基于扇出型封装结构的芯片失效位置定位方法

制造/封装

描述

徐健 孙悦 孙鹏 胡文华

(华进半导体封装先导技术研发中心有限公司 荷兰代尔夫特理工大学)

摘要:

基于可靠性试验所用的菊花链测试结构,对所设计的扇出型封装结构进行了完整的菊花链芯片制造及后道组装工艺制造,并对不同批次、不同工艺参数条件下的封装样品进行电学测试表征、可靠性测试和失效样品分析。通过菊花链设计结构及超声波扫描显微镜 (SAM) 等工具,对失效样品进行失效定位分析,并通过扫描电子显微镜 (SEM) 和能量色散 X 射线光谱仪(EDX) 等失效分析工具进行失效分析。通过对不同批次的样品进行通断电测试、可靠性预处理、可靠性试验和失效分析,总结不同工艺方法对封装整体结构翘曲、芯片偏移、金属层分层等失效模式的影响。为晶圆扇出型封装的整体封装结构设计、工艺流程搭建、封装材料选择等工作提供了指导意见。

0 引言

扇出型封装具有布线密度高、引脚间距小、封装厚度薄和高频传输损耗小等优势,近年来已逐渐发展成为封装主流技术,但是,扇出形封装也面临着很多技术问题亟待解决。

扇出型封装技术主要面临着两项关键工艺挑战: 翘曲和芯片偏移。在扇出型封装中,如果塑封工艺、重布线层 (redistribution layer,RDL) 工艺以及焊球工艺等任何一项工艺出现问题,都会导致整个芯片封装发生物理或化学失效。

翘曲问题主要是由于不同材料间的热膨胀系数不匹配造成的。芯片的保护材料以环氧树脂类材料为主,在温度变化时会发生膨胀和收缩,当和其他材料热膨胀系数失配时,接触界面会发生分层或者断裂等失效问题。对于翘曲问题,很多学者和机构做过相关研究。一种方法是从工艺和结构设计的角度出发,重点是围绕着环氧塑封料 (epoxy mold-ing compound,EMC) 的内部结构来研究的,通过在 EMC 内部添加一些金属支撑结构来改善整体的应力分布。如 Y. Lin 等人在 EMC 周围通过印刷、电镀和涂覆等工艺形成一层热膨胀系数小于 EMC的材料,这种处理方式能够通过具有较小的热膨胀系数值的材料控制晶圆的翘曲程度,或者在 EMC之间通过金属化工艺形成垂直的金属结构。金属结构能够缓解 EMC 之间的应力,减轻翘曲程度。另外,F. Z. Hou 等人通过热学和力学相结合的方法进行仿真,从材料匹配、工艺优化及设备调试方面解决这一问题。

芯片偏移是指在贴片、塑封等过程中,由于材料特性、设备精度、工艺参数等因素使芯片偏离原设计位置。在如何解决芯片偏移问题,有很多学者和机构做过一些研究,Y. Lin 等人采用凹凸结构的凸点制作,避免芯片偏移。而 C. Bishop 等人采用中间工艺表征的方法来预判断芯片偏移。本文采用芯片贴片补偿的方案解决芯片偏移问题,并通过一系列的可靠性试验进行验证,为高可靠性的扇出型封装解决方案提供了设计指导。

1 扇出型封装可靠性测试结构设计

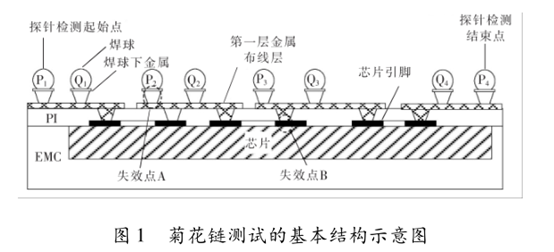

基于扇出型封装的结构特点以及菊花链的测试原理,针对扇出型封装的可靠性测试设计了菊花链测试链路。设计该链路的目的是用来反映待测封装产品的可靠性,如果链路发现失效,能够依据测试结果对失效位置进行定位,再进行后续的失效分析。测试链路的基本结构如图 1 所示。其中,金属层之间采用聚酰亚胺 (polyimide,PI) 材料。

图 1 中不同下标的 P 点和 Q 点分别代表不同的焊球,直流电阻测试探针可以通过测量两个焊球之间的阻值来判断链路是否导通。根据对扇出型封装结构的分析,A 点和 B 点是代表结构中两类可能失效的位置。其中,A 点指的是包括焊球与沉积凸点下金属层 (under ball metal,UBM) 连接位置以及 UBM 与第一层 RDL 连接位置,B 点指的是芯片的引脚与引脚上的过孔连接的位置。

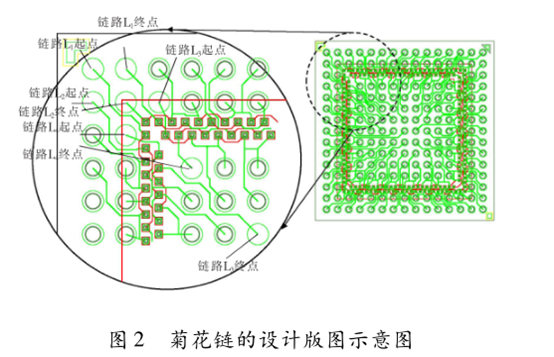

基于菊花链可靠性测试原理,设计的菊花链测试结构的版图如图 2 所示,其中扇出型封装尺寸为8 mm × 8 mm,芯片尺寸为 6 mm ×6 mm。

对应的测试链路信息如图 2 所示。版图中有 4条测试链路,即 L 1 ,L 2 ,L 3 和 L 4 ,一条链路的两个端子由起点焊球和终点焊球构成。链路上任何一处互连结构的横截面积、电阻率以及互连线的长度发生变化,都会引起电阻值的变化,但变化的幅度有所不同,因此通过 4 条链路的电阻值 R L 1 ,R L 2 ,R L 3 和 R L 4 的变化情况能够反映封装可靠性。

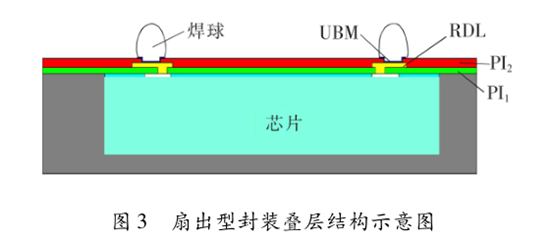

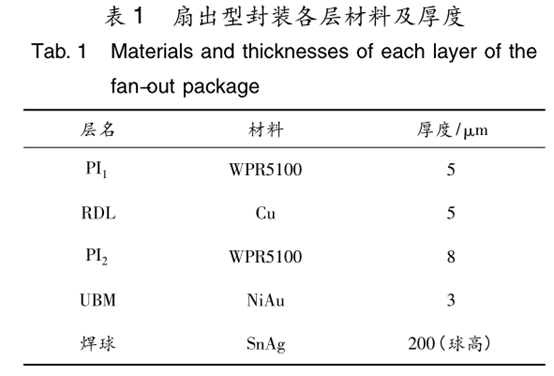

扇出封装采用传统嵌入式晶圆级球栅阵列(embedded wafer level BGA,EWLB) 封装方案,采用单层金属布线,封装层叠结构如图 3,各层的厚度信息如表 1 所示。

2 第一批次芯片可靠性验证及失效分析

菊花链的失效值规定依照标准各有不同,暂无统一标准。但是有两点标准是明确的,一是随着电路阻值增大,产品越接近失效。二是当菊花链断开时,电阻值趋向无穷大,必然导致失效。

由于行业缺乏评判标准,本文采用功能公司内部的标准进行失效评判,将通断测试的失效标准规定为 15 Ω。试验准备了两个批次的菊花链芯片,其中,第一批次芯片为 850 颗,采用开/短路的测试方法判断可靠性。在对第一批次芯片失效问题改善的基础上,进行第二批次芯片加工制造,取 240颗芯片,以链路的实际阻值大小是否超过 15 Ω 为标准判断失效情况。

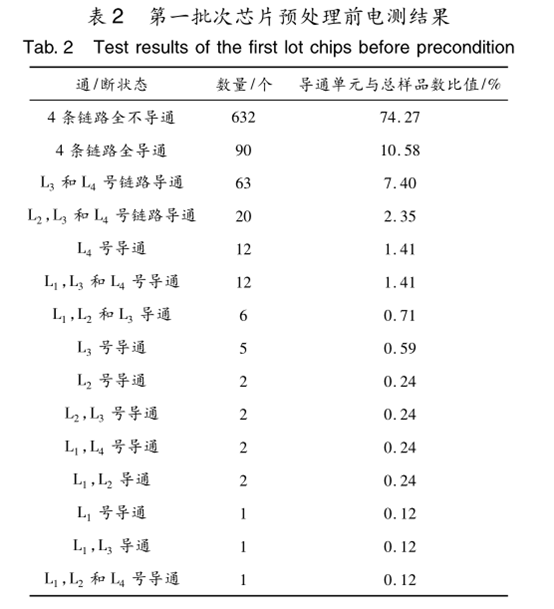

2. 1 第一批次芯片的电测试验

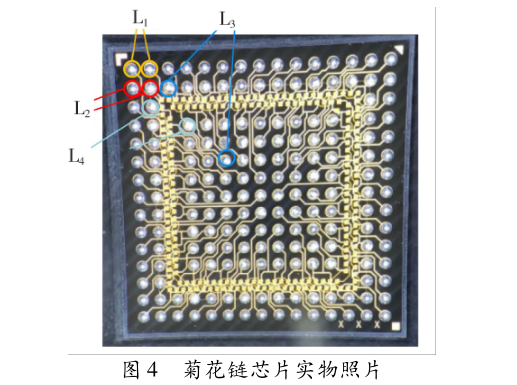

第一批次芯片的电测试验以通断测试为标准。最终封装实物及链路端口如图 4 所示。本方案采用 JEDEC MSL3 的预处理标准。在预处理试验之前进行第一次电性测量,预处理试验后重新进行第二次测量,分析两次测试之间的差异,用以评判封装的可靠性。采用万用表的蜂鸣档作为测试设备。表 2 统计了第一次电测的结果。

由测试结果可以看出,由于封装翘曲及芯片偏移的因素,L 1 ~ L 4 的 4 条链路完全导通的芯片数量较少,只占总数的 10%。但是 L 4 号链路导通的所有芯片的数量为 200 颗,因此决定以 4 条链路中的 L 4 链路的通断,作为判断芯片电测是否通过的依据。

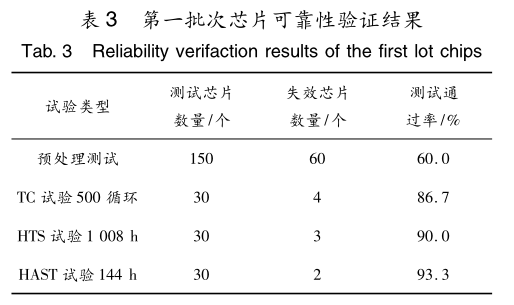

选择 150 颗已知 L 4 链路导通的芯片进行 MSL3预处理试验后,进行第 2 次电测。第 2 电测后 L 4链路导通的芯片为 90 颗,有 60 颗失效,接着进行预处理试验。经过预处理测试后,将未失效的 90颗芯片分三类,每类 30 颗,分别进行了温度循环(TC) 试验 500 循环,高温存储 ( HTS) 试验1 008 h和高压加速寿命 (HAST) 试验144 h 试验。测试结果如表 3 所示。

从表 3 可以看到,测试通过率高低与不同试验项目所施加的应力大小有直接关系,试验应力越大,失效芯片比例越大,测试通过率就越低。

2. 2 第一批次芯片的失效分析

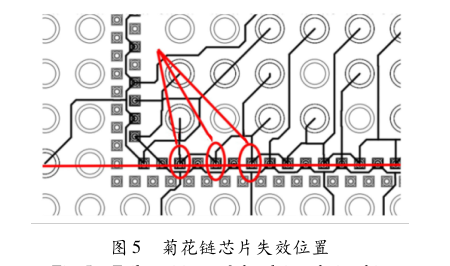

基于菊花链定位失效位置的原理,对电测失效芯片的失效位置进行定位以及相应的失效分析。在本次试验中,主要是对失效的截面和表面进行观察,以及对关键部分进行能谱分析 (EDS)。

2. 2. 1 预处理试验后的失效分析

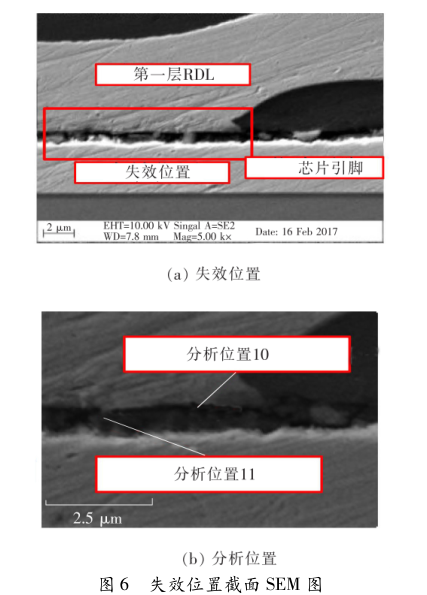

预处理试验后,确定芯片的失效位置如图 5,失效位置的截面扫描电子显微镜 (SEM) 结果如图 6。根据观察到的截面 SEM 图可知,由于芯片引脚和第一层互连线之间存在类似断裂的情况,导致导体之间产生断层,引起链路断路。为了确定失效原因,对断裂层进行 EDS 能谱分析。图 7 是采用能谱仪对断裂部分的分析结果。能谱分析结果显示,位置 10 和位置 11 的主要成分是碳元素,因此,确定在RDL 和芯片引脚之间产生了断裂部分。根据所采用的扇出型封装流程,初步判断为 PI 层在进行完开口处理后,金属表面任然留有残余 PI材料。

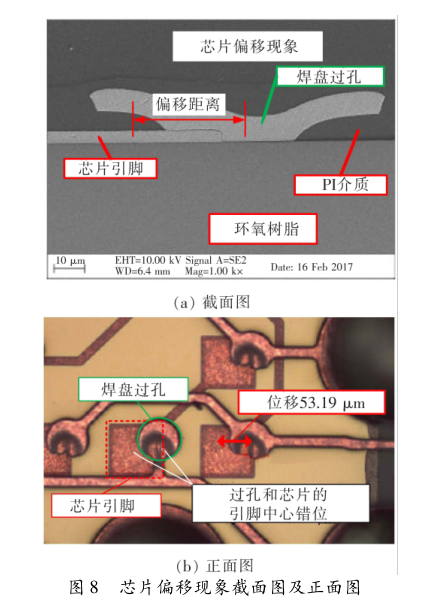

在第一批次试验中,还出现了芯片偏移问题,芯片偏移的截面图和正面图如图 8 所示。由图 8(a) 和 (b) 中可以看出,正常没有芯片偏移的情况时,过孔的位置是按照预先设计的晶圆版图布置,芯片引脚的中心是和过孔的中心重合的。由于晶圆封装各个材料的热膨胀系数不匹配,产生材料涨缩,发生翘曲,从而影响芯片位置。初步判断为贴片精度与材料涨缩所影响,后期拟通过在贴片阶段预补偿的方式,最大化地减少芯片位移对RDL 的影响。

2. 2. 2 第一批次可靠性试验的失效分析

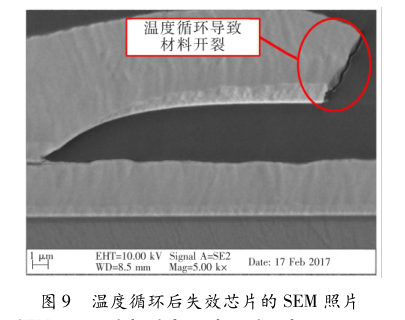

经过 TC,HTS 和 HAST 可靠性试验后,用SEM 对失效芯片进行分析,其开裂形貌照片如图 9所示。

从图 9 可以看出,介质和导体之间的连接界面虽然存在分层,但是并没有导致导体断裂,这是由于温度循环导致材料在承受高/低温冲击时产生膨胀和收缩,从而导致材料间界面开裂。因此为了能够抵抗引起界面分层的应力,需要提高界面材料的韧度和粘接强度。

在对第一批次的失效分析中认为导致链路断开的主要原因是芯片位移和导体断层。在下一批次的封装会进行相应的工艺改善。

3 第二批次芯片可靠性验证及失效分析

3. 1 第二批次芯片的电测试验

经过第一批次的可靠性测试和失效分析,针对失效问题进行了物理气相沉积 (PVD)、溅射、芯片贴片等工艺改善,进行了第二次封装流片。为了更准确地反映该结构的可靠性问题,第二次的电性测试检测了 4 条链路的实际阻值大小,采用探针台配合万用表的方式进行测试。

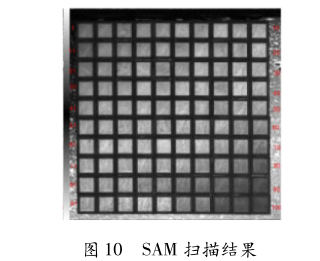

在第二批次的芯片中选择 242 颗芯片进行可靠性试验。首先进行无损超声波扫描,扫描结果如图10 所示。

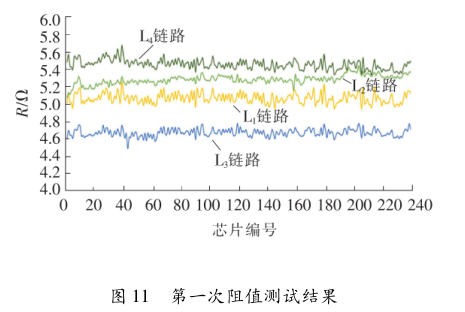

SAM 扫描结果显示未发现芯片分层。在 MSL3预处理试验之前,首先对 4 条链路的初始阻值进行测试,测试结果如图 11 所示。

由图 11 中的结果显示,L 1 链路的平均阻值约为 5. 07 Ω,L 2 链路的平均阻值约为 5. 2 Ω,L 3 链路的平均阻值约为 4. 6 Ω,L 4 链路的平均阻值约为5. 4 Ω。

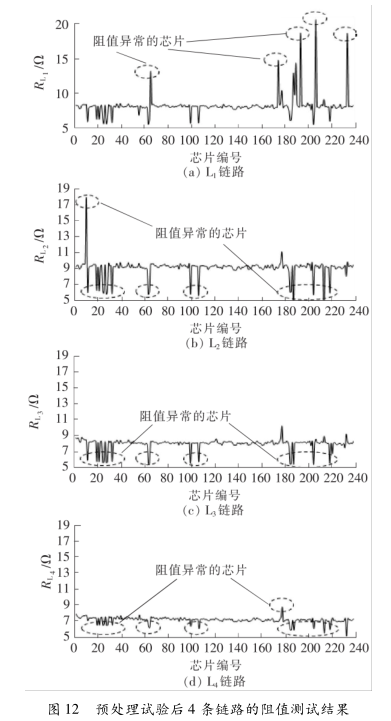

随后对这 242 颗芯片进行预处理测试,测试后芯片的 4 条链路的电阻值如图 12 所示。

根据15 Ω 的阻值失效标准,经过统计有33 颗阻值异常的芯片,其中有 6 颗芯片的阻值超过了15 Ω,判断为失效。将这些阻值异常的芯片标记后进行相应的失效分析。经过 MSL3 预处理后的芯片 4 条链路阻值的平均值分别为 8. 06,9. 3,8. 24和 7. 3 Ω。

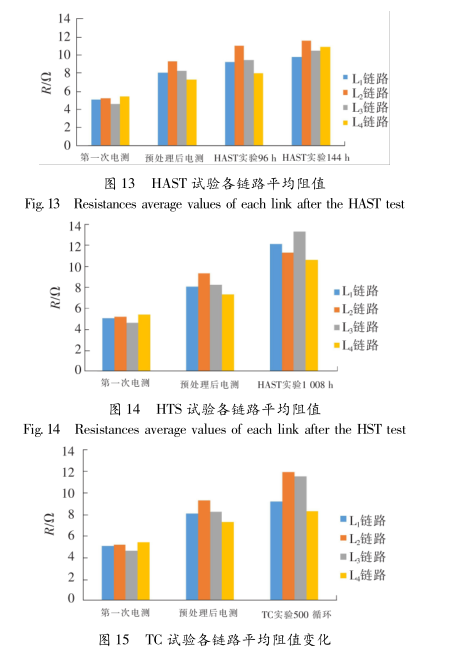

经过预处理测试后,分 3 组进行可靠性试验:第一组选择 77 颗阻值正常的芯片进行 96 h,144 h的加速老化试验; 第二组选择 46 颗阻值正常的芯片进行1 008 h 的高温存储试验; 第三组选择77 颗芯片进行 500 个循环的温度循环试验。4 条链路在每次试验前后平均阻值的对比结果如图 13 ~ 15所示。

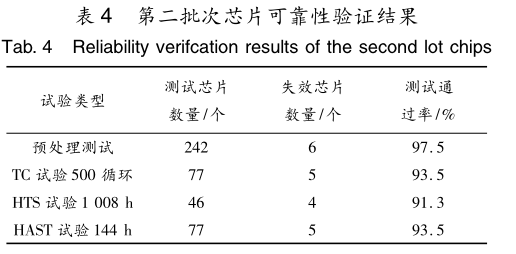

根据链路平均阻值的数据分析可知,每条链路经过预处理试验后,链路阻值都会有一定程度的上升。对于试验结果的分析如表 4 所示。

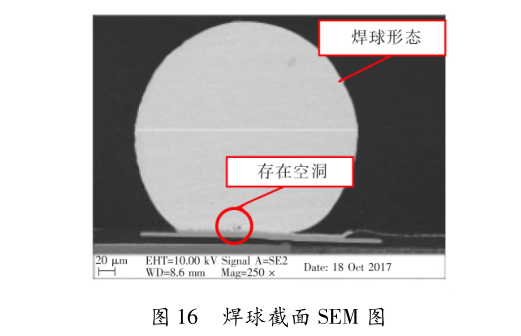

3. 2 第二批次芯片的失效分析

针对第二批次芯片封装的失效分析,主要关注阻值变化的原因和封装结构是否有缺陷。为了对比试验前后的阻值变化,首先在经过预处理试验之前,使用 SEM 设备对阻值正常的芯片的 L 2 链路的两个端子的焊球进行截面分析,SEM 照片如图16 所示。

通过对焊球的截面分析发现两个问题: 在第一批次中存在的芯片偏移问题已经解决,这是通过在贴片阶段对芯片偏移进行反向补偿的方法,对工艺进行了优化,试验结果有明显改善; 焊球和 UBM结合的金属间化合物存在空洞,而且焊球并未完全塌落,由于空洞的位置在金属间化合物 (IMC) 的晶界处,并且从焊球的形态上观察,考虑是由于助焊剂覆盖不均匀,导致回流过程中润湿性不充分,从而导致空洞的产生。

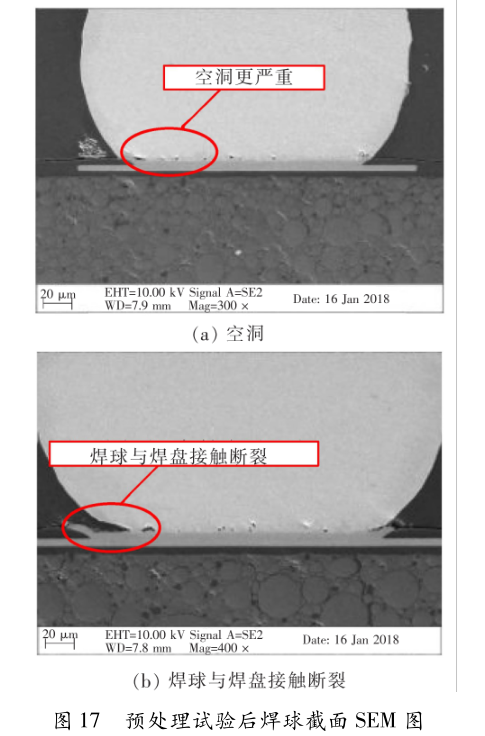

3. 2. 1 第二批预处理试验后的失效风险

经过预处理的试验后,从阻值测试结果可以看出,所有链路的平均阻值都变大。继续对经过预处理试验的芯片进行截面分析,结果如图 17 所示。

由图 17 可以看出,经过预处理试验后空洞出现得更多,并且焊球和焊盘接触的部分产生断裂。根据空洞产生的原理可知,在经历预处理 (预处理含 3 次回流) 试验的高温及回流焊测试后,焊料内晶粒长大和粗化。焊料的塑性变形导致在焊料与焊盘之间的晶界处产生微小空洞。之后,随着热循环的进行,空洞扩大并且增多,形成空洞的聚集,直至产生微裂纹,并且随着微裂纹的增多产生宏观裂纹,从而导致界面的空洞变大,对阻值的影响更大。

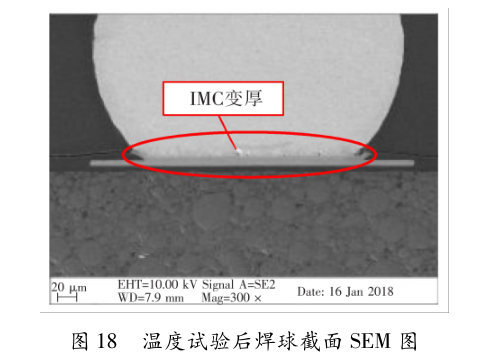

3. 2. 2 第二批次可靠性试验的失效分析

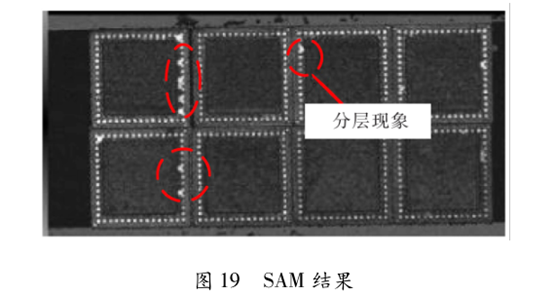

经过 HAST 试验 144 h 后,4 条链路的平均阻值上升了 5 Ω 左右。经过 TC 试验 500 个循环后,链路的平均阻值上升了约 5 Ω。经过 HTS 试验1 008 h后,阻值也上升了 5 Ω 左右。为了分析导致阻值上升的原因,对 TC 和 HTS 试验后的焊球结构和分层情况进行观察,观察到的结果如图 18所示。

由图 18 可以看出,在经过温度试验后,观察发现在焊盘和焊球之间 IMC 明显变厚,因此导致阻值变大。经过超声波扫描后,发现有几颗芯片产生了分层,观察结果的超声波扫描显微镜 (SAM)如图 19。

从超声波扫描结果可以看出,经过温度试验后,从芯片正面看进去,第二层出现分层,分层位置在 PI 和 EMC 上。虽然经过 500 个循环后,在 PI和 EMC 之间分层并没有影响到链路的通断,但后续如果继续温度循环试验,则有可能会造成更加严重的分层现象,引起RDL 的断裂。

对比两批次可靠性电测试验结果,以链路阻值超过 15 Ω 作为判断芯片失效的条件,对两个批次的可靠性验证结果分析如下: 经过对芯片偏移和导体断层的工艺问题改善后,预处理试验的电测通过率明显提高,从 60%提高到了 97. 5%; TC 试验500 个循环后,通过率从 86. 7% 提高到了 93. 5%,有一些改善。HTS 试验 1 008 h 以后,通过率从90. 0%提高到了 91. 3%,改善不明显,HAST 试验的通过率 93. 3%提高到了 93. 5%,几乎没有改善,这是由于焊球空洞和 IMC 结合不稳定等问题,在第二批次工艺仍然存在引起的。

4 结论

本文主要设计了用于封装可靠性测试的菊花链结构,研究了基于扇出型封装结构的芯片失效位置定位方法,针对芯片偏移、RDL 分层两个主要失效问题进行了相应的工艺改善。经过可靠性试验对封装的工艺进行了验证,通过菊花链的通断测试和阻值变化,对失效位置定位进行了相应的失效分析。在第二次封装流片中通过部分工艺上的改善,提高了封装的可靠性。在预处理试验后,芯片的通过率由 60% 提高到了 97. 5%,可靠性有了明显改善。

编辑:黄飞

-

芯片失效分析的方法和流程2025-02-19 2838

-

浅析扇出封装和SiP的RDL改进与工艺流程2024-04-08 5964

-

扇出型封装晶圆级封装可靠性问题与思考2024-04-07 2951

-

解析扇入型封装和扇出型封装的区别2023-11-27 17565

-

扇出型晶圆级封装技术的优势分析2023-10-25 2047

-

扇出型封装结构可靠性试验方法及验证2023-10-08 2042

-

一文详解扇出型晶圆级封装技术2023-09-25 3203

-

日月光扇出型封装结构有效提升计算性能2022-11-23 880

-

LED芯片失效分析2020-10-22 3242

-

用于扇出型晶圆级封装的铜电沉积2020-07-07 2826

-

芯片失效分析含义,失效分析方法2020-04-07 7227

-

失效分析方法---PCB失效分析2020-03-10 3850

-

元器件失效分析方法2016-12-09 8791

-

[封装失效分析系列之二] eFA:直流测试原理,I-V Curve与热定位方法2016-07-22 47198

全部0条评论

快来发表一下你的评论吧 !