浅析SiC MOS新技术:沟道电阻可降85%

描述

我们知道,SiC MOSFET现阶段最“头疼”的问题就是栅氧可靠性引发的导通电阻和阈值电压等问题,最近,日本东北大学提出了一项新的外延生长技术,据说可以将栅氧界面的缺陷降低99.5%,沟道电阻可以降低85.71%,整体SiC MOSFET损耗可以降低30%。

9月28日,东北大学和CUSIC在“ICSCRM2023”会议上宣布,他们针对SiC MOSFET开发一种“同步横向外延生长法(SLE法)”,目的是通过在4C-SiC外延层上再生长3C-SiC层,来解决高温栅氧导致的可靠性问题。

为什么需要怎么做?传统4C-SiC栅氧层制备最大的问题是温度太高(约1300℃),这会导致SiO2/SiC界面出现碳残留,导致沟道迁移率低,以及可靠性和阈值电压等缺陷。

如果通过3C-SiC来制备栅氧层,工艺问题可以低于900℃,可以完美解决这个问题。根据“行家说三代半”之前的报道,3C-SiC MOSFET的n沟道迁移率范围为100-370 cm2/V·s。而4H-SiC MOSFET通常为20-40cm2/V·s,沟槽器件为6-90 cm2/V·s,京都大学的技术可以做到131 cm2/V·s,但也比3C-SiC MOSFET低3倍左右。

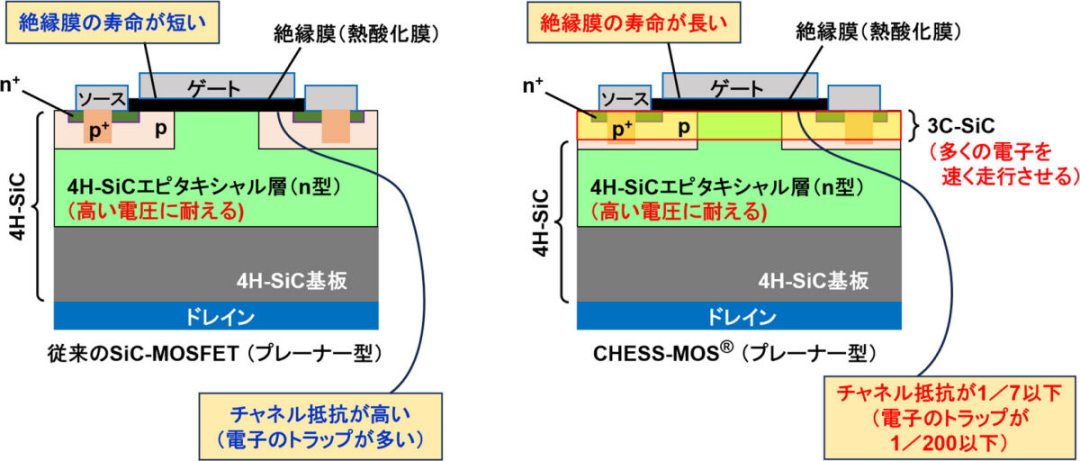

东北大学根据这思路制备了一种CHESS-MOSFET,即在4C-SiC叠加3C-SiC层,如下图:

采用4H-SiC外延层的MOSFET(左),CHESS-MOS(右)

该研究团队表示,CUSIC 设计的“CHESS-MOS”能够同时降低功率损耗并确保长期可靠性。

该器件的特点是采用了混合外延层,既利用了3C-SiC的高迁移率,也利用了4H-SiC层的高耐压。

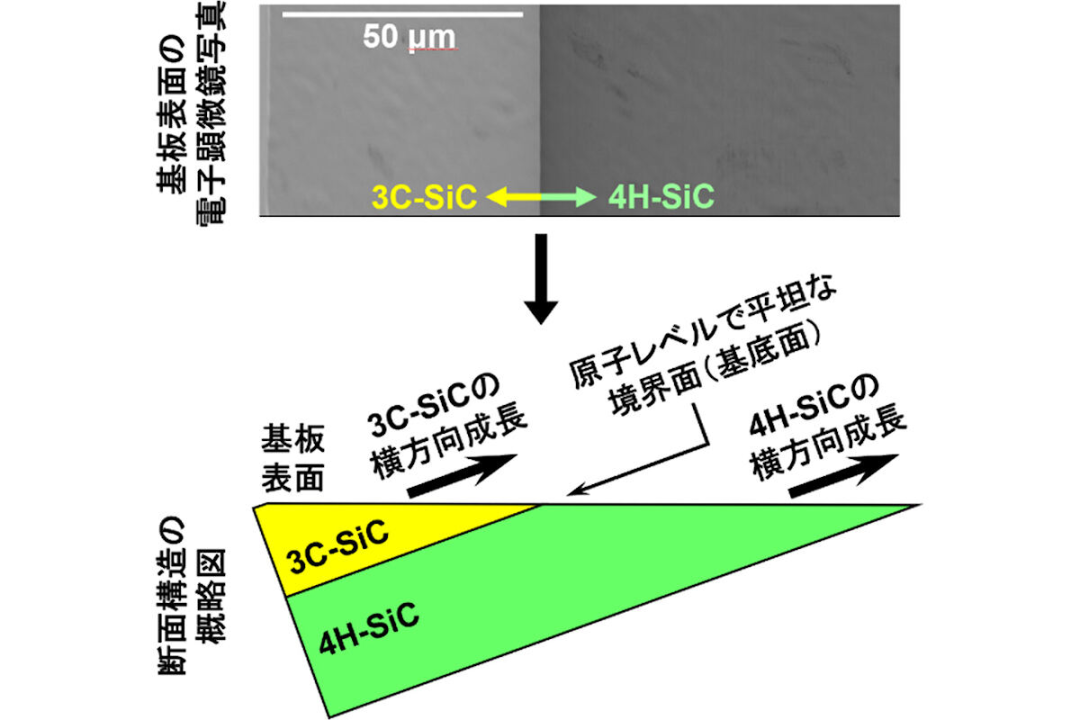

然而,要实现这一目标需要开发新的外延和晶体生长技术,以无缝堆叠两种不同晶格SiC层。因此,该研究团队开发了SLE方法。

简单来说,SLE方法是在4H-SiC的延伸基面上生长3C-SiC层,3C-SiC也沿着4H-SiC基面延伸,这样使得3C-SiC层与4H-SiC层之间的界面非常平坦,没有原子偏差。

扫描非线性介电常数显微镜测量结果显示,3C-SiC表面的缺陷密度仅为4H-SiC的1/200,表明SLE方法可以大幅降低界面缺陷密度,预测CHESS-MOS可将损耗降低30%以上。

而且,由于基于3C-SiC的CHESS-MOS还可以极大地降低绝缘膜漏电流密度,消除绝缘膜在短时间内劣化的风险,提高器件的长期可靠性。

在实验中,该团队还发现,使用SLE法可以形成3C-SiC/4H-SiC/3C-SiC/4H-SiC等双量子阱结构的现象,那么通过有意地形成这种堆叠结构,可以制造高频器件,而在以前,SiC半导体器件被认为难以实现。

此外,该团队还有另一个新发现,他们通过使用SLE方法在半绝缘4H-SiC衬底上生长3C-SiC层,可避免由于与衬底电容耦合而导致的高频信号衰减问题,这将有望为高频集成电路的大规模生产铺平道路。

最为重要的是,SLE方法能够直接在SiC外延层表面的一部分引入不同的晶体结构,而无需大幅改变现有的SiC MOSFET器件形状或制造工艺,预计该技术很快可以导入器件生产线。

审核编辑:刘清

-

国产碳化硅MOS基于车载OBC与充电桩新技术2022-06-20 12999

-

浅析降低高压MOS管导通电阻的原理与方法2018-11-01 5276

-

SiC-MOSFET有什么优点2019-04-09 4691

-

SiC功率器件SiC-MOSFET的特点2019-05-07 5701

-

浅析SiC-MOSFET2019-09-17 6420

-

SL407-60V15A93毫欧P沟道MOS管可替换AOD4072020-06-01 527

-

SL444替代SL444MOS管N沟道60V20A50毫欧2020-06-03 768

-

SL2060场效应管 20V85A N沟道功率MOS管2020-06-13 805

-

供应SL3402 N沟道MOS管,30V4A50MΩ内阻替代AO34022020-07-02 1281

-

SL3403 -30V -3.5A贴片MOS管 P沟道 替代AO34032020-08-01 923

-

30A 30A P沟道 MOS管 30P032021-03-30 1009

-

SLN30N03T 30V 30A N沟道 MOS2021-04-07 1617

-

基于深亚微米MOS器件沟道的热噪声浅析2009-12-15 775

-

浅析MOS管介绍与应用2021-11-13 1592

-

SiC MOS卓越性能的材料本源2024-09-23 1812

全部0条评论

快来发表一下你的评论吧 !