从可综合的RTL代码的角度聊聊interface

描述

SystemVerilog引入了interface,这里我们从可综合的RTL代码的角度聊聊interface。

什么是interface?

Interface是将一系列信号封装为一个模块,这里的“一系列信号”通常是彼此相关的,比如AXI接口协议之一的AXI4-Stream的TLAST/TVALID/TREADY/TDATA,这个“模块”称为接口模块。接口模块可以被实例化作为其他module的端口,从而简化了module之间以及module与TB(testbench)之间的连线操作。

使用interface的好处

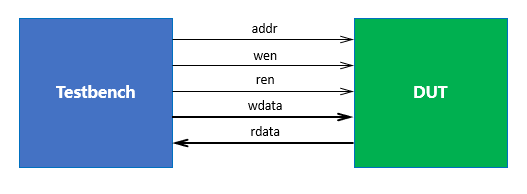

使用interface的好处也是显而易见的。我们来看个例子。如下图所示,待测模块和测试平台之间的连线包含5个信号,采用此方法就要在DUT module内定义5个端口,在TB内定义对应的5个信号。

如果采用interface就会形成下图所示的连接方式。这样无论是DUT还是TB只需要在自身模块内实例化这个interface即可。

可见,使用interface会带来这样几个好处:

(1)module之间的连线由输入/输出列表替换为interface,不易出错

(2)如果需要更新module的输入/输出端口,只用在interface里进行一次更新,而不必在相关module的端口处进行多次更新

其他好处跟UVM相关,这里先不做阐述。

接口的定义

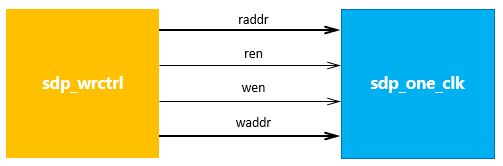

我们从可综合RTL代码的角度看个例子,如下图所示的两个模块,一个是控制模块,一个是存储模块,控制模块生成相应的控制信号给存储模块。

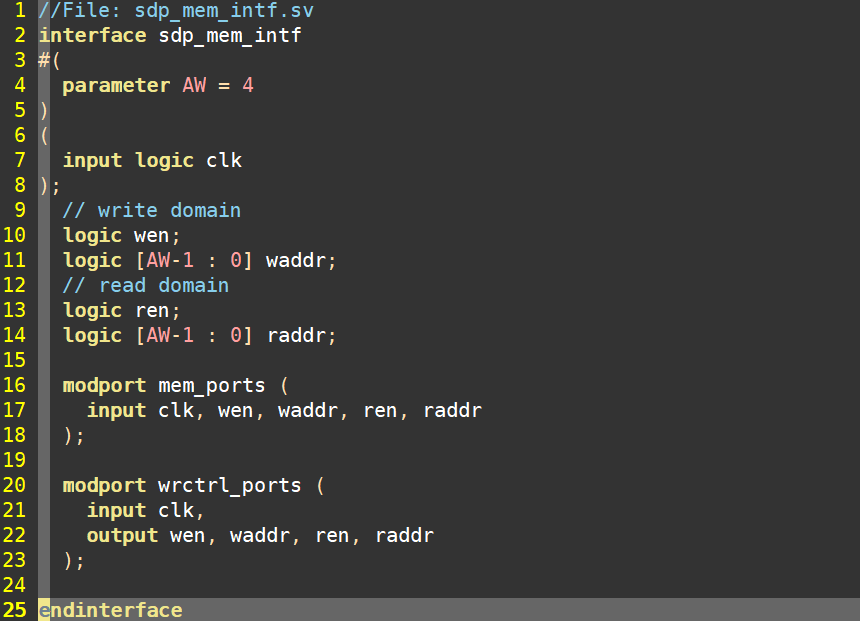

我们使用interface定义这组信号,如下图所示代码。从这段代码可以看到,接口模块以interface作为关键字开始,以endinterface结束(像不像module,endmodule)。Interface可以参数化,如代码的4行所示,可以有输入/输出或双向端口如代码第7行所示。代码第10行和第11行定义了写方向的控制信号,第13行和14行定义了读方向的控制信号。第16行modport(端口模块)用来定义信号方向。对存储模块而言,这些信号都是输入信号,对控制模块而言,除时钟外其他信号均为输出信号。

因为只是定义信号的方向,所以只用列出信号名称而无需指定信号的位宽。同时,同方向的信号可列在同一行,如代码第17行所示。如果信号方向声明的结尾也是modport的结尾,那么该结尾没有任何额外标点符号,如代码第22行的结尾,如果信号方向声明的结尾不是modeport的结尾,那么结尾就用逗号,如代码第21行。注意代码第10行至第14行定义的信号类型为logic,相比于Verilog里的reg,logic更灵活,不仅可以用在always进程中,也能用于assign赋值语句中(Verilog需要用wire)。

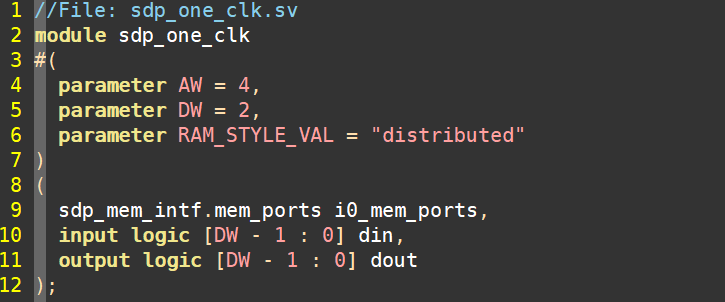

在存储模块中,可直接在端口列表内实例化该接口模块,如下图所示代码片段第9行,实例化方式和模块的实例化方式一样,需要注意的是这里不能指定interface内的parameter,其余输入/输出端口不在接口模块内的可单独声明,如代码第10行和第11行所示。

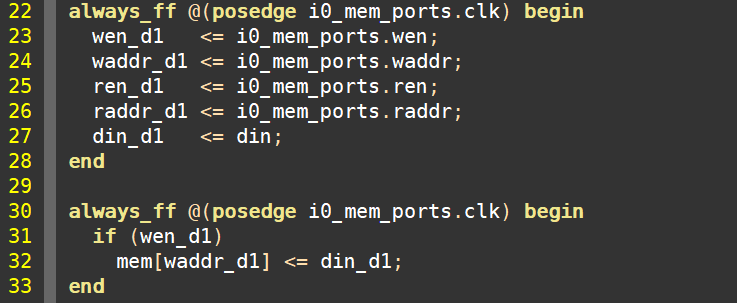

在模块内部使用interface内声明的接口,需要采用如下图所示代码片段的方式,如代码第23行,通过i0_mem_ports.wen使用写使能信号。因为代码内部可能会反复使用interface内的信号,所以interface的名字尽量短一些。

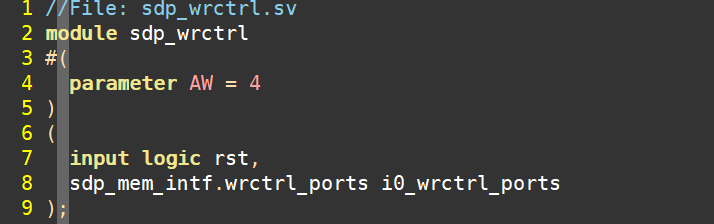

同样地,在控制模块内可直接实例化上述定义的interface,如下图所示代码片段。

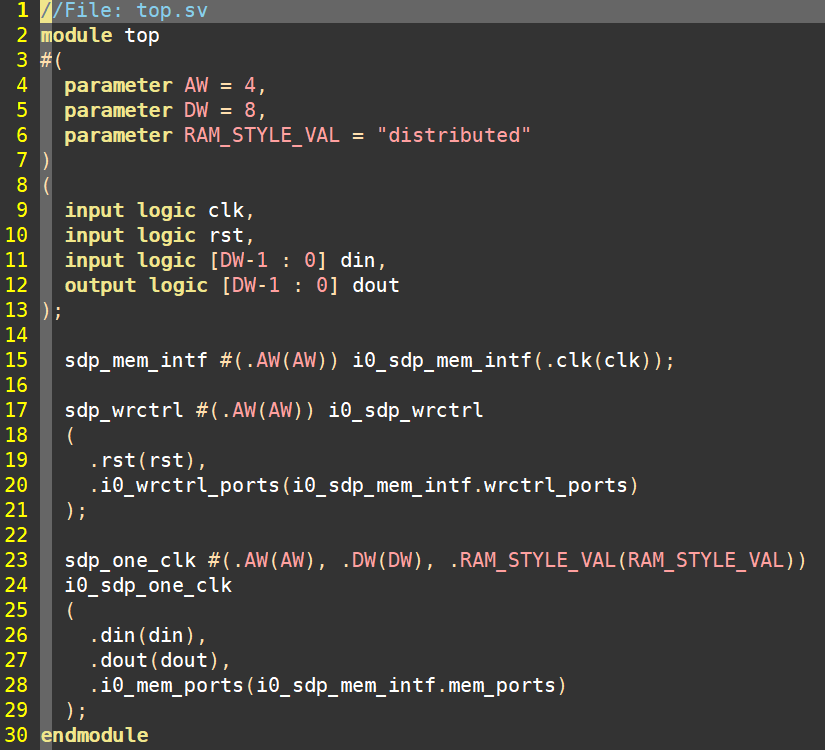

在设计的顶层,需要依次实例化接口、存储模块和控制模块。此时,就需要对接口的parameter进行设定,如下图所示代码片段的第15行所示。

传统的输入/输出列表方式存在这样几个不足之处:

(1)需要在相关模块中反复声明输入/输出信号

(2)存在不同模块端口不匹配的风险

(3)设计规格的更改会导致需要在相关多个模块中进行输入/输出信号的更新

这种重复性的更新不仅涉及到很多行代码,还会存在信号名称写错或者信号位宽写错的风险。

注意:module端口声明若采用input/output/inout这种形式,实例化时这些端口是可以悬空的,但如果采用interface,实例化的interface是不允许处于未连接的状态。

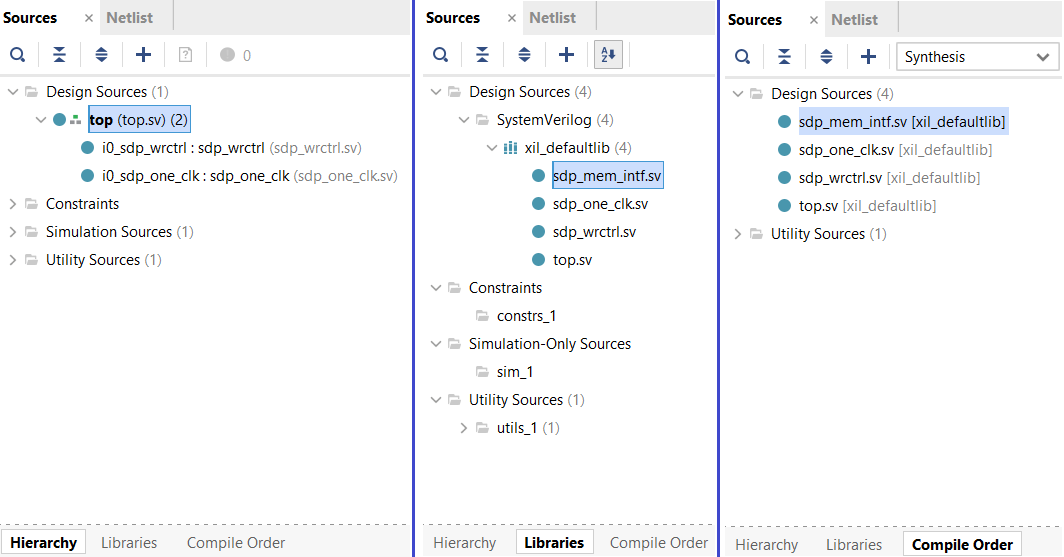

Vivado对interface是支持的。将上述4个文件直接添加到Vivado中,如下图所示。在Hierarchy窗口中,可以看到top下面只有控制模块和存储模块,而没有接口模块,因为接口并不是一个module。在Libraries下则可以看到接口模块。在Compile Order窗口下,可以看到工具会先编译接口模块,再编译其他模块。

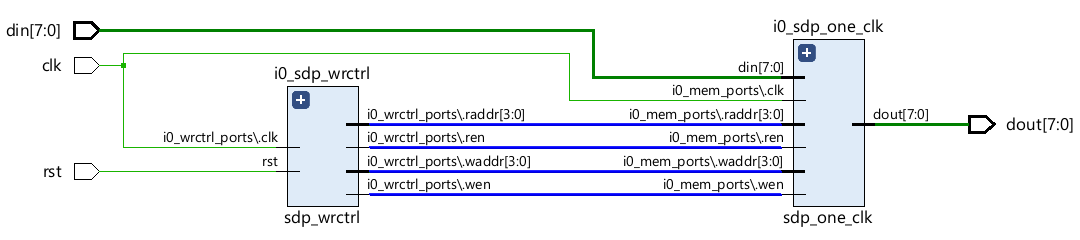

Vivado下打开Elaborated Design,可以看到interface信息,如下图中的高亮部分,工具以“接口名.信号名”的方式显示net的名字。

综上所示,SystemVerilog提供的interface支持参数化,支持信号分组(modport),在可综合的RTL代码中,可使用interface简化输入/输出列表的描述。

审核编辑:刘清

-

如何在不改变RTL代码的情况下,优化FPGA HLS设计2020-12-20 2609

-

RTL级设计的基本要素和步骤是什么2023-01-17 11570

-

RTL级代码和仿真代码的区别2012-07-21 10451

-

为什么quartus综合没有报错而modelsim rtl仿真就报错了2015-09-24 7619

-

如何理解Xilinx的RTL图2017-08-14 13018

-

来自vivado hls的RTL可以由Design Compiler进行综合吗?2020-04-13 2760

-

从架构的角度看如何写好代码 + 我的思考2020-06-18 1800

-

如何保证RTL设计与综合后网表的一致性2009-01-23 999

-

RTL8201/RTL8201BL pdf datashee2009-03-04 2177

-

设计复用的RTL指导原则2011-12-24 737

-

如何设计可综合的Verilog代码和应该遵循什么原则2019-04-20 5347

-

如何在C代码中插入寄存器?2021-02-02 4023

-

【开源硬件】从PyTorch到RTL - 基于MLIR的高层次综合技术2022-11-24 2952

-

逻辑综合与物理综合2022-11-28 3970

-

从RTL追踪到Scala2022-12-09 2030

全部0条评论

快来发表一下你的评论吧 !