SystemVerilog:处理信号双驱动问题解析

电子说

描述

1.前言

最近帮朋友搞定一个小问题,记录一下。不啰嗦,直接上结论:当某个信号出现多于一个驱动源的时候,或者某个信号是双向(inout)的时候,都需要使用wire来完成线网连接。具体用法就是声明某个信号为wire sigal_a;或者wire logic signal_a;就可以了。注意直接声明为logic signal_a;是不行的,会报类似如下的错误:xmelab: *E,ICDCBA: Illegal combination of driver and output clockvar to variable 'signal_a' detected (output clockvar found in ......).

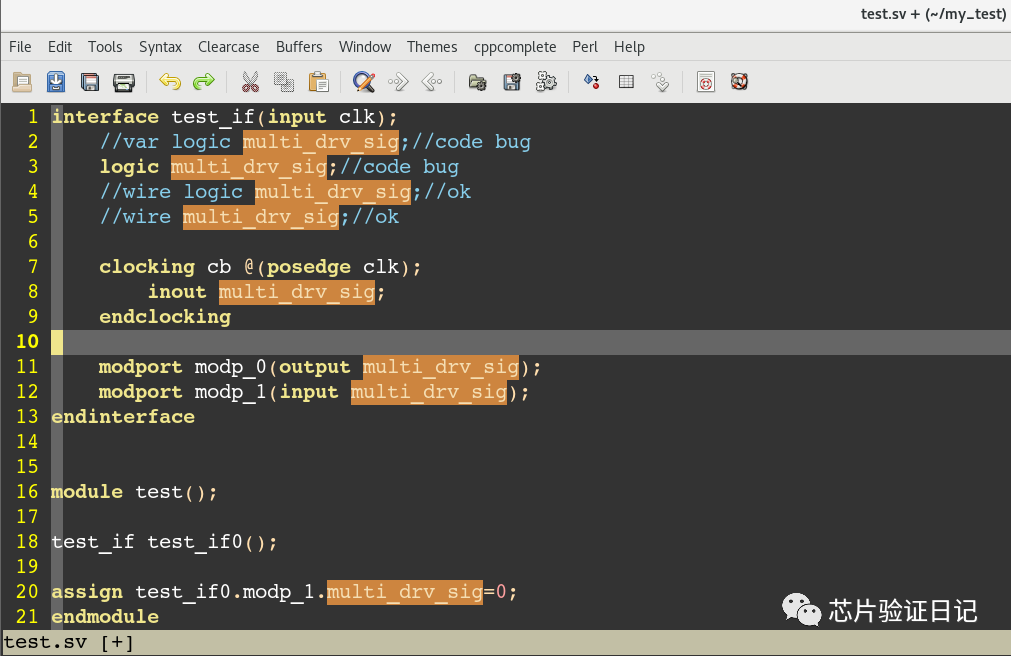

2. 实例代码

interface test_if(input clk);

//var logic multi_drv_sig;//code bug

logic multi_drv_sig;//code bug

//wire logic multi_drv_sig;//ok

//wire multi_drv_sig;//ok

clocking cb @(posedge clk);

inout multi_drv_sig;

endclocking

modport modp_0(output multi_drv_sig);

modport modp_1(input multi_drv_sig);

endinterface

module test();

test_if test_if0();

assign test_if0.modp_1.multi_drv_sig=0;

endmodule

3.Makefile脚本

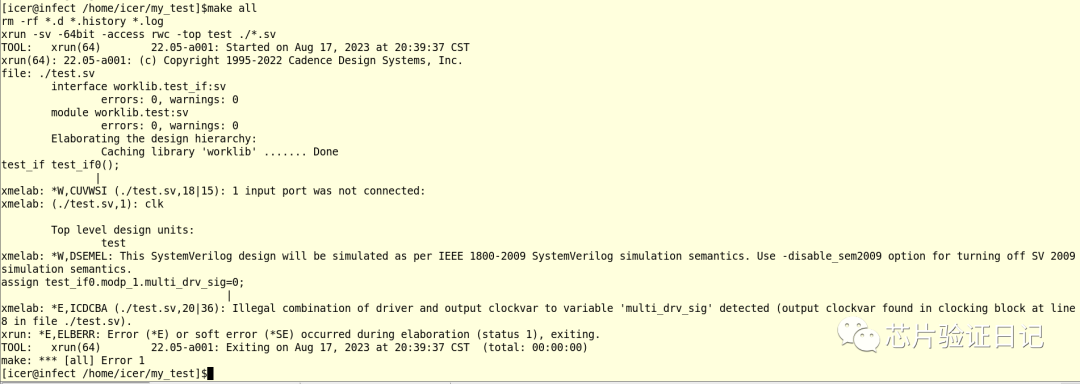

all:clean xrun -sv -64bit -access rwc -top test ./*.sv clean: rm -rf *.d *.history *.log4.仿真结果

5. 报错信息查询

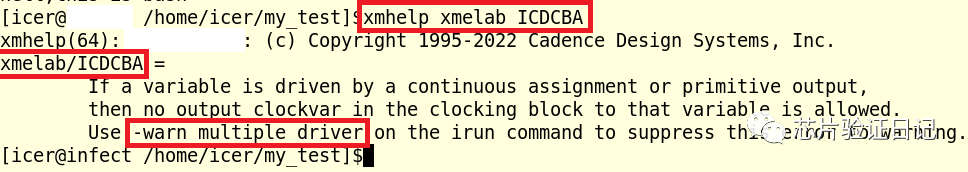

如下图所示,查询报错信息的含义,xrun甚至还给出了解决方案,通过添加工具提供的选项-warn_multiple_driver的确可以将这个*E的Error降为Warning,但是这不是问题的根源。

6. 问题的根源

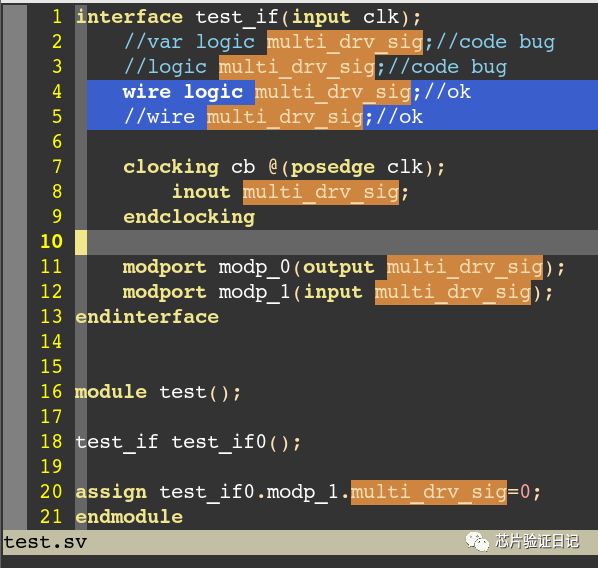

如下图所示,第4行和第5行的用法都是对的,第2行和第3行的用法都是错误的。

7. Summary & Conclusion

在SystemVerilog中,类型可以分为线网(net)和变量(variable)。线网的赋值设定与Verilog的要求相同,即线网赋值需要使用连续赋值语句(assign),而不应该出现在过程块(initial/always)中;相比于线网驱动的限制,变量(var)类型的驱动要求就没有那么多了,如logic [15:0] signal_b,该变量默认类型是var(变量),对它可以使用连续赋值或过程赋值。

简言之,可以在module中的数值存储和线网连接,多数情况下使用logic类型变量,而很少有只能使用wire的情况。那么什么时候需要使用wire类型呢?就是本文的这种scenario:当某个信号出现多于一个驱动源的时候,或者某个信号是双向(inout)的时候,都需要使用wire来完成线网连接。具体用法就是声明某个信号为wire sigal_a;或者wire logic signal_a;就可以了。

编辑:黄飞

-

RCC电路原理与设计及问题解析2009-12-14 29028

-

C语言习题解析库2015-03-11 2932

-

round robin 的 systemverilog 代码2017-03-14 3743

-

UART串口与LWIP以太网问题解析2021-08-05 1542

-

电子设计竞赛赛题解析2016-12-17 1317

-

电视卡常见问题解决方法(驱动问题等)2007-12-06 3210

-

运算放大器容性负载驱动问题2010-01-04 4300

-

自动控制原理习题解析2016-05-05 656

-

风力摆控制系统赛题解析2016-12-09 1296

-

电工学知识要点与习题解析2020-01-10 1809

-

解决高频MEMS测试驱动问题的方案是什么2020-12-08 1108

-

樊昌信《通信原理》真题解析及讲义电子版2021-09-06 1634

-

SystemVerilog里的regions以及events的调度2023-07-12 3081

-

光耦失效的几种常见问题解析2023-12-25 10152

-

USB驱动问题:设备无法识别的全面指南!2024-11-26 2442

全部0条评论

快来发表一下你的评论吧 !