"超越 MOSFET "的晶体管是否真的存在?

模拟技术

描述

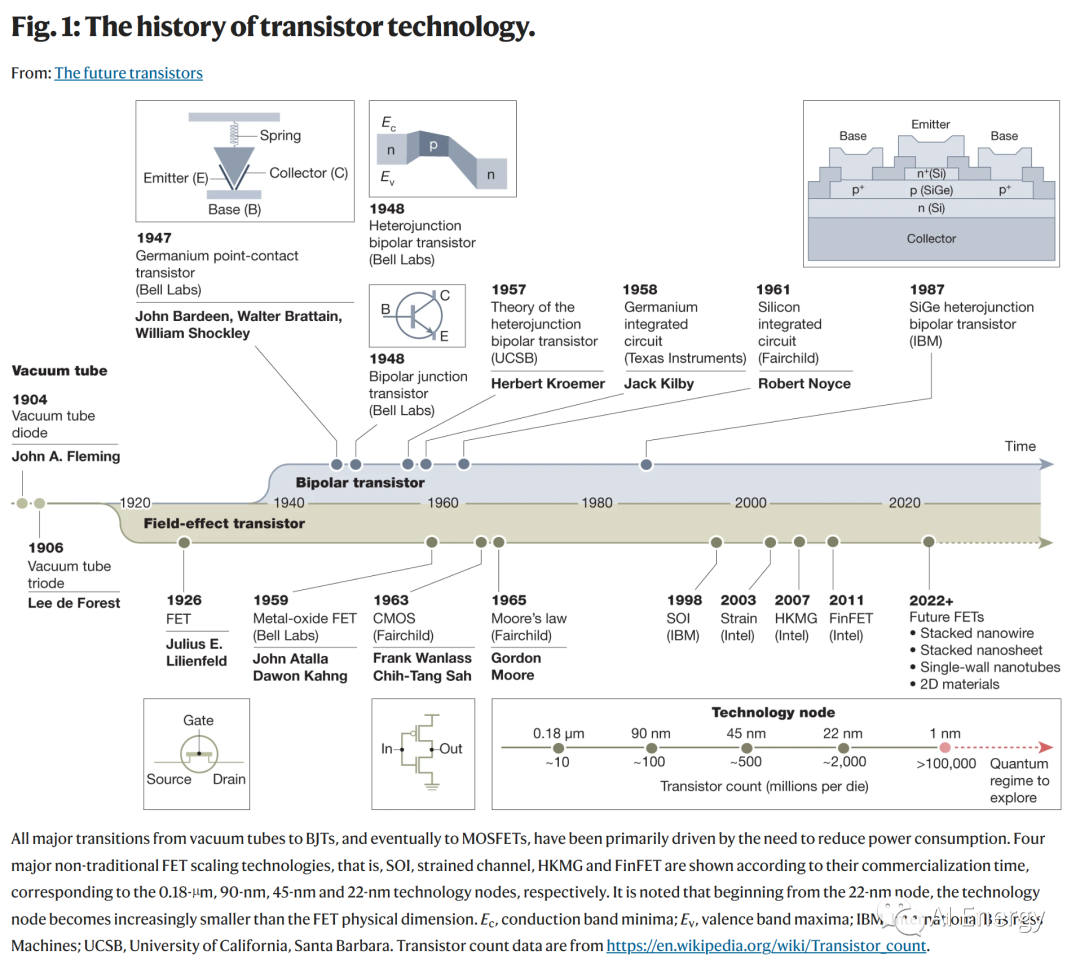

近日,美国加州大学圣塔芭芭,美国IBM研究实验室,法国格勒诺布尔大学,中国台湾台机公司,日本东京大学 ,韩国三星先进技术研究院和美国英特尔公司的研究人员在《Nature》杂志发表了一篇题为“The future transistors”的论文。

研究内容

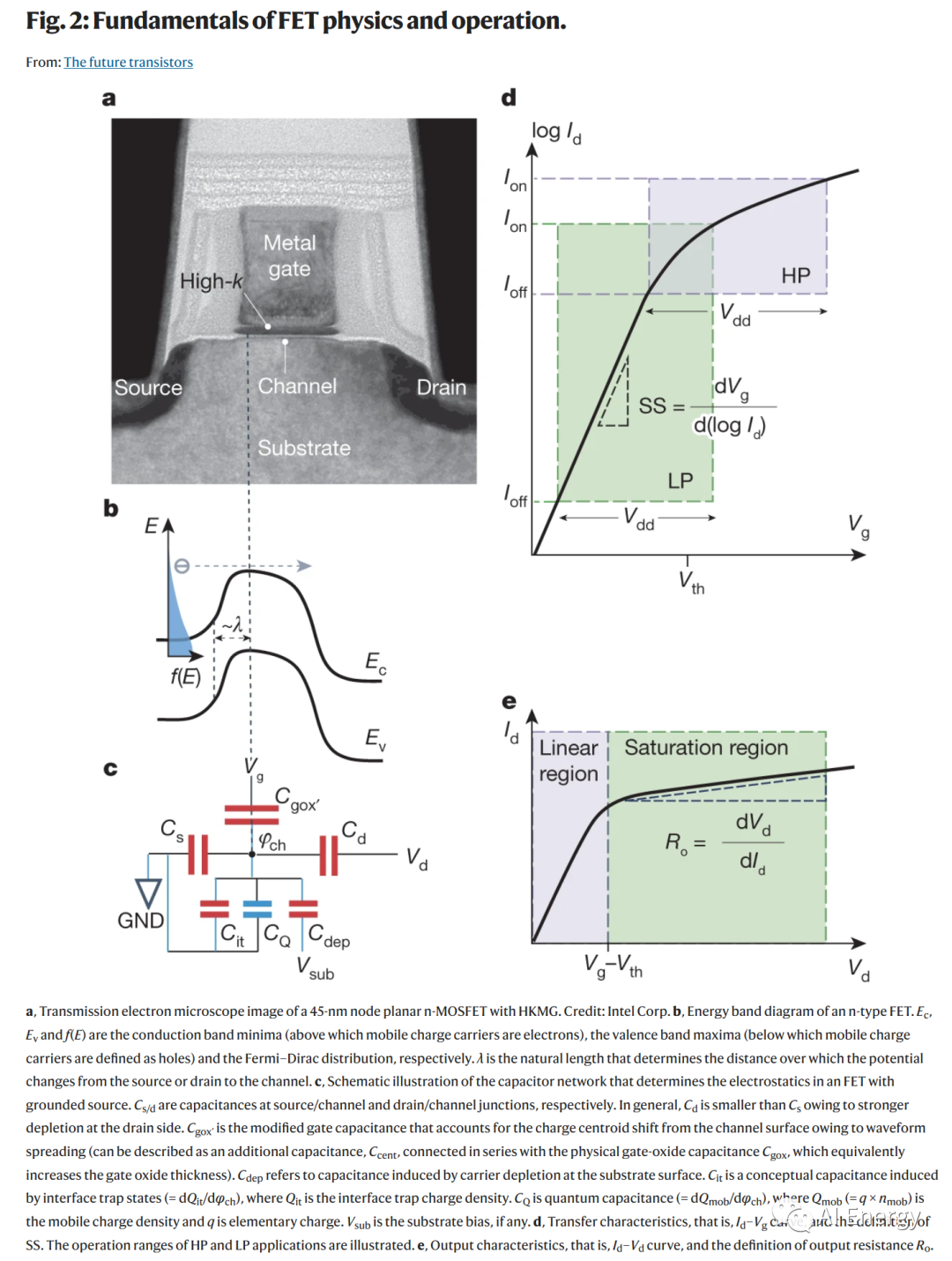

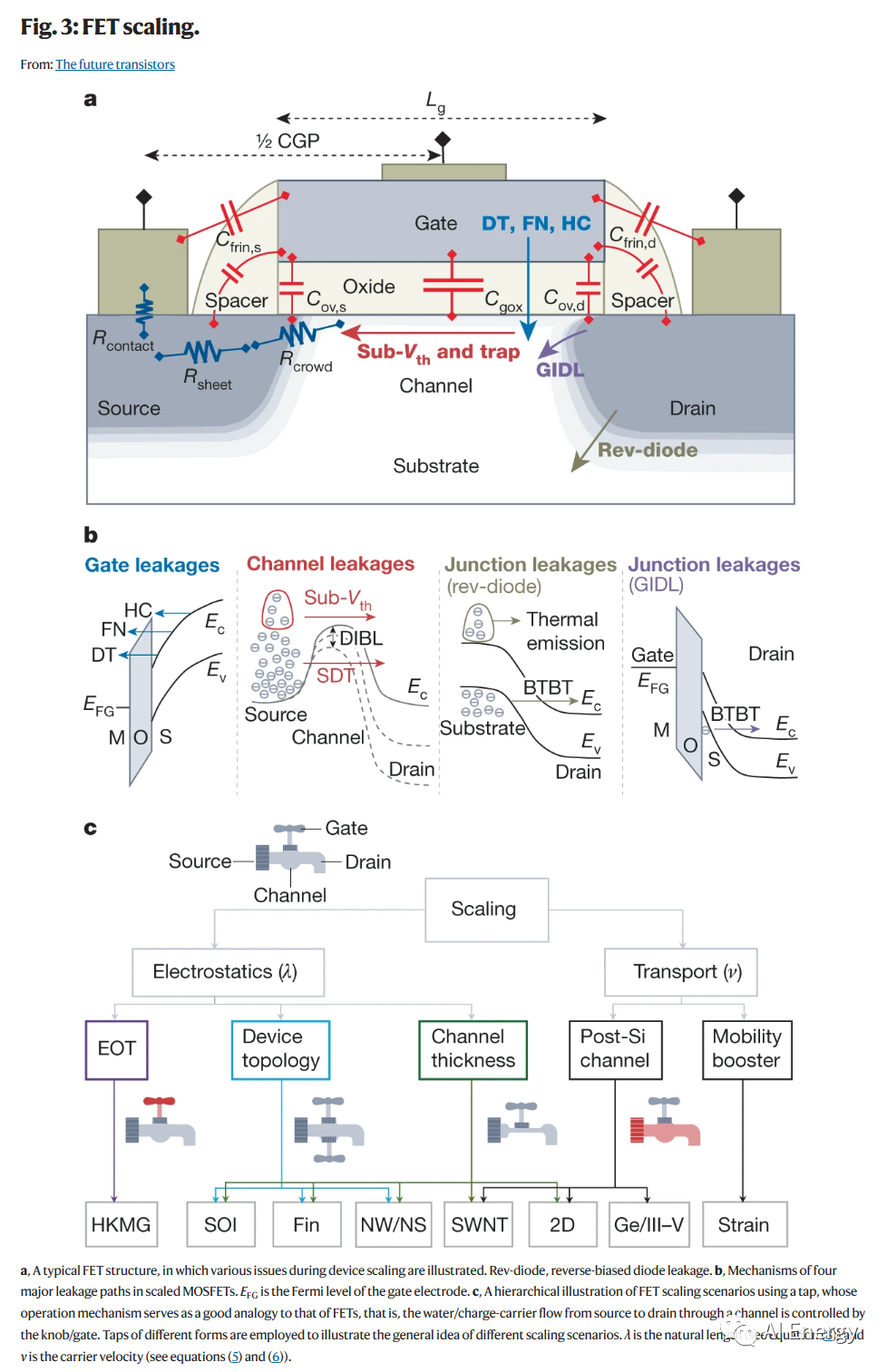

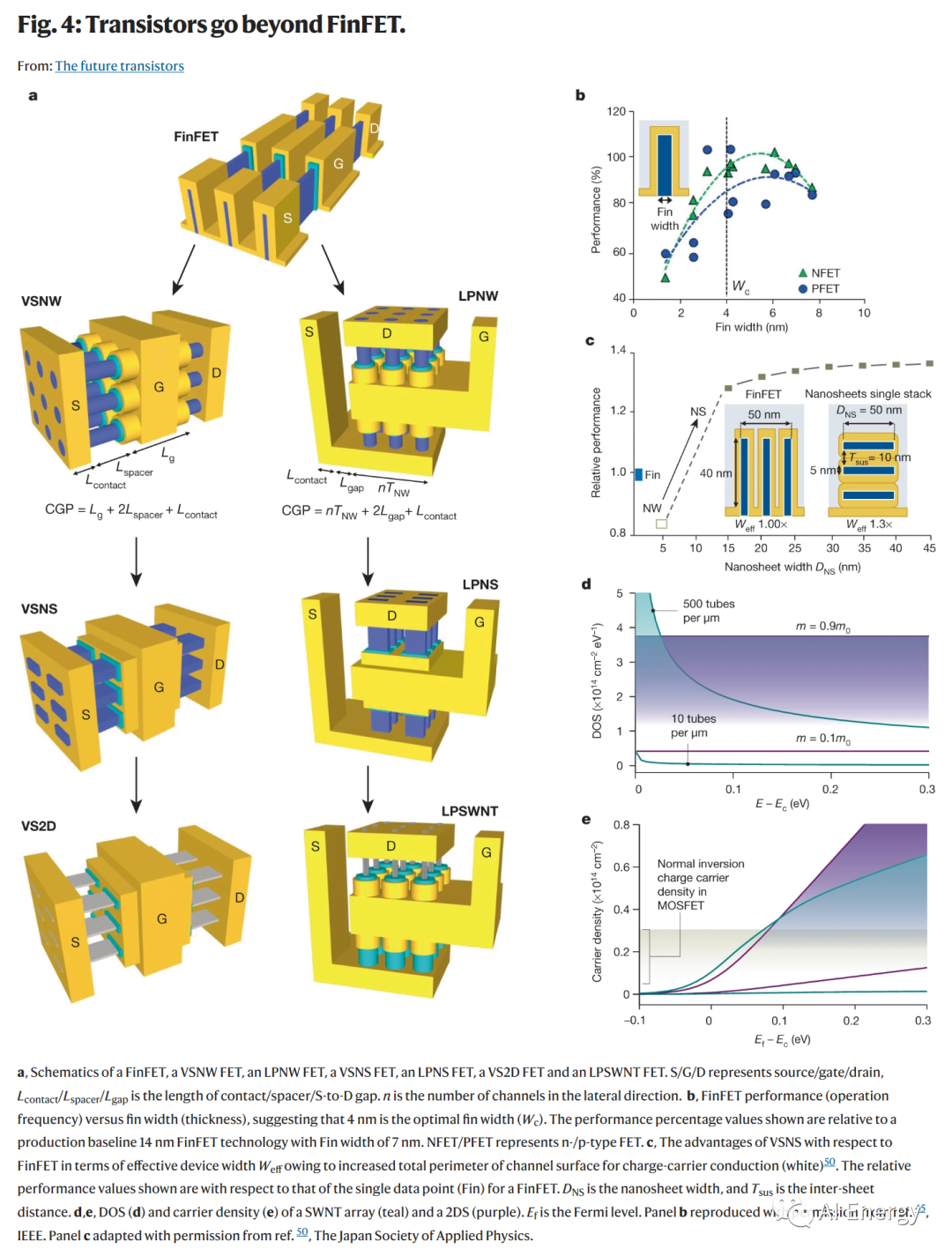

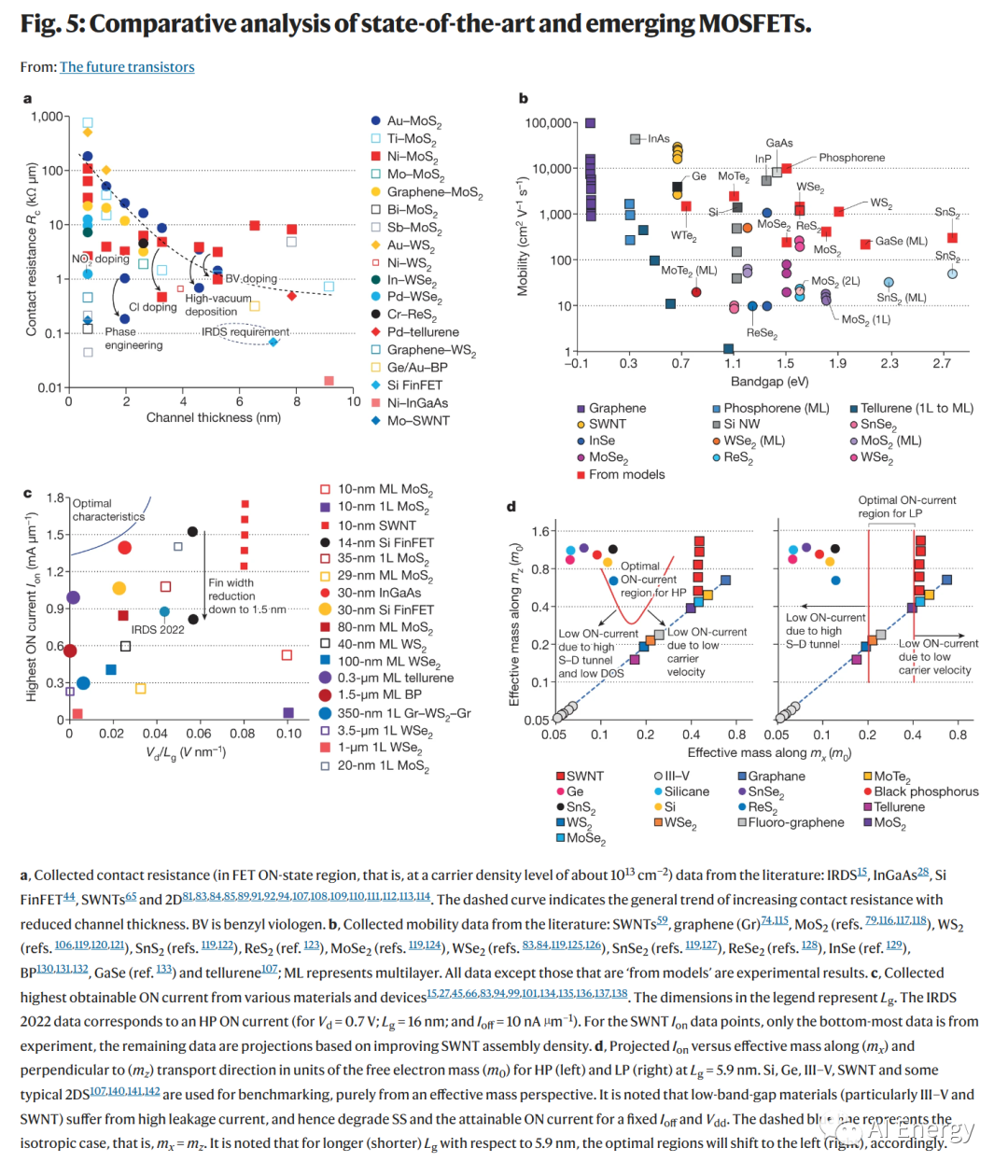

金属氧化物半导体场效应晶体管(Metal–Oxide–Semiconductor Field-Effect Transistor,MOSFET)是互补金属氧化物半导体(Complementary Metal–Oxide–Semiconductor,CMOS)技术的核心元件,是工业革命以来最重要的发明之一。在集成电路产品对更高的速度、能效和集成密度要求的推动下,过去六十年来,MOSFET的物理栅极长度已缩小到20纳米以下。然而,即使是最先进的鳍式场效应晶体管,在保持低功耗的同时缩小晶体管尺寸也越来越具有挑战性。本文对现有和未来的CMOS技术进行了全面评估,并根据为场效应晶体管缩放而建立的分层框架,讨论了设计栅极长度低于10纳米的场效应晶体管所面临的挑战和机遇。本文的评估重点是根据以往扩展工作中获得的知识,确定最有前途的10纳米以下栅极长度MOSFET,以及使晶体管适用于未来逻辑集成电路产品所需的研究工作。此外还详细介绍了对未来超越MOSFET晶体管和潜在创新机会的展望。预计晶体管技术的创新将继续在推动未来材料、器件物理和拓扑、异构纵向和横向集成以及计算技术方面发挥核心作用。

展望

超越MOSFET 的未来 “跨-电阻”

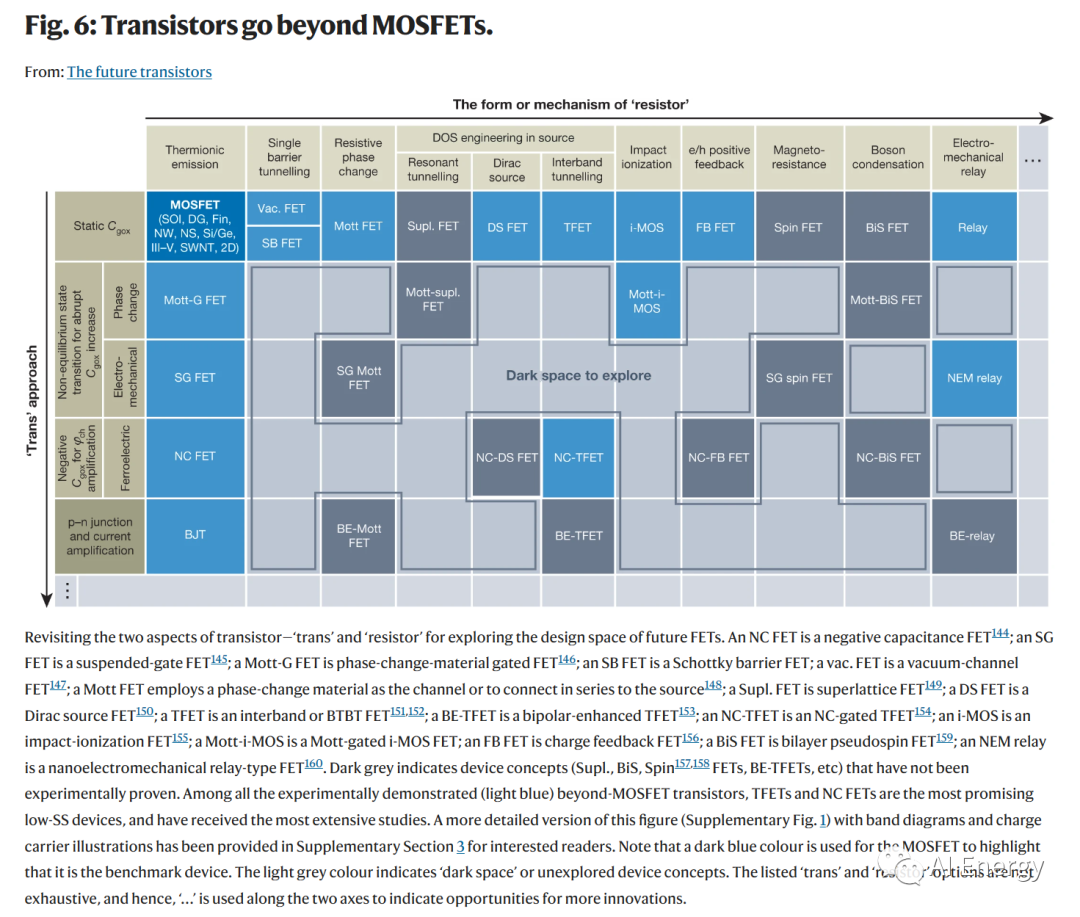

MOSFET受其工作机制的限制,因此功耗和能效无法与器件尺寸同步增长。CMOS界一直在寻找 "超越 MOSFET "的晶体管,以打破这一能效瓶颈。在这种情况下,回顾一下晶体管的基本方面--"trans"(源于 "传输 "或调制)和 "resistor"(源于沟道电阻)--是很有启发性的。因此,"晶体管 "捕捉到的是操纵信息状态或载体的方法,也就是 "电阻"。对于商业化的 MOSFET 和 BJT,"跨 "分别是通过静态栅电容和 p-n 结势垒调制的电场效应实现的,而 "阻 "则是通过这两种器件在势垒上的热释电形式实现的。为了在这两个方面中的一个(或两个)方面进行创新,人们做出了许多努力。

负电容 (NC)、悬浮栅 (SG) 和莫特相变材料门控 (Mott-G)场效应晶体管(图 6)等各种 "反式 "方法已被提出并进行了实验探索。NC FETs利用铁电材料的负电容状态来构建负Cgox,目的是克服栅极效率的统一上限。SG和 Mott-G FETs 在栅极堆栈中分别引入了纳米机电开关和绝缘体-金属相变存储单元,并利用其非平衡态开关瞬态来实现 Cgox的突然增加(相对于栅极电压),从而转化为电荷密度和漏极电流的突然增加,即超小型 SS。值得一提的是,NEM 开关和相变存储单元的存储特性不可避免地会在传输特性中产生存储效应,即滞后,这就限制了 SG 和 Mott-G FETs 在存储方面的应用。 相比之下,"电阻 "已在许多超越热释电的形式和机制中得以实现。

在肖特基势垒和真空场效应晶体管中,电荷载流子分别通过金属源和半导体或真空沟道之间的肖特基势垒隧穿。莫特场效应晶体管采用与源极串联的相变存储单元,以实现 "电阻器 "电阻的突变,从而在存储状态切换时改变漏极电流,这也在I-V曲线中引入了滞后。超晶格场效应晶体管在源区采用多量子阱,形成一个人造共振隧穿带,该带足够窄,可过滤高能量(相对于费米级)载流子的热离子发射。狄拉克源 FETs利用向石墨烯源狄拉克点递减的DOS来减少高能载流子注入。这种器件可实现的最小SS值仍大于30 mV dec-1,原因很简单,因为石墨烯是无间隙的,也就是说,虽然狄拉克点附近的 DOS 值较低,但仍允许高能载流子泄漏。隧穿场效应晶体管(TFET)、利用源的带隙过滤高能载流子的热离子发射。

然而,低带对带隧穿概率限制了其导通电流。双极增强型TFET(BE-TFET)已被提出,通过利用BJT的大电流增益放大漏极电流来缓解这一问题。要证明这一器件概念,还需要实验论证。之前的一项研究在TFET上采用了铁电栅极(预计将起到NC的作用),结果发现TFET的性能得到了增强。至于这种增强是由于 NC 效应还是仅仅由于铁电材料的高 k 值,还需要进一步研究。从本质上讲,超晶格场效应晶体管、狄拉克源场效应晶体管和TFET具有类似的 "电阻 "形式,因为它们都是基于源中的DOS工程来实现费米级附近的局部载流子注入。冲击电离MOSFET(i-MOS)在冲击电离过程中利用电子-空穴对的超指数生成(相对于栅极电压)来实现漏极电流的超指数增长。

然而,激活撞击电离过程需要较大的Vd,因此无助于降低电源电压。在反馈型场效应晶体管中,有意在n型源极和p型漏极附近分别引入电子和空穴电位势垒,以形成电子-空穴再分布和势垒调制之间的正反馈回路,从而动态加快电子-空穴注入速率。该器件还需要较大的Vd值来激活反馈回路。 与上述基于电荷载流子的场效应晶体管相比,自旋场效应晶体管采用自旋作为信息载流子,并以磁阻的形式实现 "电阻"。值得注意的是,这里的自旋场效应晶体管指的是Rashba型,在这种晶体管中,自旋方向在从源极向漏极传输的过程中由一个小的栅极电场操纵。遗憾的是,在实验中很难控制自旋方向,这使得自旋场效应晶体管至今未能得到实验证明。在双层伪自旋(BiS)场效应晶体管中,据预测,电子-空穴对(玻色子)在分隔电子-空穴双层的绝缘体中的凝聚可显著降低层间电阻,从而实现电导的突然增加。不过,要验证双玻色场效应晶体管的器件概念,还需要进行实验论证。与SG FET相比,NEM继电器 在沟道/漏极交界处采用了NEM开关,以实现沟道和漏极之间的物理接触和分离。

这种机械开关存在严重的滞后可靠性问题,尤其是对超大规模器件而言。如图6所示,LP器件设计人员仍有很大的黑暗空间需要探索。值得注意的是,要实现这些未来晶体管,明智地选择材料平台将起到至关重要的作用。例如,二维材料的原始表面可用于开发超深斜率TFETs,而传统的块状材料很难实现这一点。 自2007-2008年提出NC FET的概念以来,由于其便于制造的结构(补图2a的下半部分),NC FET迅速崛起,成为一个引人注目的概念,它基本上是一个MOSFET,在氧化物和栅极之间插入了一个额外的NC(通常是铁电材料,FE)层。在FE存储器应用中,FE的双稳态被用来存储二进制信息,与此相比,NC FET被认为是利用FE层的瞬态,即NC,对外部电场提供负极化响应,从而更好地(<1)实现MOSFET的统一栅极效率(等式 (1))。如补充图2c所示,迄今为止,已有许多声称具有低SS的 "NC FET",其直流I-V曲线测量滞后相对较小。

然而,根据数控场效应晶体管的基本器件物理原理,由于现代场效应晶体管的量子电容普遍较大,且静电性能极佳,因此最近发现 数控场效应晶体管无滞后、低于60 SS的设计空间非常小。换句话说,这些测得的小SS值无法用静态NC解释来解释。事实上,越来越多的研究表明,它们可归因于测量过程中的瞬态效应和/或 FE 极化动态。最近的一项研究 发现,在FE层和栅极氧化层之间存在超高的陷阱密度(1014 cm-2)。因此,捕获和去捕获动态(不可控)可能是报告中 "NC FETs "陡坡的另一种解释。此外,电子器件中的高陷阱密度通常伴随着可靠性问题。因此,在CMOS产品中应用NC之前,需要开展大量的研究工作来解决这些问题,并深入了解FE与氧化物之间的相互作用。

超越摩尔的集成途径

在CMOS技术发展史上,大部分努力都是为了缩小MOSFET的特征尺寸,优化逻辑芯片的平面面积利用率,包括遵循摩尔定律的 "2.5D "芯片封装技术。有一天,我们不难发现,由于制造难度和成本以及功率密度的限制,MOSFET物理尺寸的缩小和器件集成密度的平面内增加已经停止。在这方面,逻辑芯片的垂直物理空间尚未得到充分利用。虽然FinFET以及NW和 NS FET可被视为这种努力的一种类型,但它们只有利于改善器件电流和静电,而无助于将器件集成密度提高到一定程度以上。在垂直空间堆叠器件(通常以互补方式)或裸片的三维集成被认为是提高器件密度的实用方法。三维集成电路除了具有密度扩展的优势外,还能显著降低互连延迟和功率耗散。三维集成可通过不同途径实现,包括基于线键合和/或倒装芯片的三维封装、基于硅通孔(TSV)的三维裸片/晶圆堆叠以及单片三维集成(m-3D)。

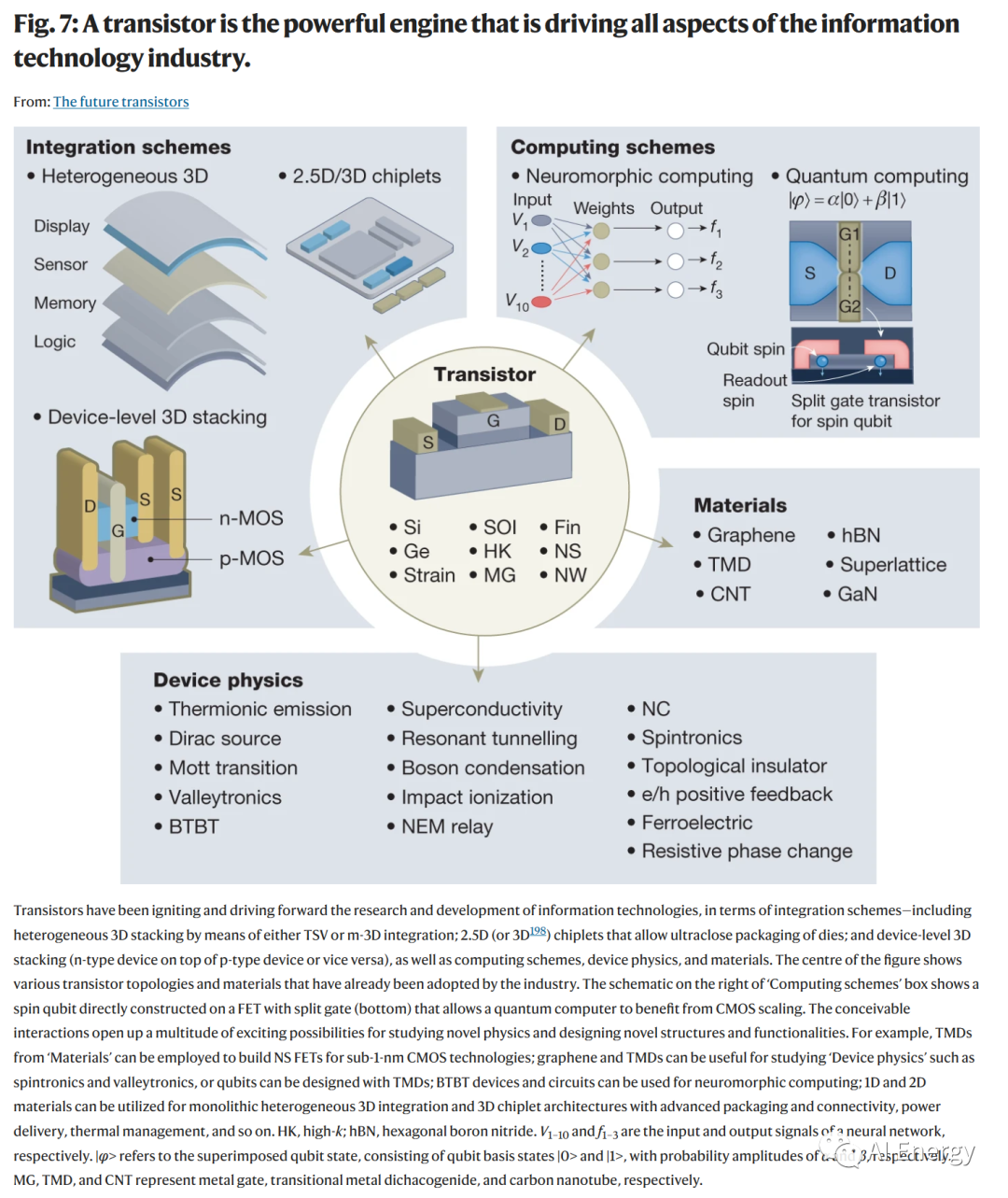

在这三种方法中,m-3D是最理想的方法,因为它具有较大的层密度和较高的局部连接设计可能性。虽然m-3D存在热预算和散热问题,但在克服这些挑战方面已取得了进展,例如采用固相外延再生长技术在600 °C以下激活掺杂剂、利用功率传输网络冷却3D集成电路以及采用高热传导六方氮化硼层间介质。三维集成是一种包容性技术。最终,它可以发展为异构三维集成的形式,在这种形式中,不同材料(如2DS和硅)、器件和功能的非常不同的系统可以沿垂直和横向集成在一起,从而构建一个超强、高能效的片上系统和异构芯片系统或芯片组(图 7)。尽管如此,器件和电路架构,如最近展示的0.5T0.5R混合电阻式随机存取存储器 ,不仅可以实现 "内存 "计算等计算模式,而且专门设计用于同时提供更高的横向和纵向堆叠密度,仍然是三维集成电路设计革命性进步的重中之重。

超越冯-诺依曼计算

信息技术从未停止过发展。除了为通用高性能计算而设计的经典计算机外,神经形态计算和量子计算也在积极发展之中,有望在某些领域(如化学反应模拟、人工智能和机器学习)带来前所未有的优势。如图 7 所示,所有这些领域的共同要求是晶体管具有超高的紧凑性和超低的漏电率,以及高电流驱动能力、坚固性和能效,晶体管可以是核心元件,也可以是辅助元件或接口元件。鉴于这些理想特性,我们有理由认为,晶体管的扩展和演进永远不会停滞,摩尔定律将在可预见的未来长期存在。

编辑:黄飞

-

功率场效应管MOSFET(功率场控晶体管)的原理及结构特点和参数2009-05-12 6387

-

"(分享设计)"晶体管电路设计2013-07-22 2175

-

SiC-MOSFET功率晶体管的结构与特征比较2018-11-30 5547

-

IGBT绝缘栅双极晶体管2019-05-06 2167

-

教你如何搭建浅层神经网络&quot;Hello world&quot;2020-12-10 1652

-

"STM32F0 Error: Flash Download failed - ""Cortex-M0""解决"2021-12-01 5555

-

芯片工艺的&quot;7nm&quot; 、&quot;5nm&quot;到底指什么?2023-07-28 13230

-

全方位精准测量技术助力:中国经济加力发展向前&amp;quot;进&amp;quot;2024-07-15 2526

-

CMOS晶体管和MOSFET晶体管的区别2024-09-13 6317

-

隧道管廊变压器局放在线监测:为地下&amp;quot;电力心脏&amp;quot;装上智能听诊器2025-04-09 991

-

电缆局部放电在线监测:守护电网安全的&amp;quot;黑科技&amp;quot;2025-04-14 1106

-

为什么GNSS/INS组合被誉为导航界的&amp;quot;黄金搭档&amp;quot;?2025-07-09 1134

-

&quot;Access violation&quot; 错误,复位位置,重新打印2025-11-08 734

-

选EtherCAT模块,别只看价格,先看&amp;quot;体检报告&amp;quot;2026-02-04 446

-

从&amp;quot;替代人力&amp;quot;到&amp;quot;智能协同&amp;quot;:履带式巡检机器人的产业跃迁2026-02-05 409

全部0条评论

快来发表一下你的评论吧 !