芯粒峰会:如何打通芯粒市场

描述

芯粒(chiplet)市场是整个芯粒领域最值得关注的话题之一。毫无疑问,技术问题会及时得到解决,例如芯粒裸片到裸片接口、创建良好的芯粒库格式,或是改善已知良好裸片的测试。但芯粒商业模式将何去何从,依然迷雾重重。

理想的模式是:准备好一个 Intel CPU 芯粒、一个 NVIDIA GPU 芯粒、一个高通调制解调器芯粒和一个 AMD/Xilinx FPGA 芯粒,然后将它们置于同一个系统级封装中即可。

但我们目前所处的阶段离这个目标还很遥远。

在今年美国硅谷举办的芯粒峰会(Chiplet Summit)上进行了一场题为“如何打通芯粒市场”的小组讨论会。该会议由 Meta 公司的 Ravi Agarwal 主持,与会者(下图中从左到右)依次为:

Ventana Micro Systems 公司的 Charles 先生

Alphawave Semi 公司(即 Alphawave IP 公司)的 Clint Walker

Marvell 公司的 Mark Kuemerle

NVIDIA 公司的 Durgesh Srivastava

Samsung Foundry 公司的 Kevin Yee

这场小组讨论会精彩纷呈,不仅座无虚席,甚至还有很多站着的听众。因此,本文总结了此次讨论会的精华内容,以与现场一致的问答形式与大家分享。

Q1. 多家公司的芯粒能否组合起来协调运行?

Ventana

大家对芯粒都很感兴趣,但当下只有自研芯粒的大公司才能生产出来。我们面临的挑战是,多家公司的芯粒能否组合一起协调运行?我们的生态系统中有很多不同的公司,今天就让我们讨论一下这个目标能否实现。

Alphawave 公司:我们今天的讨论十分火热,按某种规律来说,如果一次会议有很多人出席,那么五年之内就会形成一个市场。

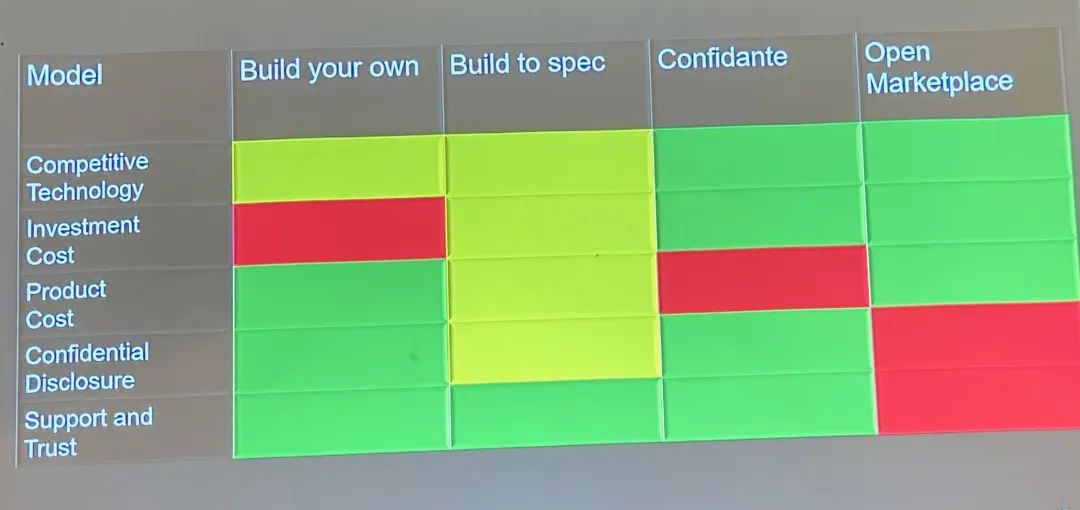

Marvell 公司:打造开放的芯粒市场,这个设想很美好,但需要克服很多障碍。理想化的情况是可以像逛商场一样随意挑选产品。目前,只有垂直整合公司或者供应商可以按照规范打造产品,只限于数量有限的芯粒和值得信赖的合作伙伴。这与“开放式芯粒市场”的构想相去甚远。那该如何循序渐进地实现这一点?下图展示了各种基于芯粒的设计实现方法的优点(绿色)和缺点(红色)。

NVIDIA 公司:业内认为,摩尔定律在推出 51 年后已经失效,就目前而言,超越摩尔定律成为了新常态。我们需要一种适合小型供应商的解决方案。

Samsung 公司:芯粒早已成为一种解决方案,但如何才能将其业务化或市场化?互操作性可能意味着要开发很多专有技术,对于市场来说,必须要有一个开放的标准。PCIe 之类的接口有“plugfest”事件来确保互操作性,那么裸片到裸片设计也需要类似的标准,但我们对此毫无头绪。封装是最棘手的问题之一。

Q2. 芯粒的未来市场需求

1.未来 5-10 年芯粒的市场需求如何?

Marvell 公司:大家时刻都在寻找一种方式来使用多芯片系统,以优化开支结构。多芯片系统属于高端基础架构。我们偶尔会开发单芯片,不过现在的需求寥寥无几。

Ventana 公司:汽车 ADAS 解决方案非常庞大,无论怎样,裸片终究需要分割开,所以不妨就此开始解决。我们需要有机基板,它不局限于超大型、造价超高的芯片。

两年内,AI 数据中心的市场规模将达到 5000 亿美元,需求很旺盛。对此,芯粒是唯一的选择。

NVDIA

Samsung 公司:我们和许多客户沟通过,其中一些垂直整合商表示,他们如今有 50% 的设计是基于芯粒的。在 5-10 年内,需求将非常高,但对其他厂商来说,我们需要构建一个生态系统。OSAT 需要准备就绪,接口互操作性也是必需的(UCIe 已经发布但尚不成熟)。Open HBI 好像消失了。

2.芯粒可以采取哪种商业模式,在 KGD(Known-good-die,已知良好裸片) 方面有什么经验可供分享?

Ventana 公司:一些厂商拥有最终设计,如果出现问题,可以联系自己的供应商,这与 IP 没有太大区别。芯粒有所不同,不过也有一些现行的模式。

AlpahWave

起初我们需要 ASIC 模式,现在正在努力提供更多标准选项,目标是在5-10 年后可以像逛商场一样挑选芯粒。

Marvell 公司:我们采用过“选择一个值得信赖的合作伙伴”模式。如果要从多个来源集成,如何启用多个芯粒就成为一项挑战,因为每个芯粒都有自己的测试功能和 KGD。我们需要找到相应的方法,让不同的公司可以分享更多信息,同时不必担心知识产权受损。

Samsung 公司:这将是一次革新,只是现在仍停留在商业谈判阶段,每个公司手握整个设计,但是还没有标准模式。

Q3. 芯粒未来发展需要考虑的问题

1. 如何确保芯粒的安全性?

Marvell 公司:安全的现行定义是一切都包含在一个 SoC 中。但问题是:只在一个芯粒中能否实现安全性?是不是每个公司都有各自的安全标准?重点是要让多个芯片以安全的方式统一运行。目前并不存在这种技术。

NVIDIA 公司:数据中心有很多安全要求,我们要确保传输、存储和计算过程中的安全性。

Alphawave 公司:安全启动也是一个问题。要把它置于哪个芯粒上?具体的位置是哪里?是否需要设计一个专用的安全芯粒?

2. 如果一个产品包含多个芯粒,最终客户会感知到利润的层层叠加吗?

我们认为答案是肯定的。在之前展示的虚构系统中,我希望每个芯粒都做到最好。在这种环境下,利润必定层层叠加。芯粒就像是一个包装好的产品,而我们秘制调料刚刚好。IP 模式已经是惯例,如果芯粒朝着IP的方向走,将会有新的变化。

Marvell

Ventana 公司:芯粒可以让人们买到想买的东西。如果开发的解决方案针对自己的需求,并且买到的东西也是恰好需要的,那么性价比就会很高。这将在一定程度上抵消利润层层叠加的问题。

Alphawave 公司:与我们如今面对的关于代工厂、IP 等方面的问题差不多。如果能买到支持 60 种不同产品的 I/O 芯粒,那么成本将会更低。UCIe 就像 PCIe,只需要“连上插头”就可以了。

3. 软件支持的问题又将如何?在芯粒中,使用微处理器来实现系统启动或初始化,那么对于每个子系统附带的软件,我们要为最终客户提供哪些支持?

Marvell 公司:这是当下芯粒面临的问题。垂直整合公司可以投入人力物力开发通用 API,也可以支持基于芯粒的系统。但这仅限于垂直整合公司或按规格加工的模式。相比之下,裸片到裸片的通信显得很简单。

Ventana 公司:这也是我们致力于解决的方向,必须搞清楚如何分区,就像是拼接一个 SoC ,然后提供一个完整的解决方案。

NVDIA

要构建芯粒生态系统,软件支持不可或缺。比如说如果四五家公司一起合作,那么肯定需要目前所缺乏的、通用的 API 框架。

Alphawever公司:没人能为我们买到所有的 IP,而现在我们必须提供五家不同供应商的 API,还要知道如何让客户无缝使用,挑战性很大。

Samsung 公司:在将基于芯粒的设计交付最终客户时,设计结果应该和 SoC 一样,像是 “一块大型芯片”,我们开发软件的方式也与开发 SoC 的方式相同。

4. 把 Compute Express Link (CXL) 和芯粒放在一起对比是个好主意。对于 CXL,我们有“结构管理器”,而这个术语没有明确的定义。在异构设计中,这种模式无法发挥作用。定义结构管理器会成为多芯粒设计的一部分吗?

NVIDIA 公司:结构非常重要。当前的 CXL 结构只能解决存储器一个方面的问题。它不是面向点对点的。CXL 还在纵向扩展,位于机架内。但我们也要考虑横向扩展机架到机架。

Marvell 公司:并非所有的芯粒系统都将基于 PCIe 或 CXL。如果结构管理器以不同的方式通信,能否依赖一个定义好的结构管理器标准,这需要打上一个问号。

Q4. 现场观众提问

1. 大家都对芯粒都充满期待,我也是芯粒的忠实拥护者。芯粒的物理外形尺寸与 IP 区别很大。我们要如何解决这一点?在解决这个问题之前,很难打造一个统一市场。

Alphawave 公司:bump 间距不一样,通道数量之类也不一样。一切都是不同的,应该根据需求确定优先级。

Marvell 公司:没有哪种合理的方法可以让外形尺寸标准化,以便将芯粒整齐排列在一起。我们还需要开发出多个裸片到裸片接口解决方案。这种“俄罗斯方块”一样的排列问题很难解决。

2. 外形尺寸方面如何?

Alpahwave 公司:这需要根据上市时间进行权衡。比如说本来预计有两个通道,但最终出现了 16 个。要么只能采用这 16 个通道,要么就再等一年,才能实现两个通道的设计。

这和 FPGA 类似,它们的尺寸永远都不能做到完美匹配。

Samsung

Marvell 公司:什么时候才是创建芯粒的合适时机?把各种功能都打包在一个芯粒中,现在这种想法也许不切实际。

Alphawave 公司:如果竞争对手在单芯片市场一路领先,那就意味着错失良机。芯粒可能不是唯一的答案。

3. 我们经常会讨论大型裸片的解体。那对于小型裸片呢,比如智能手表里的裸片?它们具有同样的应用价值吗?

Marvell 公司:芯粒有很多应用领域。

NVDIA

我们看过 Apple Watch 的拆解过程,它的基板架构上有一块主板,这已经算是芯粒。

Alphawave 公司:很多产品都在缩小外形尺寸。

Samsung 公司:随着产品尺寸缩小,接口成本增加了。如果接口可用于多种应用,那么直接使用没问题。但仅仅为了芯粒而做芯粒是没有意义的。

Ventana 公司:如果是大型数据中心芯片,那就简单多了。成本下限在不断降低,但也不会一直降到 10 美元。

4. 现在有形成某种格局吗?有些想做芯粒的客户联系我们,但通常不太合适。有没有学术研究表明技术节点是否成熟?行业格局目前又如何?这样客户就可以知道是否会盈利。

OCP 开放成本模型是目前最好的模型。它提供了 15 到 20 个变量,是很好的初步计算工具。

Meta

Alphawave 公司:我们用一张图表来确定盈亏平衡点。

Samsung 公司:我们参与了那个开放成本模型的开发,但它是高层次的工具,不会显示详细的成本。它基于电子试算表,用户可以更改变量。

Meta公司:他们很快就会发布新版本的模型。

5. 刚才提到未来该采用哪种成本模型,也许 IP 模型也是一样的,40 多年前花 10 或 20 美元就能买到标准元件,但 FPGA 市场每个要花 10 万美元。ASIC 的 IP 模型不适用于 FPGA。现在,芯粒能像40 多年前一样,花 10 或 20 美元买到元件,然后构建一个系统吗?

Alphawave 公司:如果想自主构建芯粒,那么 IP 模式还是行得通的。但对于芯粒本身,则需要购买整个产品。

Marvell

我们梦寐以求的正是无需为先进的技术掩膜付费,也无需购买相关的掩膜。掩膜成本远远高于 IP 成本。

Ventana 公司:不需要花大笔的钱来获得 IP 核心许可,可以直接购买芯粒。

Samsung 公司:有一天芯粒会成为一种商品,公司可以数百万地制造,很多客户想要购买里面的小元件。但这一天目前还没有到来。

多芯粒架构为最新的设计节点提供了成本更低的选择,同时仍然以物理芯粒的形式,提供基于 IP 的重用模型。如今,封装设计已成为新一代电子产品的核心。

全部0条评论

快来发表一下你的评论吧 !