追赶SK海力士,三星、美光抢进HBM3E

追赶SK海力士,三星、美光抢进HBM3E

描述

电子发烧友网报道(文/黄晶晶)新型存储HBM随着AI训练需求的攀升显示出越来越重要的地位。从2013年SK海力士推出第一代HBM来看,HBM历经HBM1、HBM2、HBM2E、HBM3、HBM3E共五代产品。对于HBM3E,SK海力士预计2023年底前供应HBM3E样品,2024年开始量产。8层堆叠,容量达24GB,带宽为1.15TB/s。

近日,三星电子也更新了HBM3E的进展。据韩媒报道,三星电子已确认将其第五代HBM3E产品命名为“Shinebolt”,并正在向客户公司发送HBM3E产品Shinebolt原型机进行质量认可测试。Shinebolt为8层堆叠的24GB芯片,带宽比HBM3高出约 50%,达到1.228TB/s。另外,后续还有12层堆叠的36GB产品开发。

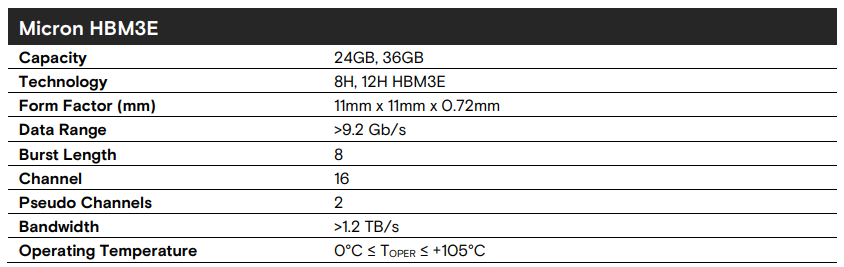

而美光首席执行官Sanjay Mehrotra透露,美光计划于2024年初开始大量出货HBM3E。美光HBM3E目前正在进行英伟达认证,首批HBM3E采用8-Hi设计,提供24GB容量和超过1.2TB/s带宽。计划于2024年推出超大容量36GB 12-Hi HBM3E堆叠。

HBM3E的推出是为了配合应用于2025年NVIDIA推出的GB100。此前SK海力士一直在HBM市场份额上处于领先,不过三星、美光也开始了追赶,三家在HBM3E上的堆叠、容量、带宽等都比较接近,将不可避免地进行交锋。

HBM的制造技术也在产品迭代中得以进步。HBM的堆叠主要采用硅通孔 (TSV) 键合。资料显示,TSV不采用传统的布线方法来连接芯片与芯片,而是通过在芯片上钻孔并填充金属等导电材料以容纳电极来垂直连接芯片。制作带有TSV的晶圆后,通过封装在其顶部和底部形成微凸块,然后连接这些凸块。由于 TSV 允许凸块垂直连接,因此可以实现多芯片堆叠。

粘合工艺是HBM的关键制造步骤,TSV倒装芯片接合方法通常使用基于热压的非导电薄膜 (TC-NCF)。三星从HBM生产的早期阶段就一直采用热压缩非导电薄膜 (TC-NCF) 方法。近来三星优化其非导电薄膜(NCF)技术,以消除芯片层之间的间隙并最大限度地提高热导率。

SK 海力士从HBM3开始采用的先进大规模回流成型底部填充 (MR-MUF) 工艺,可以减少堆叠压力并实现自对准。由于采用MR-MUF技术,2023年4月SK hynix 开发了其12层HBM3。

根据SK海力士官网介绍,MR-MUF是将半导体芯片堆叠后,为了保护芯片和芯片之间的电路,在其空间中注入液体形态的保护材料,并进行固化的封装工艺技术。与每堆叠一个芯片时铺上薄膜型材料的方式相较,工艺效率更高,散热方面也更加有效。

对于更先进的HBM封装,SK海力士、三星都在加速开发混合键合工艺。

根据SK海力士官网介绍,混合键合(Hybrid Bonding)技术采用Cu-to-Cu(铜-铜)键合替代焊接。Cu-to-Cu(Copper-to-Copper, 铜-铜)键合作为封装工艺的一种混合键合方法,可在完全不使用凸块的情况下将间距缩小至10微米及以下。当需要将封装内的die相互连接时,可在此工艺中采用铜-铜直接连接的方法。如下图第一排第三张示意图。

混合键合技术可以进一步缩小间距,同时作为一种无间隙键合(Gapless Bonding)技术,在芯片堆叠时不使用焊接凸块(Solder Bump),因此在封装高度上更具优势。

此前SK海力士推出的HBM2E,采用混合键合成功堆叠1个基础芯片和8个DRAM芯片。而为了推进HBM4产品的开发,三星电子正计划采用针对高温热特性优化的非导电粘合膜(NCF)组装与混合键合(HCB)等技术。

-

10纳米DRAM制程竞争升温,SK海力士、美光加速追赶三星2018-11-12 630

-

SK海力士开发出全球最高规格HBM3E2023-08-21 2139

-

SK海力士推出全球首款HBM3E高带宽存储器,领先三星2024-02-21 1626

-

SK海力士HBM3E正式量产,巩固AI存储领域的领先地位2024-03-19 1984

-

SK海力士成功量产超高性能AI存储器HBM3E2024-03-20 2130

-

刚刚!SK海力士出局!2024-03-27 1670

-

三星HBM3E芯片验证仍在进行,英伟达订单分配备受关注2024-05-16 2172

-

SK海力士HBM3E内存良率已达80%2024-05-23 1356

-

SK海力士:HBM3E量产时间缩短50%,达到大约80%范围的目标良率2024-05-27 2318

-

三星HBM3E内存挑战英伟达订单,SK海力士霸主地位受撼动2024-08-23 2036

-

三星、SK海力士及美光正全力推进HBM产能扩张计划2024-08-29 2234

-

SK海力士9月底将量产12层HBM3E高性能内存2024-09-05 2030

-

SK海力士推出48GB 16层HBM3E产品2024-11-05 1635

-

SK海力士展出全球首款16层HBM3E芯片2024-11-13 1488

-

SK海力士发布HBM3e 16hi产品2024-11-14 1665

全部0条评论

快来发表一下你的评论吧 !