如何利用相位噪声分析程序和传递函数来降低锁相环的输出相位噪声?

描述

本文摘要:

本文是关于相位噪声建模、仿真和传播在锁相环中的应用的第三部分。文章介绍了相位噪声的理论和测量方法,并探讨了相位噪声的分析与建模过程。通过分析示例合成器,作者演示了如何利用相位噪声分析程序和传递函数来降低锁相环的输出相位噪声。同时,文章指出了选择合适的环路带宽对于优化相位噪声至关重要。总体而言,本文提供了关于锁相环和相位噪声的详细介绍,对于研究锁相环和相关领域的读者具有参考价值。

如第1部分和第2部分所述,锁相环 (PLL) 在当今的高科技世界中无处不在。几乎所有商业和军用产品都在其运行中使用它们,并且相位(或 PM)噪声是一个主要问题。频率(或 FM)噪声密切相关(瞬时频率是相位的时间导数),并且通常被认为是在相位噪声的范畴内(也许两者都可以被视为“角度噪声”)。幅度(或 AM)噪声是另一个考虑因素。

虽然两者都会影响 PLL 性能,但幅度噪声通常是自限性的,不会产生任何后果。因此,PLL 输出和 RF 组件的相位噪声是主要问题。当然,输出相位噪声是最终关注的问题,并且很大程度上取决于每个组件的相位噪声。造成组件相位噪声的因素有很多,例如电源、EMI 和半导体异常等,了解这些因素使我们能够实施组件相位噪声的缓解策略,并最终实现输出相位噪声的缓解策略。

在第 3 部分中,我们分析示例假设的合成器以演示所提出的概念和方法。

示例(来自第 2 部分):8 至 12 GHz 输出/50 MHz 步进 PLL 频率合成器的相位噪声分析

我们使用相位噪声分析程序和特定 PLL 框图和相位噪声传播模型 (图 8,第 2 部分)进行分析,在五个输出上完成:8-9-10-11-12 GHz。

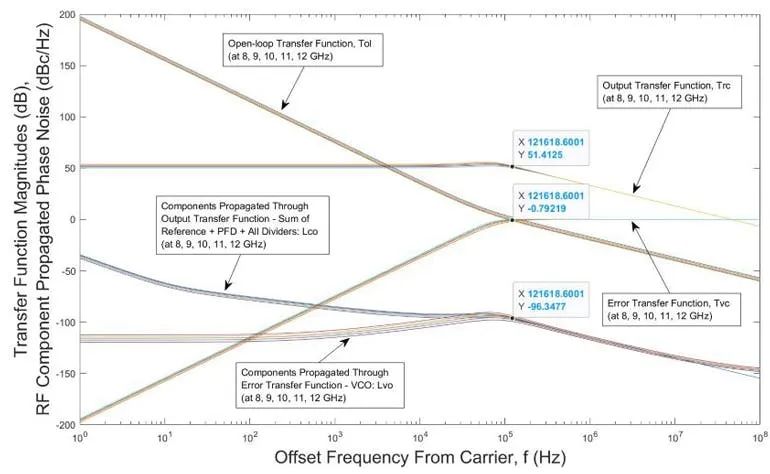

对于之前使用该过程的步骤 1 到 6 开发的所有射频组件相位噪声模型,我们现在使用步骤 7(请参阅第 2 部分)并将所有组件相位噪声模型乘以其适用的(输出或误差)传递函数幅值平方给出他们的传播相位噪声模型。除了开环、输出和误差传递函数(下面讨论)之外,还对模型进行了仿真(图 9)。

9. 8 至 12 GHz 输出/50 MHz 步进 PLL 频率合成器的传递函数幅度和 RF 分量传播相位噪声。

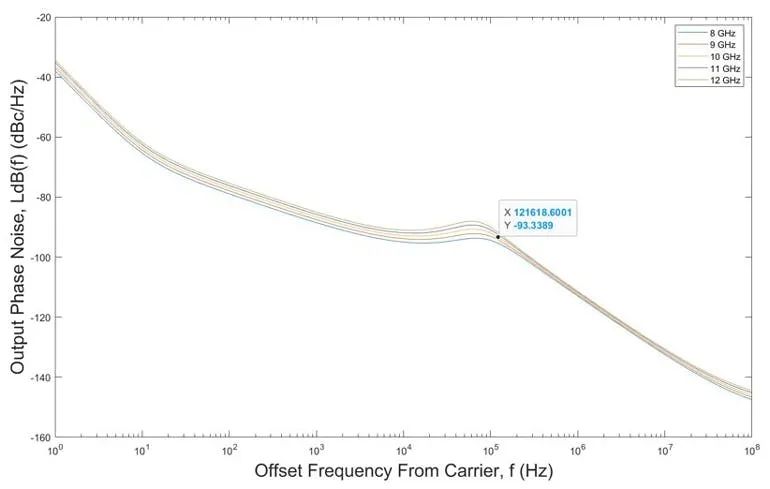

然后,我们使用该过程的步骤 8(请参阅上面的链接)并添加所有组件的传播相位噪声模型以给出输出相位噪声模型,该模型在图 10 中进行了模拟。

10. 示例 8 至 12 GHz 输出/50 MHz 步进 PLL 频率合成器的输出相位噪声。

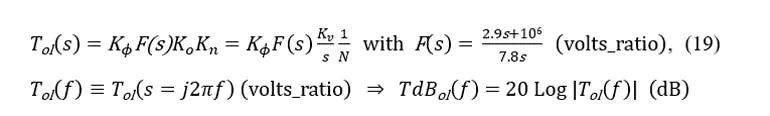

A. 开环传递函数,T ol(8-9-10-11-12 GHz 输出)

参考图 8,通过标准框图分析,我们得到开环传递函数 T ol(在 8-9-10-11-12 GHz 输出):

模拟图 9中 TdB ol (f)的五种情况(选择 K Φ、 K v、 N适用于 8-9-10-11-12 GHz 输出)。

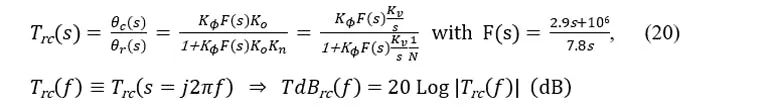

B. 通过输出传递函数 T rc传播的分量(在 8-9-10-11-12 GHz 输出)

再次参考图 8,我们得到输出传递函数,同样来自标准框图分析,有源低通滤波器 T rc(在 8-9-10-11-12 GHz 输出):

模拟图 9中 TdB rc (f)的五种情况(选择 K Φ、 K v、N 表示 8-9-10-11-12 GHz 输出)。

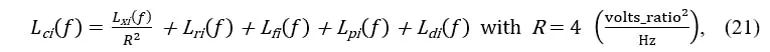

然后,再次参考图 8 ,我们将上述分析应用于适用组件(基准、基准分频器、反馈分频器、预分频器和相位检测器)相位噪声模型,表示为L ci。这些由 T rc进行处理,以找到这些组件的传播相位噪声模型,用 L co表示,如图 9所示:1,4,5

模拟图 9中 LdB co (f)的五种情况(为 8-9-10-11-12 GHz 输出选择 K Φ、 K v 、 N )。

C. 通过误差传递函数 T vc传播的分量(在 8-9-10-11-12 GHz 输出)

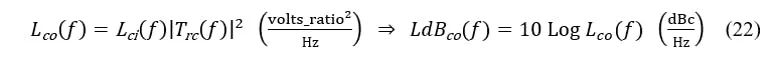

再次参考图 8 ,我们得到了误差传递函数,它再次来自标准框图分析,即有源高通滤波器 T vc(在 8-9-10-11-12 GHz 输出):

模拟图 9中 TdB vc (f)的五种情况(为 8-9-10-11-12 GHz 输出选择K f、K v、N )。

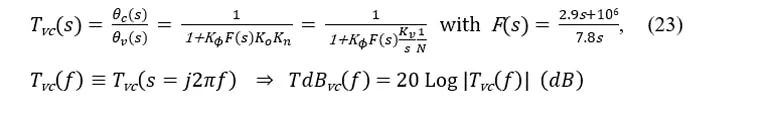

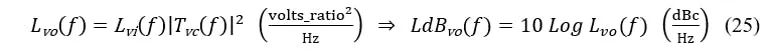

然后,最后一次参考图 8 ,我们将上述分析应用于单个适用组件 (VCO) 相位噪声模型 L vi (在 11.3 GHz 时从 L 11.3缩放到 8-9-10-11-12 GHz)数据表上给出)。它由 T vc处理以找到该组件的传播相位噪声模型 L vo,该模型在图 9中进行了仿真:1,4,5

模拟图 9中 LdB vo (f)的五种情况(为 8-9-10-11-12 GHz 输出选择 q、K Φ、K v 、N)。

D. 输出相位噪声(8-9-10-11-12 GHz 输出)

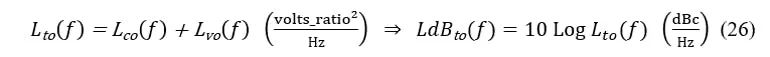

现在,我们完成上述分析,并添加由 T rc处理的分量传播相位噪声模型(由L co表示)和由 T vc处理的单分量传播相位噪声模型(由 L vo表示)。这将给出输出相位噪声模型 L to,该模型在图 10中进行了仿真:

模图 10中 LdB至(f)的五种情况(为 8-9-10-11-12 GHz 输出选择 K Φ、K v、N )。

因此,相位噪声分析(建模、仿真和传播)是完整的,并且直观上看起来是合理的。从模拟中可以明显看出以下几点:

在从 ~1 Hz 到 ~10 Hz 的近距离区域中,参考值及其一阶和高阶闪烁贡献是清晰的。

VCO 在约 100 kHz 至 > 100 MHz 的远处区域是清晰的,也具有一阶和高阶闪烁贡献。

其他分量在 ~10 Hz 至 ~100 kHz 的中间区域清晰可见,具有本底(0阶)贡献和一阶闪烁贡献。

对于大多数情况来说,这代表了相当标准的配置文件。

如前所述,最佳相位噪声通常是通过选择中频输出的 VCO 和基准相位噪声曲线相交处的环路带宽来实现的。然而,在某些需要对参考相位噪声进行更多抑制的情况下,可以使环路带宽更窄以实现这一点,但随之而来的是 VCO 和基底噪声的增加。当然,如果需要更多地抑制 VCO 相位噪声,可以加宽环路带宽来实现此目的,但会随之增加参考噪声和基底噪声。总是需要进行权衡。

结论

我们展示了如何对一般相位噪声进行建模和仿真,以及 RF 分量相位噪声如何通过 PLL 传播以确定其输出相位噪声。我们首先讨论了相位噪声的一些简要理论和典型测量。然后我们讨论了相位噪声的分析,并介绍了我们的相位噪声分析程序,其中详细展示了大多数 CAD 应用程序使用的分析方法。

最后,我们通过设计和分析假设的单环路 8 至 12 GHz 输出/50 MHz 步进整数 PLL 频率合成器来演示所提出的概念和方法。它通过在 10 GHz 中频带输出处实现最低相位噪声,在整个频带内产生最低的平均输出相位噪声。

对于我们的示例合成器,我们选择了组件并开发了它们的相位噪声模型(即射频组件的)。然后使用其适用的传递函数(输出或误差)将分量相位噪声模型传播通过合成器(即PLL)以获得其传播的相位噪声模型。然后将分量传播的相位噪声模型相加,得到输出相位噪声模型。所有模型均经过仿真以显示其相位噪声曲线。我们对 8-9-10-11-12 GHz 五个输出进行了分析,结果直观上似乎是合理的。

我们还利用了 MATLAB 先进的计算能力。未来可能的努力可能包括考虑更复杂的因素(例如具有相关相位噪声的组件和/或影响输出相位噪声的其他微妙现象的组件)的类似分析。

审核编辑:刘清

-

分布式系统的组合相位噪声性能怎么评估?2019-08-02 1617

-

从哪几方面去分析电荷泵锁相环系统的相位噪声特性?2021-04-07 1976

-

锁相环相位噪声与环路带宽的关系是什么2021-06-07 2678

-

锁相环频率合成器:相位噪声问题和宽带循环2009-07-25 987

-

锁相环(PLL)和相移键控(PSK)系统的相位噪声2008-11-24 2361

-

锁相环相位噪声与环路带宽的关系分析2012-11-22 24720

-

如何在锁相环中实现相位噪声和杂散性能2019-05-21 6825

-

CN-0369:低相位噪声的转换锁相环频率合成器2021-03-20 1193

-

切勿让不良参考信号破坏锁相环/合成器中的相位噪声2022-11-02 738

-

具有分布式锁相环的相控阵的系统级LO相位噪声模型2022-12-22 2179

-

锁相环在相位检测中的应用2023-10-29 2056

-

带有分布式锁相环的相控阵系统级LO相位噪声模型2023-11-22 612

-

锁相环的输入输出相位一致吗?2024-01-31 2730

-

锁相环相位噪声的影响因素2024-07-30 5203

-

锁相环PLL的噪声分析与优化 锁相环PLL与相位噪声的关系2024-11-06 4851

全部0条评论

快来发表一下你的评论吧 !