介绍一下Layout相关效应

电子说

描述

高性能模拟电路中如果layout处理不好很容易恶化模拟电路性能,除了之前给大家介绍的版图布局布线及电源网络的划分,还要留意LDE(Layout Dependent Effect),LDE主要包含STI(Shallow Trench Isolation)和WPE(Well Proximity Effect),本期重点介绍一下这两种效应并简单介绍一下其他layout相关效应,希望对大家有所帮助。

1. LDE

layout相关效应主要包含以下几个方面:

其中LOD(Length of Diffusion)Effect,也称为STI Stress Effect。下面章节将逐一展开layout相关效应。

2. 常见LDE****定义

2.1 LOD

LOD(Length of Diffusion)Effect,也称为STI Stress Effect,顾名思义就是有源区外的STI隔离会对其带来应力作用,从而影响晶体管阈值电压,通常用Poly到有源区边界的距离(SA/SB,如Fig9所示)来描述,如图1所示。

Fig1. LOD效应

2.2 WPE

集成电路在制造过程中,对阱作离子注入时,注入的离子与阱区周围的光刻胶发生溅射而富集在阱的边缘,因而在水平方向呈现掺杂浓度的非均一性,这会导致阱区中的MOS管的阈值电压随晶体管与阱边缘的距离(SC_L/SC_R/SC_T/SC_B,如Fig9所示)而发生变化,这一特性称为WPE,如图2所示。

Fig2. WPE效应

2.3 OSE

OD到OD之间的距离(SFAX_L/SFAX_R/SFAX_T/SFAX_B,如Fig9所示)也会影响晶体管特性,这一特性称为OSE,如图3所示。

Fig3. OSE效应

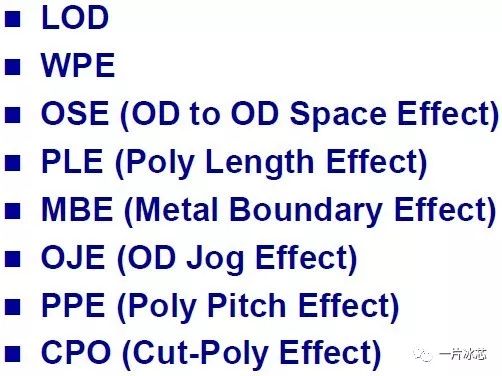

2.4 PLE

Length长度(PLODA1/PLODA2/PLODA3/PLODB1/PLODB2/PLODB3,如Fig9所示)也会影响晶体管特性,这一特性称为PLE,如图4所示。

Fig4. PLE效应

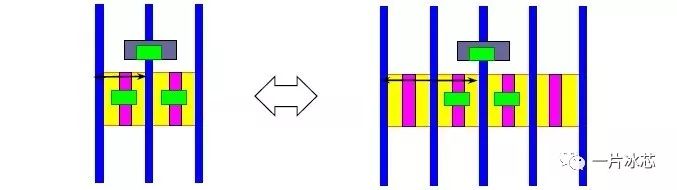

2.5 MBE

N/P管金属边界之间的距离(SMBT/SMBB,如Fig9所示)也会影响晶体管特性,这一特性称为MBE,如图5所示。

Fig5. MBE效应

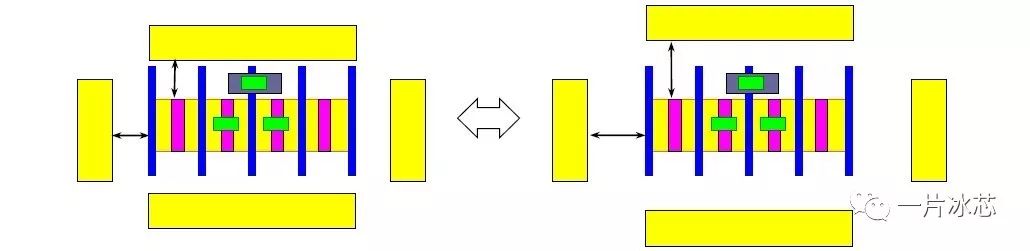

2.6 OJE

拐角的OD与非拐角OD也会影响晶体管特性,这一特性称为OJE,如图6所示。

Fig6. OJE效应

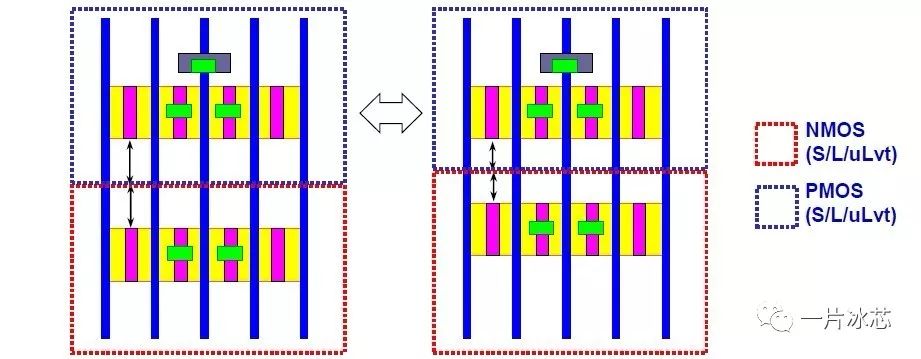

2.7 PPE

Poly之间的pitch也会影响晶体管特性,这一特性称为PPE,如图7所示。

Fig7. PPE效应

2.8 CPO

Poly Cut的位置也会影响晶体管特性,这一特性称为CPO,如图8所示。

Fig8. CPO效应

2.9 LDE Summary

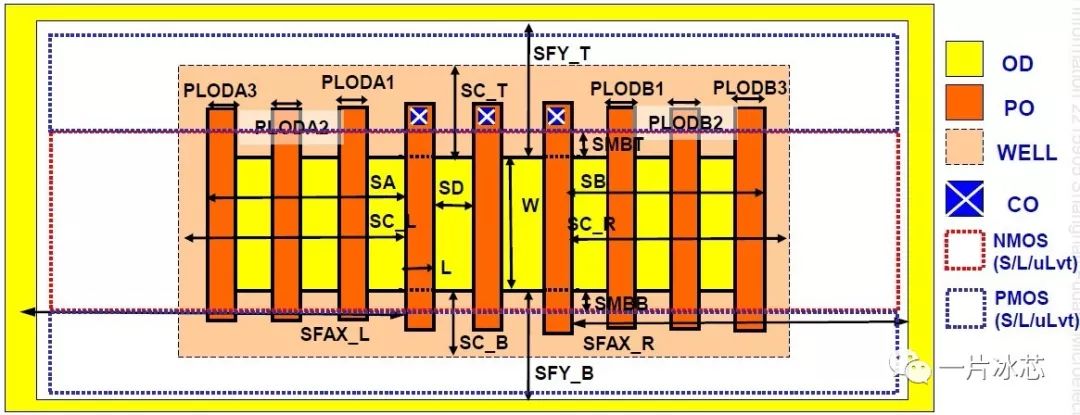

2.1~2.8节中的LDE总结如下图9所示。

Fig9. LDE Summary

图中参数说明如下:

前后仿网表中LDE相关参数如下:

3. 项目中的LOD****问题

图10为lcvco中的偏置电路,后仿发现ss_lvlt(ss低温低压)corner下lcvco振荡频率偏小。为了debug这一问题,尝试了很多方法,前仿时偏置电流由50uA加大到100uA发现与后仿现象一致,因此怀疑后仿时注入lcvco的电流偏大引起lcvco振幅偏大,进而使lcvco中等效并联电容偏大,降低了振荡频率。

后仿发现ss_lvlt corner下M1管的阈值电压偏大,导致M1管源端电压低到70mV,而M4管源端电压为200mV,由于沟道长度调制效应,使得流过M4管的电流偏大,进而降低了lcvco振荡频率。

查看layout发现M1管两侧未加dummy管,有源区边界处的STI隔离产生的应力使得M1管阈值电压偏大,M1管两侧加dummy后,再次后仿发现ss_lvlt corner下lcvco振荡频率正常。

Fig10. lcvco中的偏置电路

4. 减小LDE****方法

①减小阱的个数,将同一电位的器件放在一个阱里,适当拉大有源区到阱边界的距离,NMOS距离阱边界较近时,阈值电压会增大50mV,当距离拉大到3um以上,阈值电压基本不受影响;②提高管子的对称性并加入dummy,减小STI应力的同时增大了非dummy器件到阱边界的距离;③对于高性能模拟电路而言,尽可能保持管子周围及自身环境(包括OD到OD间的距离、Poly长度等)一致。

-

详细介绍一下PSS+Pnoise仿真2023-11-03 24408

-

介绍一下S参数的基础知识2023-06-15 15909

-

介绍一下高低温试验箱的校验项目与方法2023-05-11 1208

-

了解一下DC-DC的layout2023-02-12 3061

-

看一下MOSFET场效应管的相关知识内容和典型的使用方法2022-10-27 2398

-

了解一下AOC有源光缆的相关知识2022-03-25 3125

-

介绍一下EMC相关知识2021-12-29 1663

-

请问一下电流的热效应是什么意思2021-10-11 1831

-

电磁炉加热一下就停一下什么原因2021-06-04 42020

-

详细介绍一下ACM的优点资料下载2021-04-20 1814

-

电磁炉加热一下就停一下什么原因及解决办法2020-03-18 289159

-

作为一个PCB Layout工程师,得赛一下作品!2019-09-12 0

-

什么是巨磁电阻效应_巨磁电阻效应的应用介绍2018-05-11 31840

-

简要介绍一下Python-UNO的使用方法2018-01-04 10019

全部0条评论

快来发表一下你的评论吧 !