Xilinx FPGA学习笔记

描述

一、时序设计

方法1.通过状态机来实现,通过verilog控制FPGA,让它该快的时候快,该慢的时候慢。

方法2.FPGA中运行CPU

把逻辑控制顺序复杂的事情用C代码来实现,而实时处理部分用verilog实现,并且verilog这部分可以被C代码控制。Xilinx的FPGA目前支持的CPU有Microblaze,ARM9,POWERPC,其中Microblaze是软核,其余的两款是硬核。

(1)软核就是用代码实现的CPU核,配置灵活;

(2)硬核就是一块电路,已经做好了,不能再发生变化;

软核灵活性好,但是要占用FPGA的资源。硬核不占用FPGA的资源,速度和性能更好。比如Xilinx的DDR内存控制器,就是一种硬核,其运行速度很高。

二、基础语法

1. always @(),括号里是*,表明是一直敏感的;

2. (1) <= 非阻塞赋值,在一个always模块中,所有语句一起更新

(2) = 阻塞赋值,或者给信号赋值,如果在always模块中,这条语句被立刻执行。

非阻塞赋值

always @(posedge clk)begin a <= b; c <= a; end

执行结果是a的值是b,c的结果依旧是a

阻塞赋值

always @(posedge clk)begin

a = b;

c = a;

end

执行结果a的值是b,c的结果也是b。

一般我们使用的都是非阻塞的赋值语句,这样可以很好地控制同步性。

3、预处理命令

`include file1.v

`define X=1;

`define Y;

`ifdef Y

Z = 1;

`else

Z = 0;

`endid

有时候需要一些公共的宏参数,我们可以放在一个文件中,比如文件名XXX.v,。那么我们就可以 `include XXX.v ,就可以包含文件中定义的宏参数

三、小练习

1.加法器的设计

module adder(

input [3:0] a,

input [3:0] b,

input cin,

output [3:0] sum,

output cout

);

assign {cout,sum} = a + b + cin;

endmodule

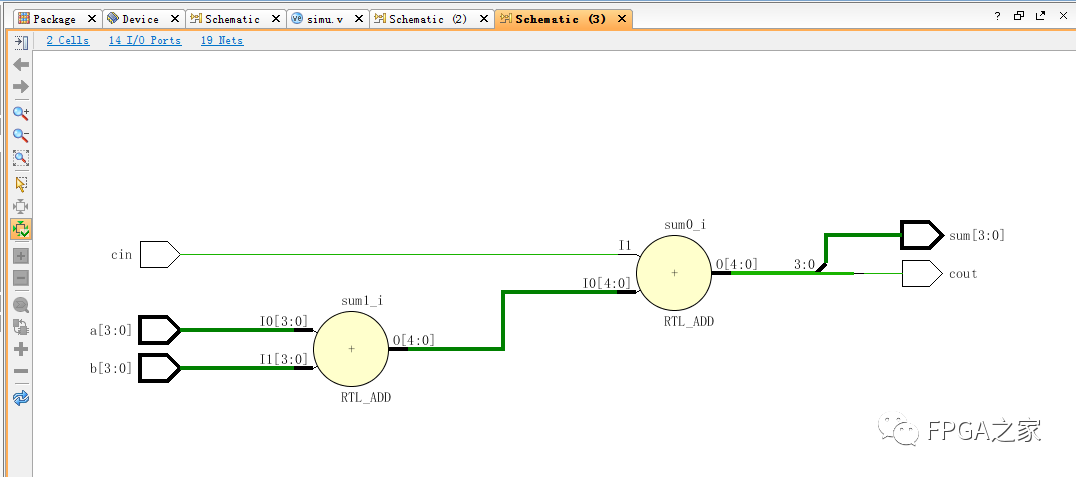

RTL视图

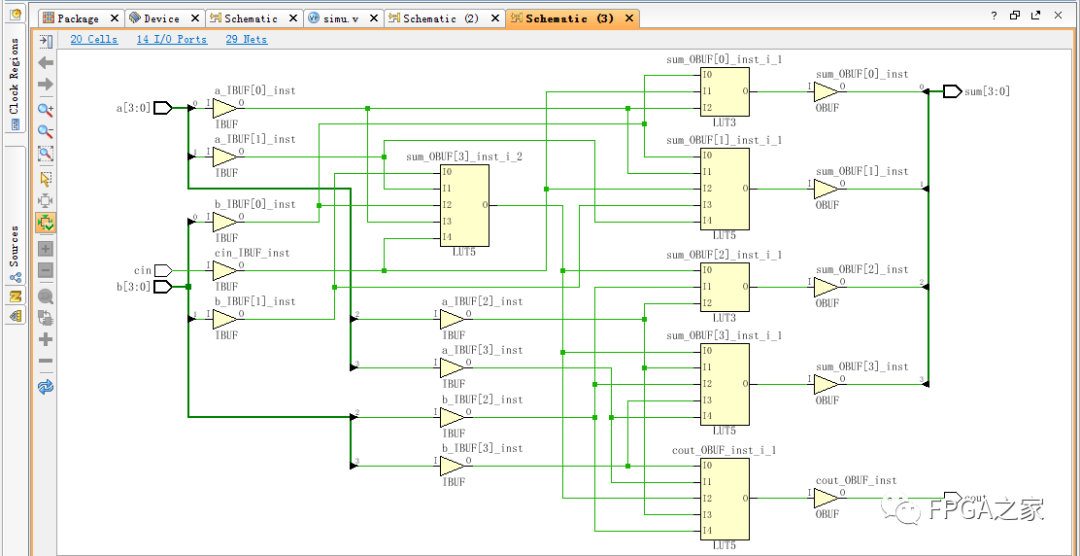

RTL 技术原理图

仿真代码

`timescale 1ns / 1ps //1ns的仿真刻度,1ps的仿真精度

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2017/10/22 1058

// Design Name:

// Module Name: simu

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module simu(

);

reg [3:0] a;

reg [3:0] b;

reg cin;

wire cout;

wire [3:0] sum;

reg [4:0] i,j; //中间变量

adder inst(

.a(a),

.b(b),

.cin(cin),

.cout(cout),

.sum(sum)

);

initial begin

a =0; b=0; cin=0;

for(i=1;i<16;i=i+1)

#10 a = i;

end

initial begin

for(j=1;j<16;j=j+1)

#10 b = j;

end

initial begin

$monitor($time,,,"%d + %d + %b = {%b,%d}",a,b,cin,cout,sum);

#160 $finish; //160ns 后仿真结束

end

endmodule

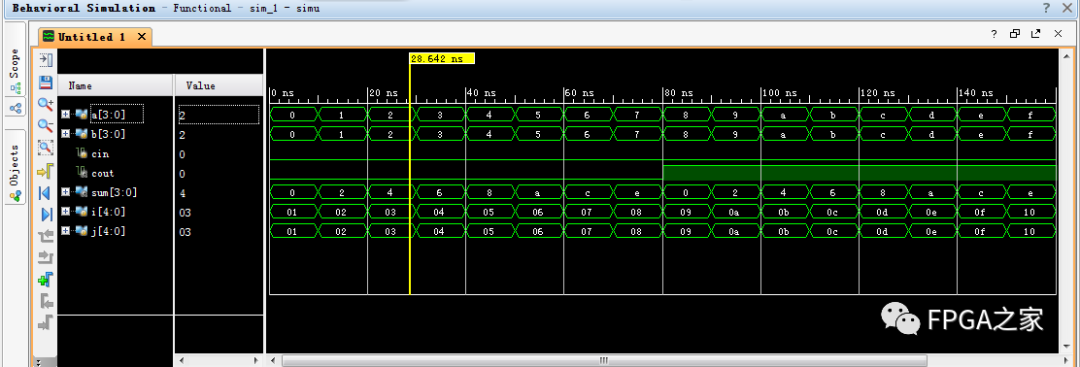

仿真波形

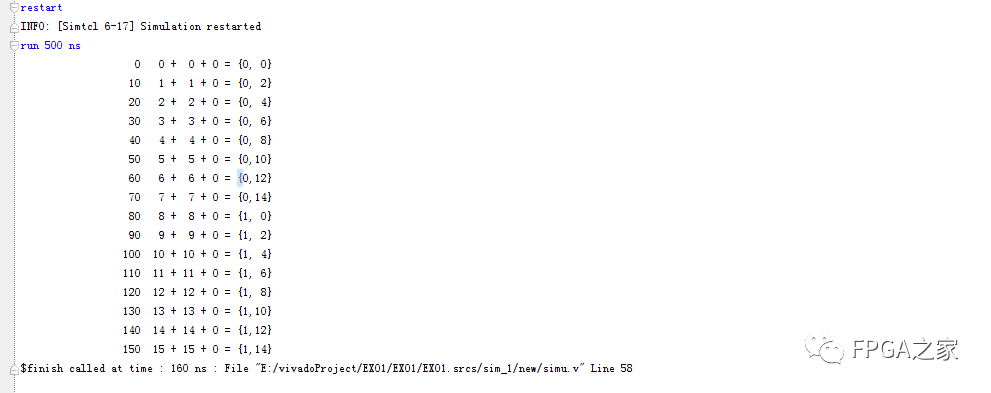

打印输出结果

-

Xilinx FPGA学习笔记:原语BUFIO的理解2023-05-08 4027

-

Altera FPGA CPLD学习笔记2021-09-18 1693

-

FPGA学习教程之硬件设计基本概念2020-12-25 1385

-

如何借助Xilinx FPGA和MATLAB技术加速机器学习应用2019-12-25 3214

-

Xilinx FPGA如何通过深度学习图像分类加速机器学习2018-11-28 4622

-

【Artix-7 50T FPGA申请】FPGA由Altera转Xilinx系列笔记2016-10-11 6871

-

Xilinx-FPGA高级开发工具2016-09-01 1044

-

Xilinx_FPGA系列入门教程(一)—如何搭建Xilinx2016-01-18 905

-

入门 Z-turn Board 学习笔记(汇总ing)2015-07-06 6828

-

分享一本学习xilinx FPGA的好书2014-07-18 15641

-

FPGA学习笔记汇总(7.13更新)2014-06-20 2641

-

Xilinx学习资料2014-03-11 3610

-

Xilinx FPGA学习笔记(1):1602液晶IP核设计与实现2012-11-20 18989

全部0条评论

快来发表一下你的评论吧 !