趣谈混合信号模型与仿真实践

电子说

描述

在工作中会遇到不少建立模型,建立顶层仿真并在后期进行验证的工作。应版主把个人零星的一些感受总结一下。

主要工作角色还是模拟设计工程师,日常负责的也主要是模拟模块的设计。因此建模使用的比较多的还是Verilog和VerilogA。会写一些数字模块作为辅助。数字域和模拟域通常是严格分离的。

真正的VerilogAMS混合信号的模块几乎没有。SystemVerilog,UVM之类的技术似乎更加偏向数字领域。看过EENET实现的一些模拟模型。 感觉就是:我的天啊

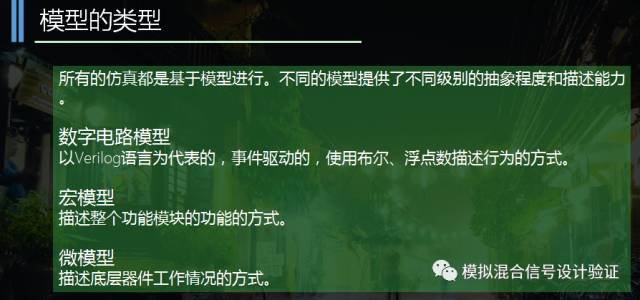

数字行为模型用于描述数字电路;以及模拟电路的功能,如使用wreal或者System Verilog。

宏模型用于简化模块,描述模拟电路的功能和性能。实践中设计者多使用VerilogA。有时候提供spice类的模型。

微模型从器件层次描述单元的功能和性能。基本上都是使用spice/spectre模型。

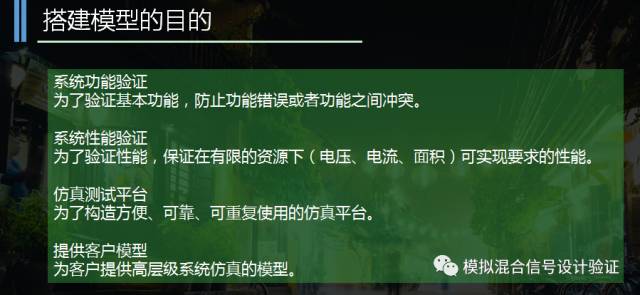

使用数字行为模型,进行基本的功能验证。

使用宏模型和微模型进行性能验证。

使用混合信号模型搭建测试仿真平台。

客户需要的模型多种多样。基本是从IC设计中的模型转化而来。

这里只涉及芯片设计阶段的仿真验证。

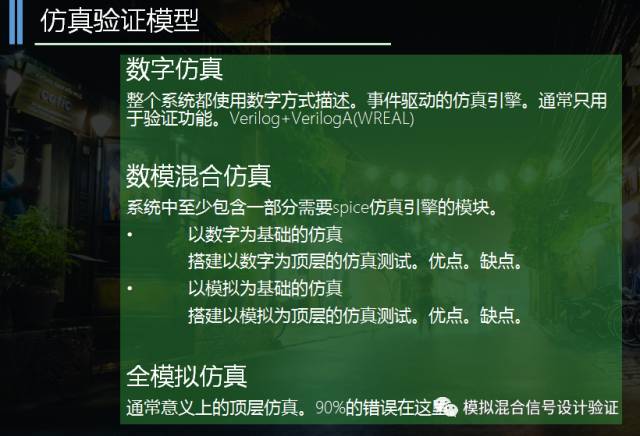

数字行为模型的仿真验证一般在设计初期进行,通常只用于验证系统功能,提高验证覆盖率。而且有待于后期使用混合信号仿真进一步验证。

数模混合模型的仿真验证在设计中与电路设计同步进行。可以使用数字顶层的架构,有利于批量仿真进行功能验证。缺点是配置复杂,模拟电路设计师对数字的设置和配置可能不是很熟悉。

如果采用模拟顶层的方式优点是直观,便于电路的调试,内部修改比较容易。缺点是批量仿真比较难,需要额外的仿真测试平台模型支持。

全模拟仿真,在顶层使用微模型进行仿真。最耗时间也最能够体现真实的功能和性能。通常这里最能够体现实际问题。

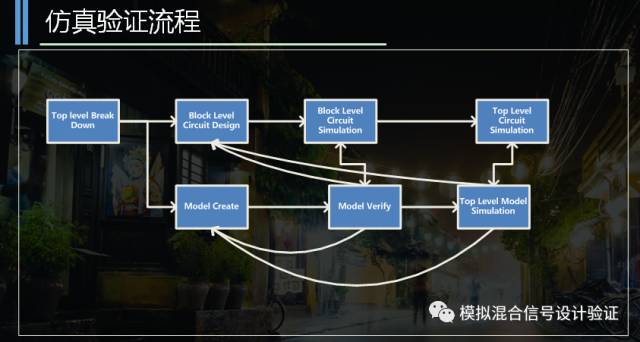

仿真验证流程如上图。大致思路是:模型先于电路;模型和电路要互相对比验证;模型要体现电路的实现方法;多次迭代进行。

搭建任何一种模型都对工程师的能力有相应的要求。能力不足可能写出错误的模型,或者掩盖了真实的问题,或者消耗过多的设计时间。

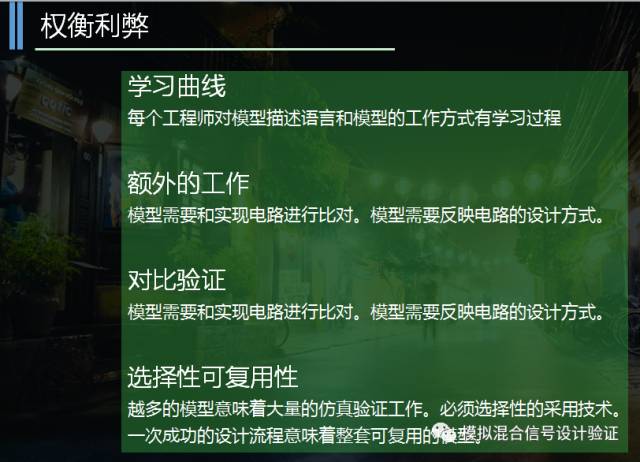

采用任何一种建模方式都意味着额外的设计时间。在消耗的时间和不使用这种技术带来的风险之间要权衡利弊。并不是使用了越多的技术就能带来越好的结果。

模型和电路要迭代对比验证。模型要反映电路的实际实现方法。

选择了一种建模技术后,要考虑可复用性。尽量在模块阶段搭建可复用的模型,为将来的/其他人的项目节省时间。

-

数模混合电路仿真实现2025-01-21 391

-

Cadence混合信号仿真教程.zip2022-12-30 708

-

MATLAB与控制系统仿真实践(第3版)源码2022-09-05 1289

-

HFSS的6个微波电路仿真实例模型资料免费下载2020-05-07 2767

-

PSpice 仿真实践2020-01-20 6822

-

Altium Designer的混合电路信号仿真工具介绍2019-07-19 1872

-

信号混合放大电路仿真2016-03-23 651

-

【MSP430趣谈】系列教程汇总贴2016-02-20 35014

-

MATLAB信号处理仿真实验代码包2013-09-23 1317

-

PSpice教程:PSpice仿真实践2013-04-07 2196

-

军事仿真实体可视化模型系统关键技术2009-04-14 958

-

PSpice仿真实践2006-03-12 10414

全部0条评论

快来发表一下你的评论吧 !