关于DRAM市场趋势的“虚假谎言

存储技术

描述

DRAM制造技术世代进入10nm世代(不到20nm世代)已经过去五年了。过去五年,DRAM技术和产品格局发生了巨大变化。因此,我们将总结和更新DRAM产品、发展和技术趋势。尽管如此,过去 20 年来 DRAM 的定位发生了显着变化。为此,在本专栏的前一篇中,我们回顾了从公元 2000 年到 2010 年代初的 DRAM 技术,作为基础知识的“回顾”。参考文章《DRAM,何去?何从?》

这次我们将介绍2010年代末至2020年代初的DRAM发展趋势。从技术节点来看,对应29nm代(2Xnm代)到12nm代(1β代)。将其应用到ISSCC国际会议上公布的DRAM原型芯片的技术节点上,29nm到25nm节点将于2014年,25nm节点于2016年,21nm到20nm节点于2017年,22nm到18nm节点于2018年, 2019年从22nm到18nm节点,小型化从1Xnm节点进展到1Ynm节点,2020年又进展到1Ynm节点。

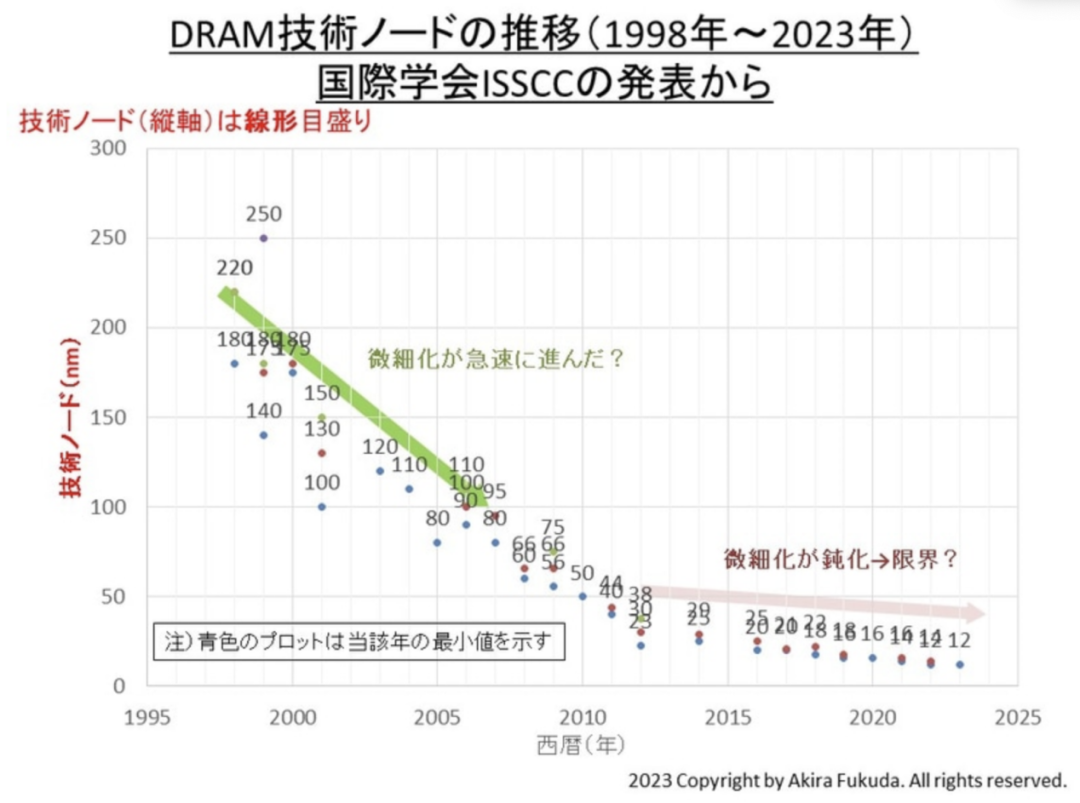

DRAM 技术节点过渡(1998-2023)。纵轴是技术节点(线性比例),横轴是出版年份

DRAM的发展趋势包括“处理尺寸的小型化”、“存储器密度的增加”、“存储容量的增加”和“数据传输速度(输入/输出速度)的增加”。他还将谈到一些媒体中关于趋势的“虚假(或误解)”。

审视DRAM 正在“达到小型化极限”的说法

在半导体逻辑的研发中,“小型化的极限”一直被人们谈论。正如上次提到的,尖端逻辑MOS FET的加工尺寸已不再与技术节点值相匹配,可以说晶体管的小型化已经达到了极限。那么DRAM的小型化又如何呢?

开头的图表总结了 1998 年至 2023 年国际会议 ISSCC 上提出的 DRAM 原型硅芯片的制造技术节点(换句话说,25 年来的趋势)。该图纵轴显示技术节点,横轴显示出版年份。该图显示,虽然从1998年到2010年小型化进展迅速,但自2010年以来进展不大。由此可见,“2010年代以来DRAM小型化已接近极限”的说法成立。

然而,这个说法却包含着一个严重的陷阱。原因是纵轴上的技术节点是“线性尺度”的。

滥用线性图,忽视“比例缩减定律(缩放定律)”

比例缩减定律(也称为缩放定律、登纳德缩放定律或登纳德定律)已成为半导体研发中的半常识。1974年,IBM的Robert H. Dennard和他的同事在IEEE期刊上发表了一个理论,解释了根据比例因子“k”减小MOS FET尺寸的好处,并进行了计算。

从结论粗略地得出比例定律,如果MOSFET栅极尺寸(栅极长度和栅极宽度)减小到1/k,则延迟时间将减小到1/k,功耗将减小到1/ k. 下降到 的 1/2。这是一个梦幻般的理论,理论上,只需将设备做得更小,就可以同时实现更快的速度和更低的功耗。而且,从 20 世纪 70 年代到 90 年代的 MOS FET 和集成电路的发展一般都遵循这种比例定律。实际使用的“k”约为1.4,或者换句话说,“1/k”约为0.7。

DRAM 的尺寸在 20 世纪 70 年代到 90 年代推动了小型化,并根据该比例因子 (1.4) 进行了缩小。当然,也有细微的偏差,但在大约三年的时间里,下一代产品——加工尺寸缩小了0.7倍的大容量DRAM被开发出来。3年的0.7倍意味着6年后的0.49,即0.7的平方,这意味着尺寸将减半。

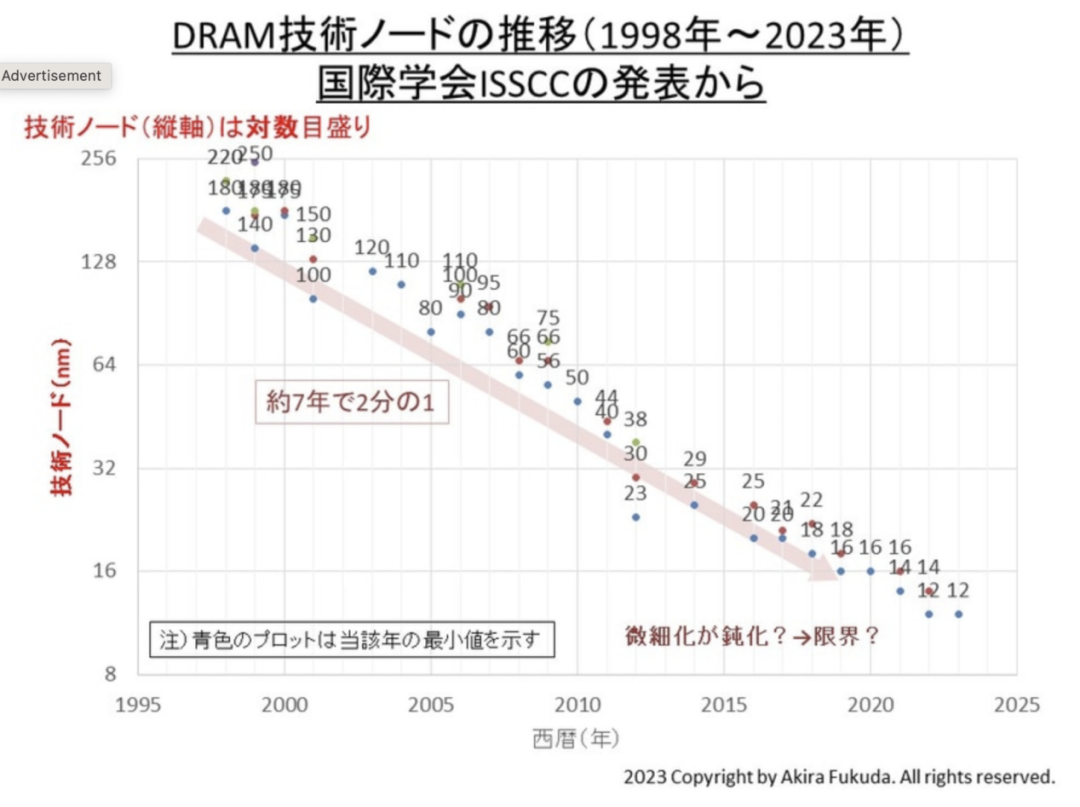

我想再次向大家展示一张图表,总结了 1998 年至 2023 年 ISSCC 上公布的 DRAM 制造技术节点(即 25 年来的趋势)。该图纵轴显示技术节点,横轴显示出版年份。然而,纵轴已更改为对数刻度。

DRAM 技术节点过渡(1998-2023)。纵轴为技术节点(对数刻度),横轴为发表年份。

当我将垂直轴更改为对数刻度时,图表看起来完全不同。25年来,DRAM技术节点继续以几乎恒定的速度小型化,“每七年缩小一半(年率0.906倍)”。虽然没有1998年之前实现的“六年左右减半(年率0.891倍)”那么快,但小型化的速度显然保持在恒定的速度。从该图中可以看出,没有任何限制的迹象(除了现实之外)。

比例归约律是通过维度相乘建立的。这不是加法。对数图是准确显示因乘法(或除法)而变化的物理量的趋势的图。在这种情况下引入“线性图”(即加法图)本身就可以被视为一种愤怒。

验证“自 2010 年代末以来内存密度的提高进展迅速”的理论

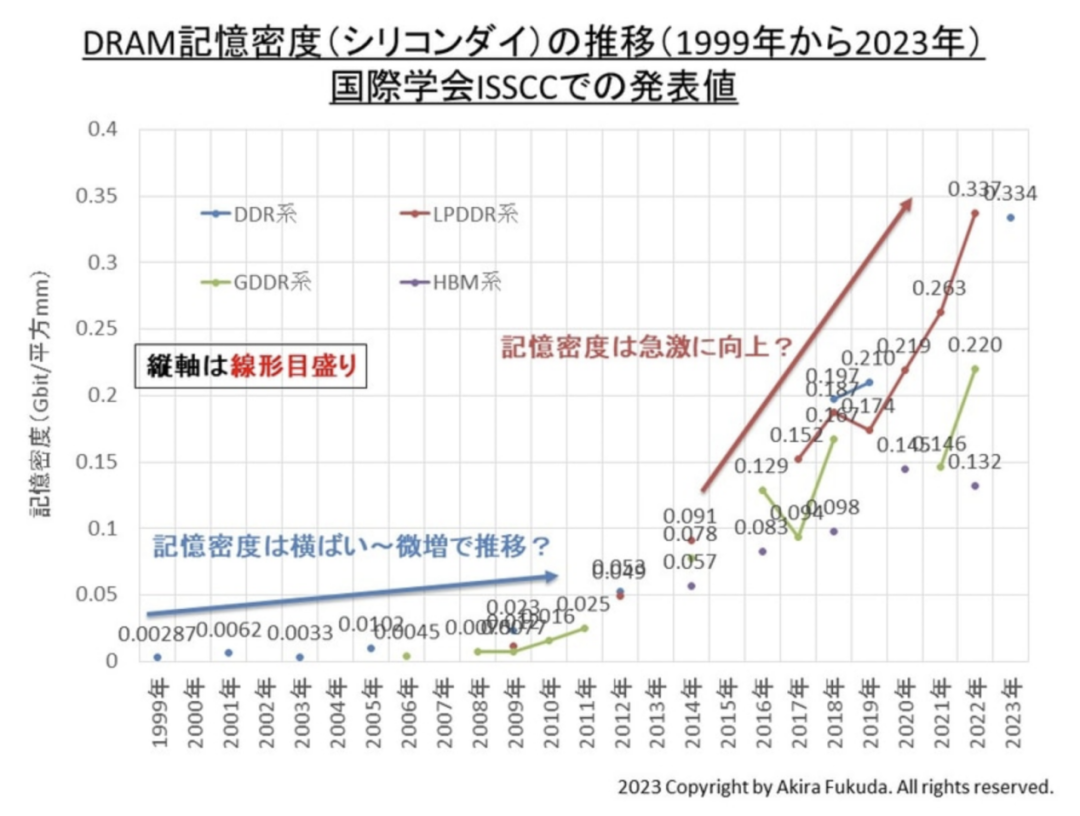

在围绕记忆密度增加趋势的讨论中也可以看到类似的愤怒或虚假叙述。下面是在国际会议 ISSCC 上展示的 1999 年至 2023 年 DRAM 原型硅芯片存储密度的图表。垂直轴(存储密度)采用线性刻度。

从1999年到2010年,存储密度(Gbit/mm2)保持不变或略有增加。但自2014年以来,这一数字一直在快速增长。因此,DRAM硅芯片的存储密度“自2010年代中期以来迅速提高”的说法似乎是正确的......

DRAM 存储密度的变化(每个硅芯片)(1999-2023 年)。纵轴是存储密度(线性刻度),

由于以线性比例绘制内存密度,这种说法也被误解了。这是因为晶体管尺寸减半意味着其面积减少四分之一。面积按尺寸的平方减小。当然。因此,原则上,如果尺寸减半,存储密度会增加四倍。

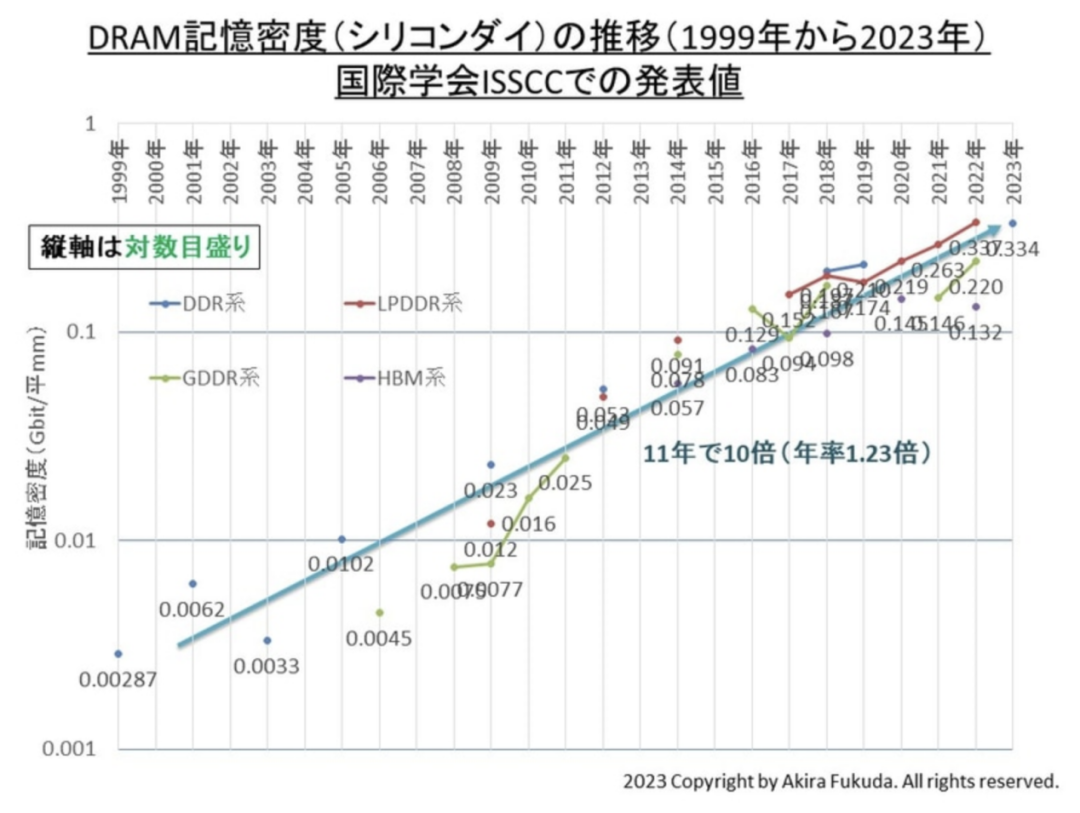

存储密度也基本上由乘法决定。不能说在那里引入线性图是正确的。对数图是合适的。如果换成对数图,您会看到与以前完全不同的视图。从1999年到2023年,存储密度将“在11年内以10倍的恒定速度提高(每年1.23倍)”。自2014年以来,存储密度的增长速度与以前相同。

DRAM 存储密度的变化(每个硅芯片)(1999-2023 年)。纵轴是存储密度(对数刻度),横轴是出版年份。

年增长率1.23倍意味着存储密度将在6.7年内翻两番。可以看出,这与“七年减半”的小型化趋势非常契合(原则上七年内存密度翻两番)。

2010 年代末最大存储容量再次扩大

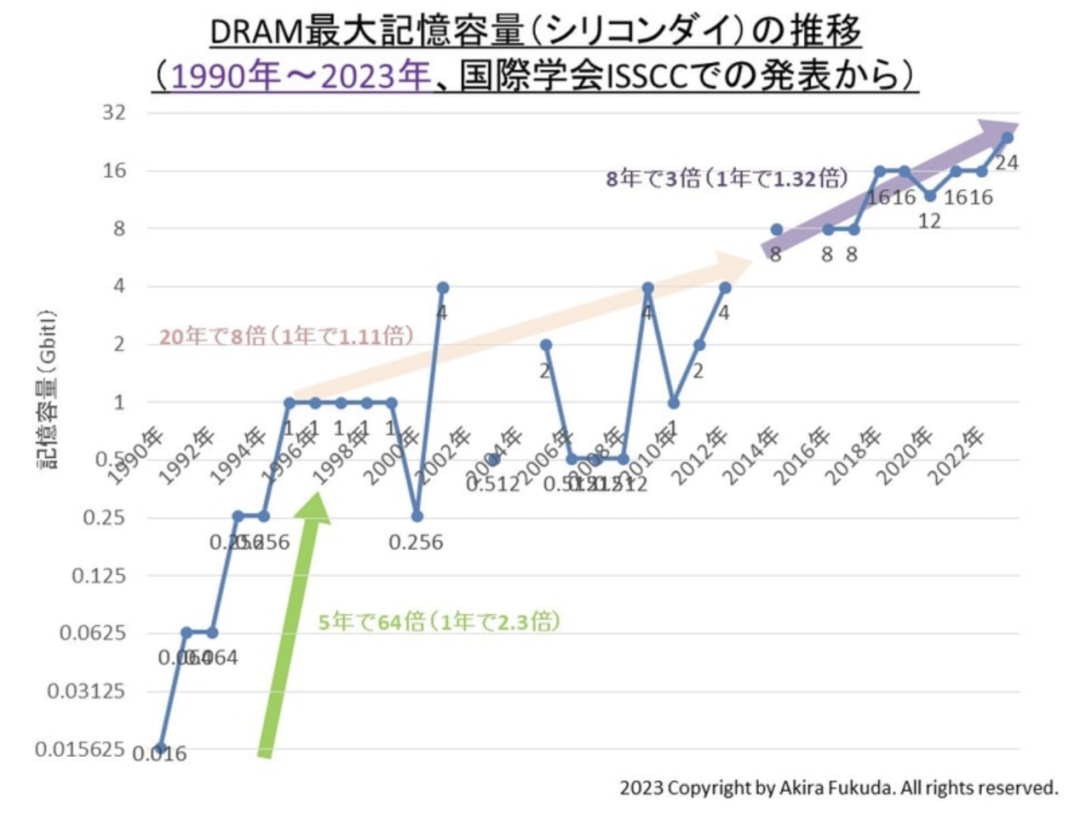

接下来是每个硅芯片的最大存储容量(我不会在这里讨论错误的理论)。正如上次提到的,DRAM的存储容量在2000年代停止了大幅增长。1995年至2014年ISSCC公布的最大存储容量在20年间放缓至8倍,即每年1.11倍。顺便说一下,“3年4倍”就是年化1.59倍。

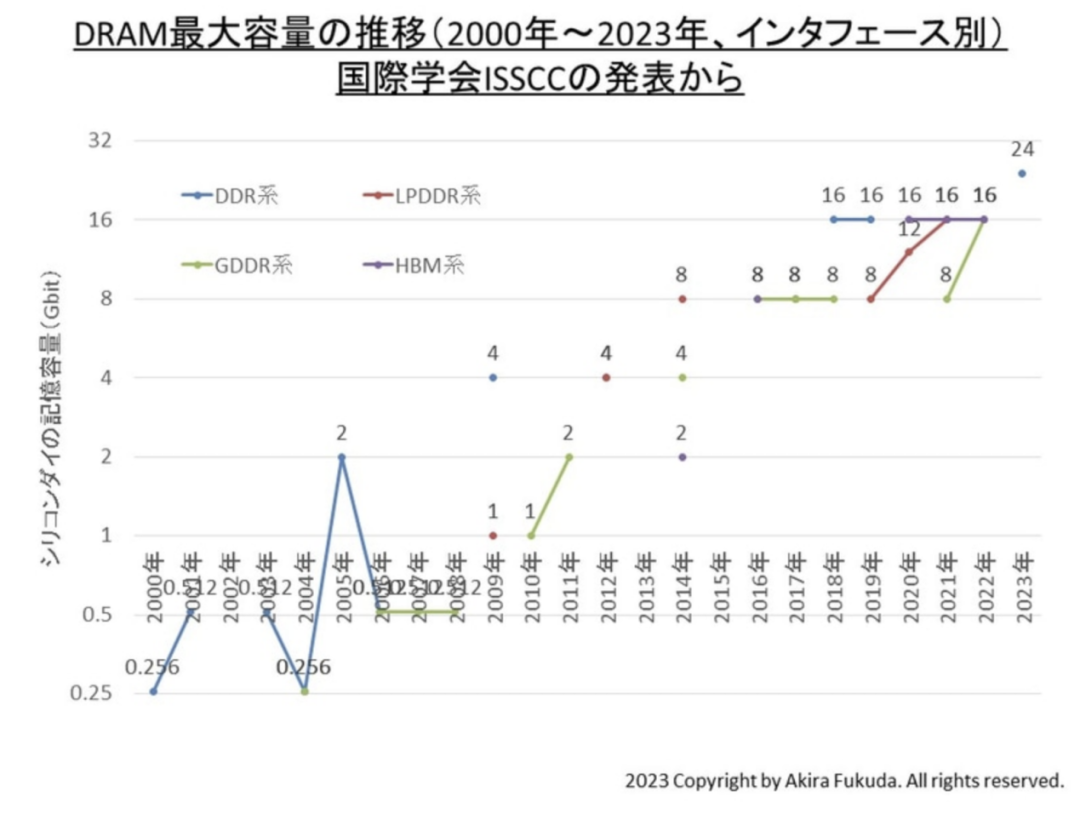

然而,2010年代末,存储容量再次开始扩大。2014年至2023年的最大存储容量在八年间增加了两倍,每年增加1.32倍。纵观各个接口系列,可以看出DDR和LPDDR系统正在推动容量的增加。DDR类型似乎反映了数据中心(服务器)对更大容量主存储器不断增长的需求,而LPDDR类型则反映了高端智能手机对更大容量主存储器不断增长的需求。

DRAM 存储容量趋势(每个硅芯片)(1990-2023 年)

为每个接口系列绘制的 DRAM 存储容量(每个硅芯片)趋势(2000-2023 年)

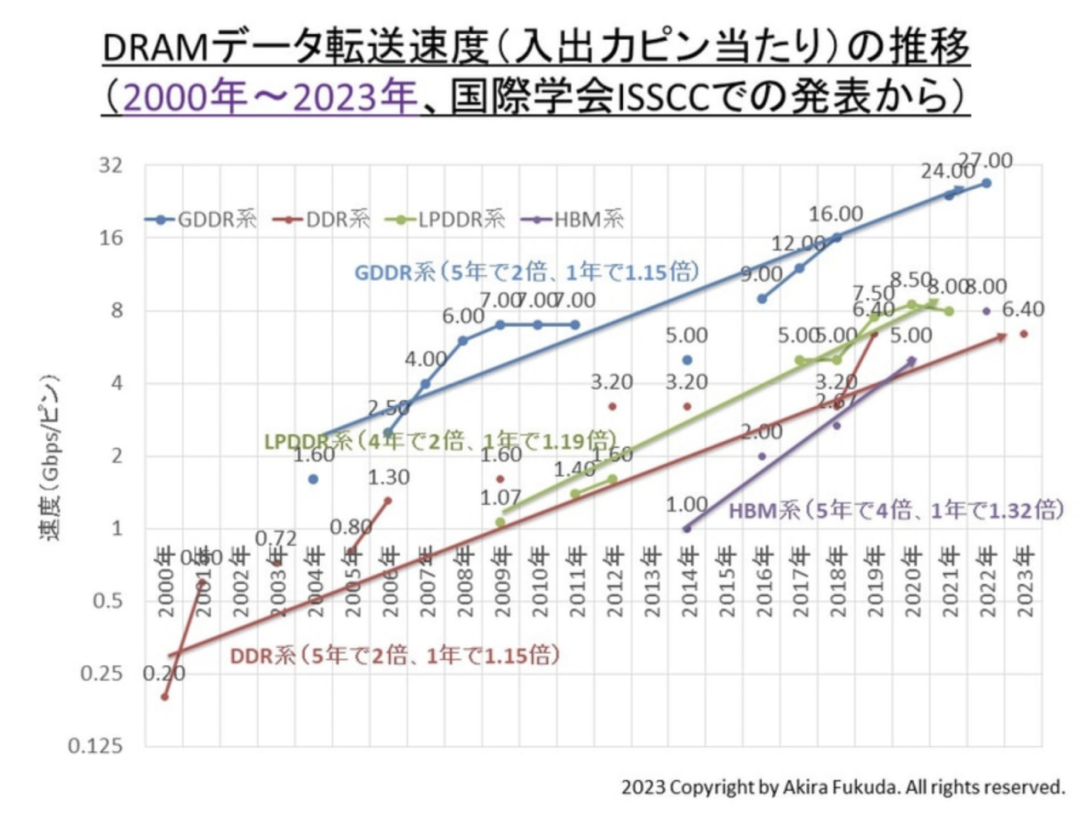

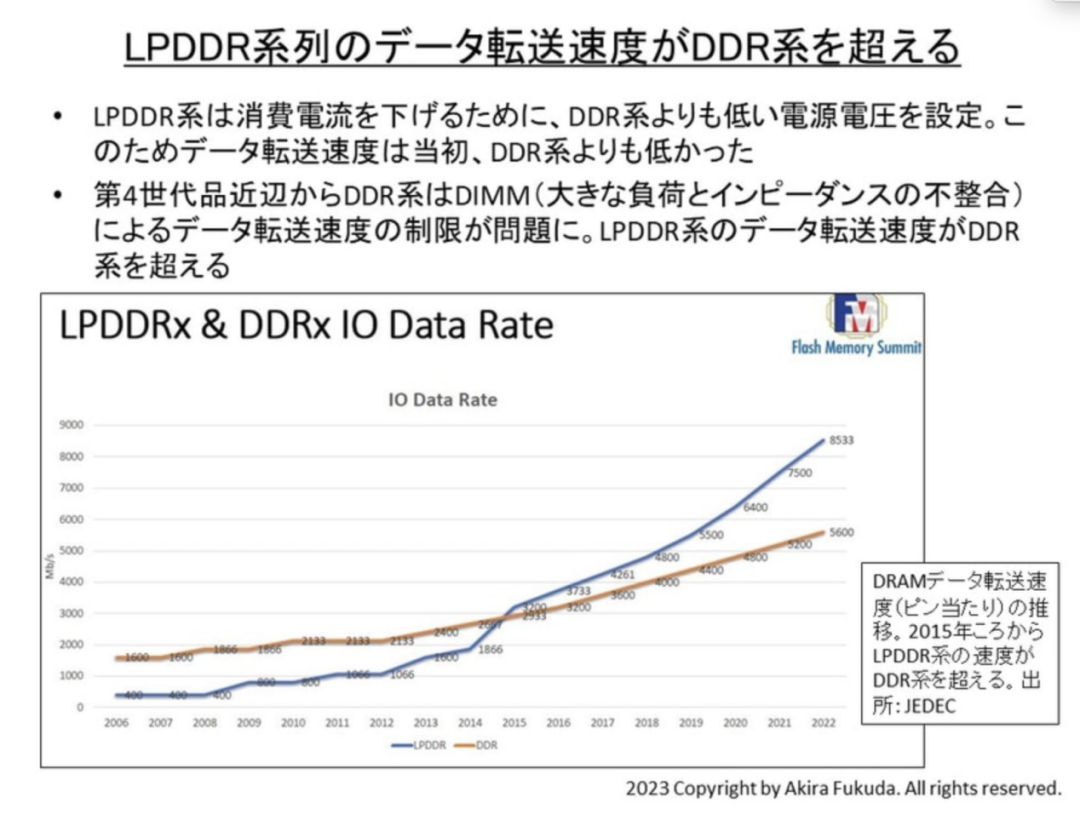

LPDDR系统在数据输入/输出速度上超越DDR系统

接下来是数据输入/输出速度(数据传输速度)。自 ISSCC 发布以来,绘制了 2000 年至 2023 年每引脚的速度(Gbps/引脚)。DRAM 数据传输速度根据接口系列的不同而有很大差异。速度最快的是GDDR系统,比其他接口系统快3到4倍。HBM 系统是最慢的。HBM系统的设计理念与其他接口不同。降低电路时钟以减少电流消耗,并将输入/输出引脚数量增加至1,024个以提高数据传输速度(带宽)。

绘制了每个接口系列 (2000-2023) 的 DRAM 数据传输速度变化

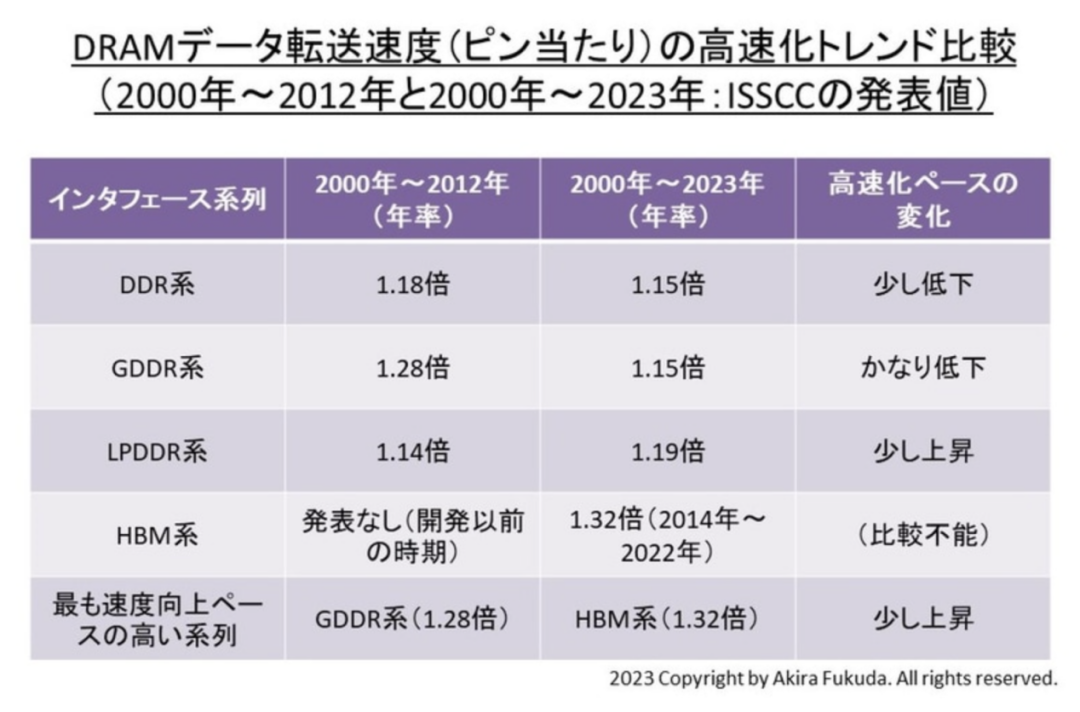

比较2000-2012年和2000-2023年每个接口系列的每引脚速度,趋势存在一些差异。从2000年到2012年,速度提升速度最快的是GDDR系统,以年化1.28倍的速度持续提升。接下来是年增长率为1.18倍的DDR系统,其次是年增长率为1.14倍的LPDDR系统。截至 2012 年,HBM 系统仍在开发中,尚未在 ISSCC 上公布。

从2000年到2023年,HBM系统的速度提升速度最快。HBM 芯片于 2014 年在 ISSCC 上首次发布。从此时起到2022年,速度以年化1.32倍的相当高的速度增长。另一方面,GDDR系统的速度增长明显放缓,2000年至2023年的年增长率为1.15倍。按年计算,DDR 系统也失去了一些动力。另一方面,LPDDR系统略微提高了速度。

DRAM 数据传输速度(每个引脚)增加的趋势(“2000-2012”和“2000-2023”之间的比较)

DDR 和 LPDDR 系统之间的数据传输速度发生了逆转。当LPDDR系统在2000年代末投入实际使用时,其数据传输速度低于DDR系统。由于LPDDR系统降低了电源电压并使用多种技术来抑制电流消耗,因此数据传输速度较低是正常的。不过,此后LPDDR系统的速度提升速度比DDR系统更快。结果,数据传输速度在 2010 年代中期发生逆转,并且差距从 2010 年代末开始扩大。

LPDDR 系列和 DDR 系列的数据传输速度(每个引脚)的变化。2016年,LPDDR系统的速度超过了DDR系统。此后,差距扩大。

根据接口系列的不同,发展重点分为高速和大容量。

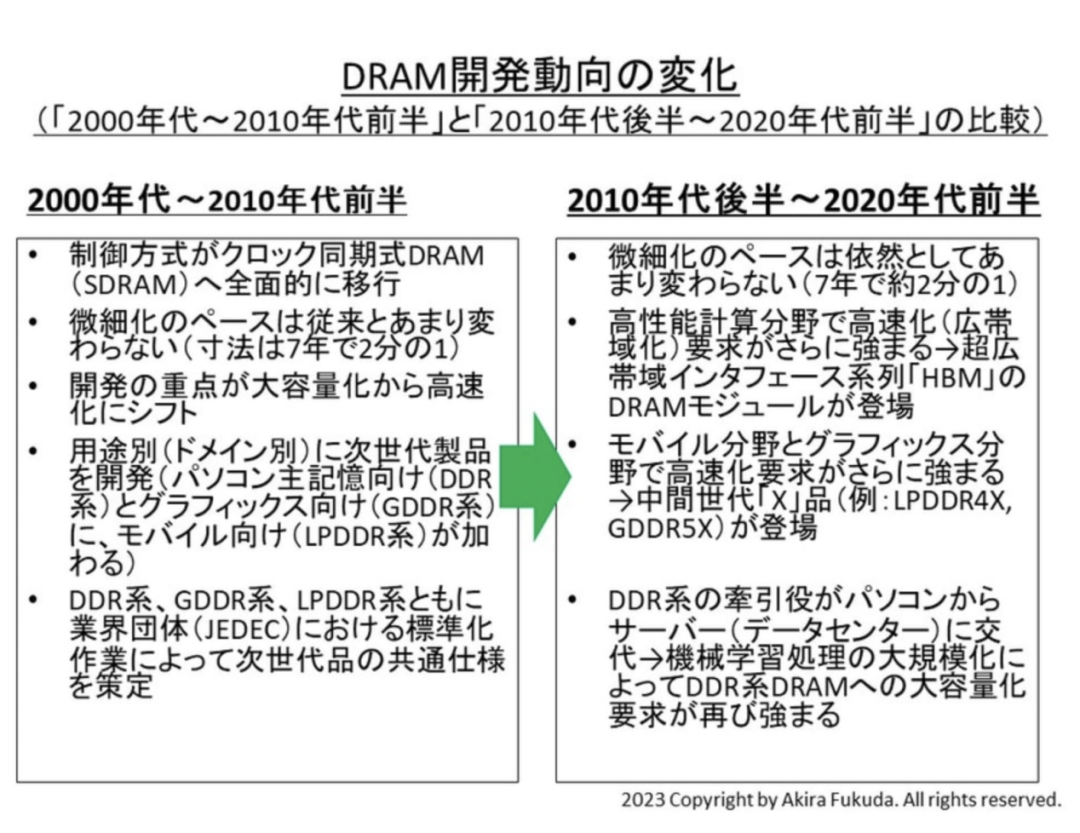

这是一个总结。我们比较了 2000 年代至 2010 年代初以及 2010 年代末至 2020 年代初的 DRAM 发展趋势。以下是 2010 年代末至 2020 年代初趋势的简要说明。

对更高速度的需求不断增长,导致 HBM 模块的超高速版本商业化。目前尚不清楚这是否是一种反应,但 GDDR 系统的速度提升有所放缓。

DRAM发展趋势变化(2000年代至2010年代初、2010年代末至2020年代初比较)

DDR 系统的大容量已经复苏。其背景是机器学习(大规模学习)的革命性演变突然增加了对更大主存容量的需求。数据中心和服务器处理的数据量的增加似乎也起到了一定作用。

最值得注意的是,DRAM小型化的步伐保持不变。加工尺寸(换算为有源区域的半节距)减小的速度在大约七年内减半。我想关注10nm代以后是否还能保持这个速度。

编辑:黄飞

-

利基DRAM市场趋势2025-06-07 4072

-

电子采购供应市场趋势展望峰会,获供应商管理调查报告2011-02-11 2169

-

汽车电子市场趋势2019-07-16 4081

-

2019年中国IT市场趋势热点介绍2020-07-13 1698

-

十大MCU供应商排名 MCU市场趋势2009-03-18 3589

-

2016汽车照明最新技术、产业及市场趋势2016-09-26 1676

-

2015年十大安防市场趋势2016-12-19 868

-

英特尔投资和未来大数据市场趋势2018-11-09 2671

-

一文看懂PCB的市场趋势2019-10-17 4157

-

汽车电子产品市场趋势2021-03-21 967

-

边缘计算的优缺点及市场趋势2021-06-23 2264

-

BMS芯片市场趋势和主要技术壁垒是什么2022-07-29 5815

-

浅析电子线束的市场趋势和机遇2022-12-01 2765

-

信号集成滑环的技术特点与市场趋势分析2025-02-06 727

-

数据采集器的市场趋势与前景2024-11-28 1336

全部0条评论

快来发表一下你的评论吧 !