浅析DRAM测试和检查设计方案

存储技术

描述

随着对缺陷和工艺可变性的日益关注,DRAM制造商继续要求具有成本效益的筛选和工艺改进解决方案,但随着更快接口和多芯片封装的推出,满足这一需求变得更加困难。

动态随机存取存储器在各种电子设备中扮演着重要角色,从电话和个人电脑到汽车中的ECU和超大规模数据中心内的服务器。同样,它也是AI/ML中的一个必要组件,其中需要处理和存储的数据量正在快速增长。曾经简单的内存现在是一整个系列的选项,从廉价到具有更快读/写操作事务的高容量dram(512 GB到1TB)。

不过,DRAM也有一些独特的挑战。尽管这种存储器的成本历来很低,但对质量和可靠性的需求却在不断增长,尤其是在安全和任务关键型应用中。这与位单元的持续缩小不一致,这使得它们更容易受到缺陷和工艺可变性的影响。虽然自我修复和错误检测代码(ECC)方案可以解决制造缺陷,但工程团队仍然依赖检查和电气测试来完成繁重的工作。

质量和RAS(可靠性、可访问性和可维护性)预期因应用而异。根据内存和处理之间的数据量和传输速度,数据速率和接口有很大不同。这高带宽存储器(HBM)接口增加了它自己的复杂程度,因为它使DRAMs能够从电路板和DIMM插槽迁移到2.5D和3D封装。

的内存和系统工程高级主管Tadashi Oda表示:“DRAM行业一直在改进其内存产品线,以适应多样化的应用Advantest America。“起初,DRAM只是计算机的一种类型。但今天,应用范围从PC、服务器、移动/平板,到IoT、AI/ML、汽车。结果,我们有了DDR、LPDDR、GDDR和HBM。每个DRAM都有独特的技术挑战,我们预计会有越来越多的细分和挑战。”

晶片检测和过程控制

当在最接近缺陷和工艺变化发生的工艺步骤捕获有意义的数据时,新DRAMs的产量上升是最有效的。产量、工艺和器件工程师依靠晶圆生产过程中的检测来筛选缺陷并提供工艺可变性的反馈。此外,工程团队通过将工艺变化或缺陷与来自晶片的位图故障联系起来,测量晶片制造期间的关键器件电参数。

更高的缺陷水平是DRAM单元不断缩小的直接结果。Neumonda首席执行官Peter p CHMüller解释说:“现代DRAM技术使用带有堆叠电容器的掩埋字线结构,其中字线位于硅表面下方,以减少短沟道效应。在制造过程中会出现许多影响DRAM性能的缺陷,这是存储器制造商通常要测试的。一个例子是蚀刻过程中的污染,其中颗粒会阻碍光刻或蚀刻过程。缺陷的另一个来源是晶片中的污染。如果晶片被污染,铜或其他离子会在晶片内移动,并导致诸如可变保留时间的影响。当然,制造工艺本身存在变化,导致隔离层厚度的边际效应,这会导致存储器的电容耦合变化。晶片晶格中的缺陷会导致DRAM单元机制中的暂时或永久泄漏

更高的采样率,可以高达100%,有助于更快地发现缺陷。这在汽车等行业尤为重要,在这些行业中,客户对极高质量的要求——少至十亿分之十(ppb)——也推动了更高的检测率。

“总的来说,检测率实际上取决于晶圆/组装制造的工艺步骤和目的,”的产品营销经理Nathan Peng说创新。例如,对于前端光刻后检查(开发后检查,或ADI ),检查步骤不一定需要100%取样。如果客户希望在光刻过程中监控工艺偏差,采样可能相对较低,尤其是对于成熟节点。另一方面,对于出货质量保证等过程步骤,100%抽样是必须的,因为其目的是为了出货晶圆质量控制,根据缺陷率要求决定接受或拒绝晶圆或芯片。”

器件和成品率工程师早在FEOL时就使用电气测试来深入了解工艺变化。“参数测试是一种测量电气特性(阈值电压、开/关电流、电容等)的检查。的晶圆测试解决方案营销经理Yasuhiko Iguchi说道是德科技。“随着DRAM工艺节点的进步和NAND堆叠层数的增加,关键存储元件的设计余量不断缩小。由于这种收缩,存储器件变得容易受到影响保持力、性能或可靠性工艺变化的影响。使用基本存储电路元件的电测试的过程控制监控在晶片生产中变得更加重要,用于检查那些基本元件的电特性的变化。典型地,在晶片上制造晶体管层(在线)和在晶片上制造接触焊盘(生产线末端)之后进行测试

晶圆测试后,产量工程师使用故障DRAM单元的位图来锁定可能的缺陷源。该位图来自所有测试的通过/失败数据的光栅化。

Onto Innovation软件产品管理总监Mike McIntyre表示:“内建自测(BiST)仍然是创建最适合在单元级别将线内缺陷与器件影响相匹配的内存结果的基础和黄金标准。当与位图模式分类器结合使用时,BiST使器件工程师能够真正了解器件在倾斜时的灵敏度

制造测试要求

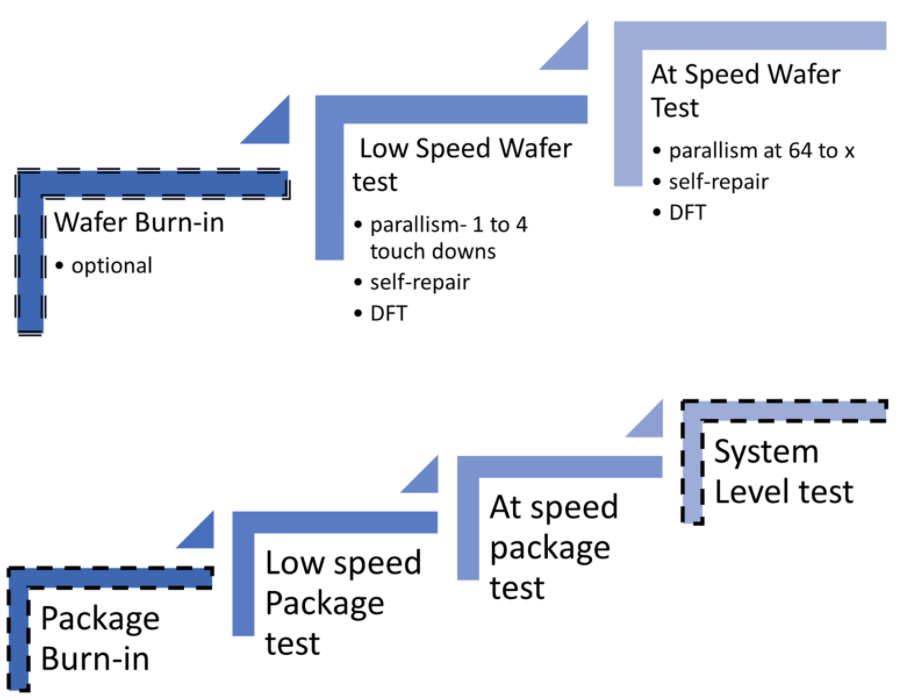

DRAM测试发生在晶圆探针和封装测试。最终组装的封装、终端系统要求和成本考虑推动了测试流程,包括ATE要求和相关测试内容。

工程师使用两个插件来管理巨大DRAM阵列的长测试时间和高速接口的要求。在第一种情况下,所有的内存测试算法都以较低的速度应用。对于第二个芯片(也称为已知良好的芯片),使用芯片的高速接口,并以运行速度运行内存测试算法。这两种插入在晶片测试期间执行,并且对于封装测试可以重复这两种插入。

“晶圆测试以大约100MHz的相对较低的频率进行,以识别薄弱的单元,然后修复它们。出于成本原因,平行度需要很高,并且通过每个晶片大约四次触地来实现,”Neumonda的p CHMüller说。“这需要具有20,000根针和每根针2.5g的高成本探针卡。它给每个晶片增加了大约50公斤的高压。KGD测试需要更高速的阵列和后端全速测试,这需要通过探针卡来执行。这需要低并行度和高速探针卡。出于这个原因,KGD通常不支持最高速度的等级。”

老化过程可用于加速可靠性相关的缺陷发现,在切换电路信号的同时向DRAM施加高温和高电压。晶圆级老化和封装级老化系统均可用。在某些情况下,可以添加系统级测试,在其中测试实际工作负载。

晶圆级老化有几个原因。一是提高用于3D封装的DRAM芯片的可靠性。卖威化是另一个原因。Advantest的Oda表示:“一些DRAM厂商将DRAM作为晶圆出售,而不是封装。”“然后,买家包装和测试DRAM。在这种情况下,DRAM厂商应该保证晶圆级质量。他们无法进行封装老化,因此需要在发送给客户之前在晶圆上进行。”

晶圆级测试和老化(WLTBI)使内存供应商能够对晶圆上的所有芯片施加压力,以识别边缘和故障单元。这使得能够去除婴儿死亡率芯片,以提高多芯片/异质模块产量。模块是通过使用几种不同的技术构建的,如微处理器、内存、硅光子学等。其中每种技术都需要不同的电压、时间和温度应力要求,这只能在特定技术的晶圆上完成。此外,WLTBI期间对存储器的散热要求也在不断提高,密度和频率的增加推动了对晶圆散热能力的需求,也推动了系统供应商提供更高的性能。“

图1:两个DRAM测试流程,可选步骤用虚线突出显示。资料来源:a 。 Meixner/半导体工程

记忆有什么不同

存储器ATE系统在几个方面不同于逻辑ATE系统。首先,有模式生成和自我修复的需求。

Advantest的Oda表示:“主要区别在于,针对内存的ATE解决方案需要配备APG(算法模式生成器)和故障捕获内存(或错误捕获RAM)来存储故障信息和访问。“在晶圆分类中,存储器修复的失效分析是必须的,也是工艺反馈的关键。运行中的内存修复分析是非常高的计算能力,ATE硬件可访问性是密集的。”

高速接口是第二个区别。英特尔战略业务开发总监Ken Lanier表示:“对于包括内存控制器在内的SoC设备,高速I/O故障可通过集成DFT功能解决太达因。“这意味着SoC测试人员不再受限于内存I/O速率。一个10岁的SoC测试人员可能会很好地测试带有DDR5接口的处理器。另一方面,内存测试人员仍然必须进行全速测试,以保证某个部件全速运行,包括极其苛刻的计时测试。存储器ATE还必须在极高的测试点数下进行,以抵消较大存储器的较长测试时间的影响。这给ATE设计人员带来了巨大的挑战,他们需要开发专门的测试仪电子设备,以难以置信的高集成度实现这种高速能力。这也意味着新的内存标准推动了对新测试设备的需求,因此设备的使用寿命变得更短。”

DRAM测试内容地址范围很广,针对测试刷新能力、单元泄漏和解决单元故障的一长串模式,有许多特定于存储器的模式。其中许多需要来自相邻位单元的特定数据。[1]例如,臭名昭著的行锤测试强调位单元在连续读取后保持其数据的能力。[2]如前所述,分别对存储器性能和接口性能进行高速测试,检查操作时序规格(如tAC、tRCD)和I/O时序规格(如tVB、tVA)。

“DRAM需要大量使用内部测试,我喜欢称之为‘秘密测试模式’,”Neumonda的p CHMüller说。这些是专有的,用于在测试过程中实现高并行性,例如,通过将多个I/O压缩为单个I/O。或者,可以将定时参数修改为比自然操作更关键的值,以找到弱内存单元

虽然一些晶圆缺陷/故障机制与逻辑技术中的类似,但可靠位存储的本质需要一些额外的关注。由于DRAM单元的密度,对缺陷的敏感性非常高。如果每个失败的位单元、行或列都被标记为失败,则产品产量将会很低。几十年前,这些现实促使设计工程师增加备用行和列,以及在测试期间执行修复的相关方法。在晶圆级,可以通过激光或电熔断(e-fuse)进行修复,但在封装级只能进行e-fuse。误差校正码(ECC)电路可以在制造测试和系统使用期间管理单位故障。用于修复的芯片面积可以是总面积的5%到10%。

同时,为了降低成本,在晶片和封装测试中都采用了并行测试。“因为内存是商品,测试成本才是王道,”小田说。“因此,DRAM使用大规模并行。对于晶圆测试,技术趋势是一次触地(1TD)。NAND 1TD在几年前变得很常见,DRAM 1TD也成为一种迫在眉睫的需求。为了实现这一点,ATE需要组装许多引脚电子器件和设备电源。Advantest开发了一种新的创新型测试单元,通过将ATE和处理器集成在一个紧凑的单元中,提高了每给定占地面积的并行性。”

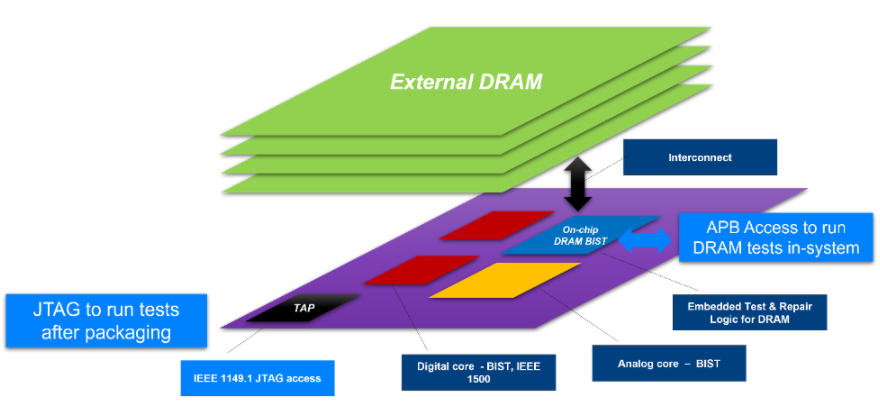

DRAM测试不可能没有测试设计(DFT),其中可编程存储器阿拉伯学者发动机是最重要的。通过提供运行大量内存测试算法的能力,它使工程团队能够在设备生命周期的每个阶段权衡测试时间和测试覆盖率。作为一个IP模块,内存BiST还需要适应各种DRAM I/O接口,无论是LPDDR、DDR、GDDR还是HBM。其中每一种都有不同的延迟、数据速率和协议。其他DFT方案支持老化测试插入,并允许使用I/O压缩进行并行测试。为了找到薄弱的存储单元,DFT改变内部DRAM时序。DFT支持存储器阵列自修复和HBM通道修复。

DRAM修复主要是根据制造测试标准进行的。在过去十年中,JEDEC DRAM标准定义了封装后修复(PPR ),它为每个存储体提供一行修复。[3]标准化方法能够在启动时进行修复。

“DRAM可编程测试引擎很少提供给最终用户,”Faisal Goriawalla说,他是新思科技。“随着可靠性和油田内部作业相关要求的增加,这种情况正在发生变化。随着寿命的延长,服务器中DRAM的任何现场更换都将非常昂贵。DRAM厂商现在提供系统可用冗余,称为封装后修复(PPR)。JEDEC已经为DRAM厂商标准化了这种封装后修复。系统制造商希望在他们的SOC中部署这些解决方案,以利用DRAM中的备用容量,并提高现场可靠性。”

多芯片封装中DRAM面临的挑战

无论是在2.5 D封装中连接到计算SOC的DRAM,还是在3D封装中使用HBM的堆叠式DRAM,产量和测试工程师都需要解决单芯片DRAM部件之外的其他挑战。有些是DRAMs独有的,而有些则不是。

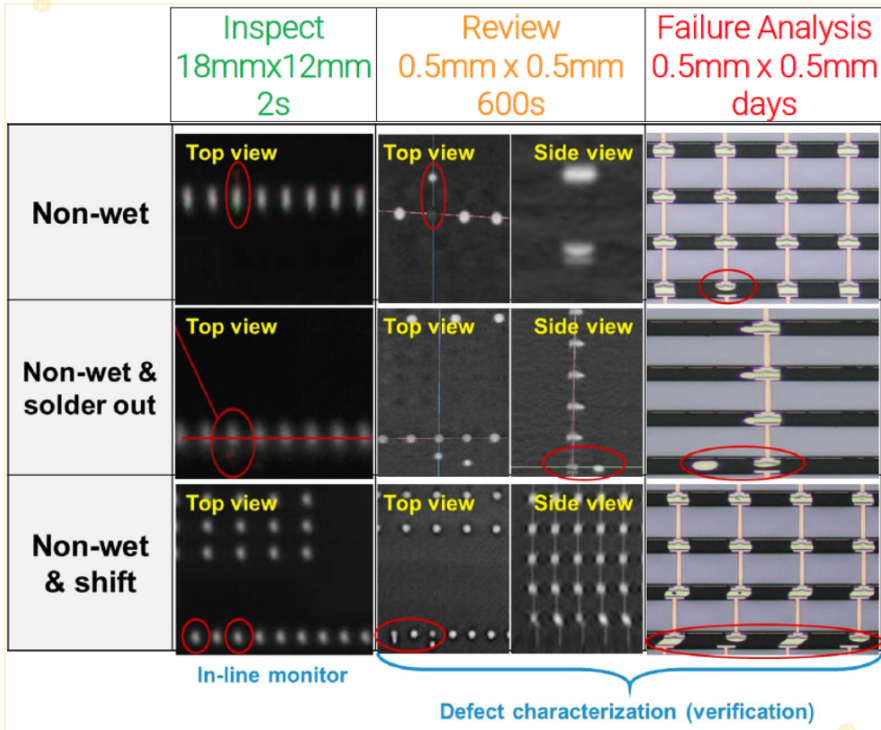

现代DRAM间距尺寸和高微凸块数量给检查和测试都带来了挑战。

“多芯片封装产品需要更多的2D/3D检测和计量解决方案。对于多芯片封装,将有额外的互连步骤(扇出、微凸点、直接键合等)。芯片之间的额外互连需要更多的工艺步骤。扇出需要对断裂或桥接的RDL线进行缺陷检查。对于微凸点,需要CD和高度度量,以及凸点顶部的残余缺陷检测。对于直接粘接,需要进行检查以发现裂纹、空隙和分层。”

HBM接口以较低的功耗提供高得多的数据速率。它被设计为宽接口(1,024通道),用于2.5D和3D封装解决方案。然而,堆叠裸片的凸块间距大小和众多连接使得通道修复选项成为必需,以适应裸片之间的错误接合。随着芯片堆叠变得更深(范围从4到16),这个倍数增加。这需要特定的测试策略来发现故障通道并实现通道修复,这正是DFT所促进的。但是众所周知,由于不良的冶金接触,检查方法具有更高的筛选潜在缺陷结合的可能性。

硅通孔(tsv)和微凸块连接实现了堆叠HBM DRAM管芯。作为已知良好管芯预期的一部分,测试流程通常在管芯减薄步骤之前筛选有缺陷的tsv。然后,一旦所有堆叠的管芯之间的键合被连接,就可以对它们进行检查和测试。检查在评估焊接质量、芯片对准(重叠)和芯片翘曲方面发挥着重要作用。

“目前他们使用的是带焊帽的铜柱,”Frank Chen说,他是布鲁克。“随着间距缩小,它将逐渐过渡到混合键合。对于垂直堆叠,芯片放置精度对于监控和维护至关重要。过度移动会导致凸起拉伸和断开,从而导致不润湿。同样重要的是以粘合层厚度(BLT)测量的压缩。大BLT会导致不润湿,小BLT会导致焊料挤出。在某些情况下,焊料会被完全挤出,即不在焊盘区域内。”

图2:堆叠管芯微凸块键合缺陷识别和检查。来源:布鲁克

硬短路和开路故障最容易隔离。在部分或边缘债券的情况下,人们担心并非所有债券都会被识别出来。然而,其中一些连接最终会在现场失效。在这些情况下,详细的检查会有所帮助,但这并不容易。

“目前,在速度足够快、能够灵敏地区分各层并评估影响粘合的属性的工具方面存在一些差距,尤其是当您使用8层、12层或16层堆叠时。对于这些多层,随着管芯变得更薄,翘曲和对准成为问题。所有这些都需要监控,”陈指出。

将DRAM并入多芯片封装提高了测试和DFT的标准。

“在多芯片模块中,你会遇到与可测试性、可访问性和多芯片诊断相关的额外挑战,”Synopsys的Goriawalla说。此外,HBM也带来了挑战,因为您无法单独测试逻辑芯片和内存芯片。您必须一起测试这两者。您需要测试它们之间的互连。对于这种芯片堆栈,您需要能够访问它,这是IEEE标准1500所允许的。然后,当然,你的诊断需要区分和隔离,以进行物理故障分析。基于DRAM的引擎需要在逻辑小芯片上。它位于控制器和DFI总线主芯片上的PHY之间。在测试模式下,它控制PHY通过PHY运行读/写指令,以测试外部存储器和互连。”

图3:支持DRAM测试、诊断和修复的2.5D多管芯配置。来源:Synopsys

对于多芯片组件制造,可追溯性是实现操作反馈和芯片性能匹配的关键。

Onto的McIntyre表示:“一旦芯片被认为“可以使用”,确保多芯片模块(MCM)兼容性和监控版本控制的可追溯性和分析技术在内存和MCM中使用的任何其他组件类型之间通常是相同的。“最好的例子是使内存性能与封装中其他芯片的性能相匹配。这是必须的。将速度较慢的内存芯片放在高性能封装中的后果可能会导致整个封装的降级。这通常会导致较低的平均销售价格和盈利能力。另一个例子是将动态工作范围受到影响的内存放入一个封装中,该封装将部署在一个预期高度可变的环境中。”

摘要

由于成本的原因,许多观察家认为DRAM是一种商品。但是把所有的DRAM都放在同一个桶里是一种误解。内存性能对于一些最复杂的计算系统的整体性能至关重要。

但是,鉴于计算对兆兆字节数据和更快执行速度的需求不断扩大,DRAM向更密集的位单元和堆叠芯片实施的迁移正在使测试和检查变得复杂,随着更快的内存和更复杂的封装成为常态,这一问题只会变得更加难以解决。

审核编辑:黄飞

-

DRAM的矩阵存储电路设计方案2020-12-01 6674

-

DRAM原理 - 6.猝发模式与内存交错#DRAM原理EE_Voky 2022-06-28

-

【资料分享】stm32设计方案与示例分享第二波2014-03-12 4140

-

STM32设计方案与示例分享2018-09-03 3691

-

浅析DRAM和Nand flash2019-09-18 5455

-

DRAM 的EFA测试2020-11-13 3826

-

求一种DRAM控制器的设计方案2021-04-28 1662

-

求一款RFID读卡器测试系统的设计方案2021-05-11 1955

-

浅析DRAM供不应求因素2010-04-23 834

-

并网逆变器的设计方案2016-01-11 1221

-

基于基于Qt的集成电路测试软件设计方案2021-06-19 1075

-

嵌入式发动机活塞温度测试系统设计方案2021-06-22 1119

-

通用高可靠性航天器供配电测试设备的设计方案2021-06-25 1185

-

浅析ROHM的汽车照明解决方案2021-11-19 877

-

浅析LED电磁兼容解决方案2022-01-25 925

全部0条评论

快来发表一下你的评论吧 !