3D 封装与 3D 集成有何区别?

电子说

描述

作者:Paul McLellan,文章来源: Cadence楷登PCB及封装资源中心

今年3月,第 18 届国际设备封装会议和展览(简称 IMAPS,是主办方国际微电子组装与封装协会- International Microelectronics Assembly and Packaging Society的首字母缩写)顺利开幕。就在同一周,苹果发布了 M1 Ultra,使先进封装再次成为了科技新闻的关注焦点。M1 Ultra 由两个被中介层(或称之为互连桥)连接在一起的 M1 Max 芯片组成。中介层通常比在其之上的裸片更大,而互连桥则较小,并只位于连接处的裸片边缘之下。

在此次 IMAPS 会议上,Cadence 资深半导体封装管理总监 John Park 先生阐述了 3D 封装 与 3D 集成 的区别。

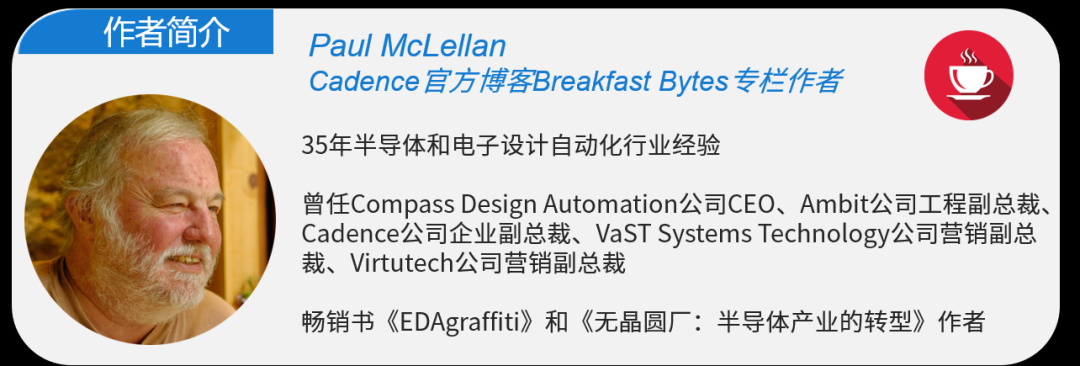

他首先指出,系统级封装 (即System-in-Package ,SiP) 有两个不同的方向。一是把 PCB 上的器件转移到多芯片组件;二是如同前几年制造大型系统级芯片(即System-on-Chip, SoC)一样进行集成,但是转换制程利用先进封装来封装裸片。

以下是一些使晶粒(Chiplet)解决方案具有吸引力的重要因素:

在为器件挑选最佳工艺节点方面具有很大的灵活性;特别是 SerDes I/O 和模拟核,不再需要“全部统一在单一”制程节点上

由于制造裸片尺寸小,所以良率会更高

使用现成的晶粒(Chiplet),可缩短 IC 的设计周期,并降低集成的复杂性

通过购买良品裸片(即known-good-die ,KGD),可普遍降低生产成本

在许多设计中使用同种晶粒(Chiplet)时,将具有如同采用批量生产的相同成本优势

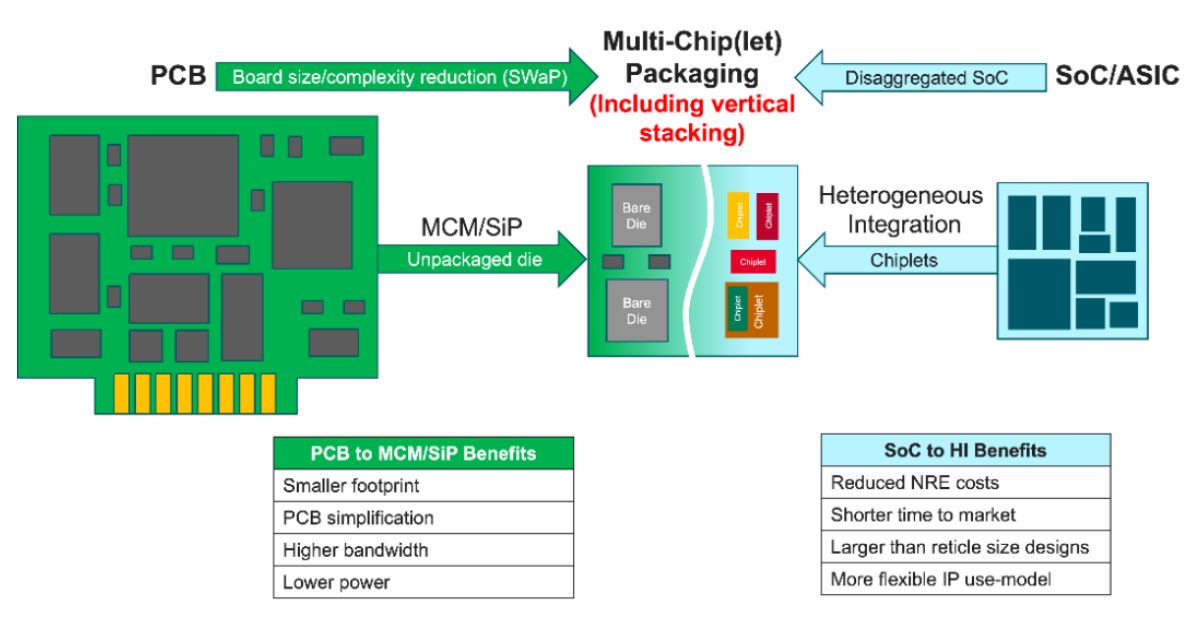

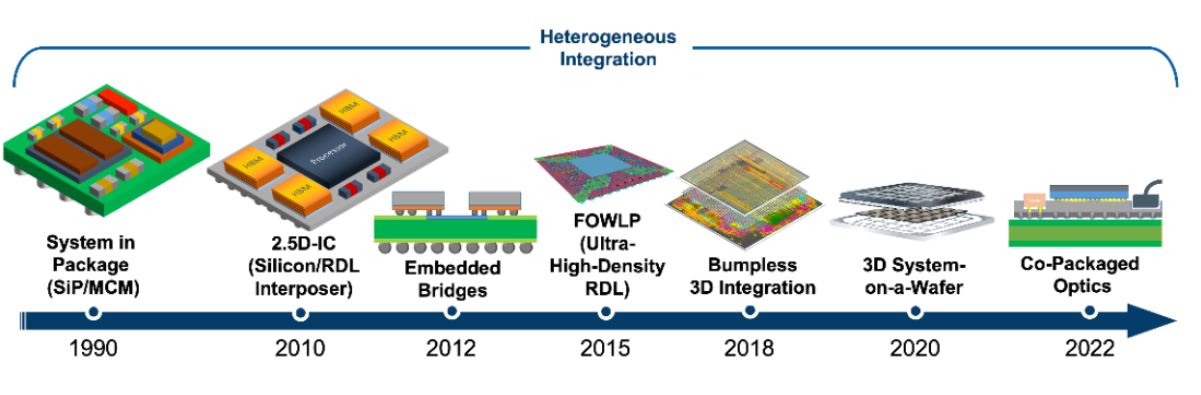

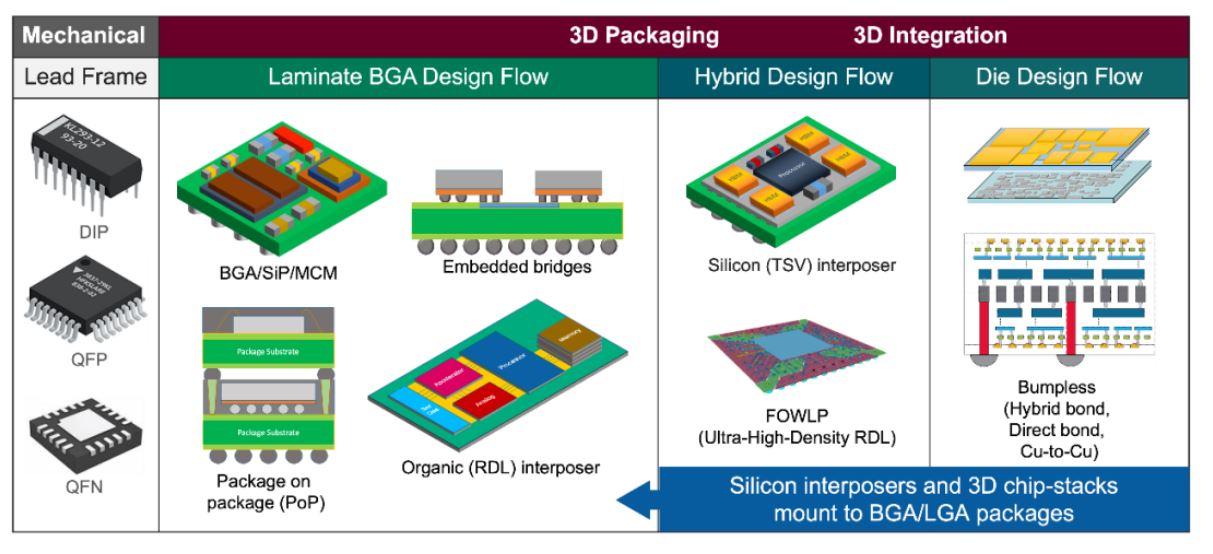

以 IC 为重心的先进封装改变了设计流程。上图中,20世纪90年代设计采用的是类似 PCB 的设计流程;而如今已采用类似 IC 的设计流程。把多种不同的技术集成到一起,即异构集成,结合了多年以来使用的各种制程技术。特别是先进封装和先进集成方法,例如晶圆堆叠(Wafer-on-Wafer)和无凸块集成(Bumpless)。

我们可以将基于封装的 3D 视为“后端 3D”,把先进集成方式视为“前端 3D”。

后端 3D是微型凸块互连(micro-bumped)加上每个裸片都有单独的时序签核和 I/O 缓冲器。这种方式中,多个裸片之间通常没有采用并行设计。多年来,这一直是用于存储器和 CMOS 图像传感器的常见方法。

对于前端 3D,裸片通常是直接键合的制程工艺(铜对铜,或采用类似方法)。裸片之间没有 I/O 缓冲器,这意味着并行设计和分析必不可少,需要时序驱动的布线和静态时序签核(对于数字设计而言)。所以设计将倾向于朝Z 轴上布局,多个裸片会堆叠在一起;这意味着随着设计的推进,一个特定的区域可能被分配给超过一个的裸片。

这是封装领域的下一个重要转变,也是向真正3D-IC 设计迈出的一大步,即将众多不同的裸片堆叠在一起,这能大大缩短信号所需的传输距离。当然,由此产生的散热问题也需要加以分析和管理,裸片上方的另一个裸片可能会阻绝散热,这取决于众多的设计细节。

持。

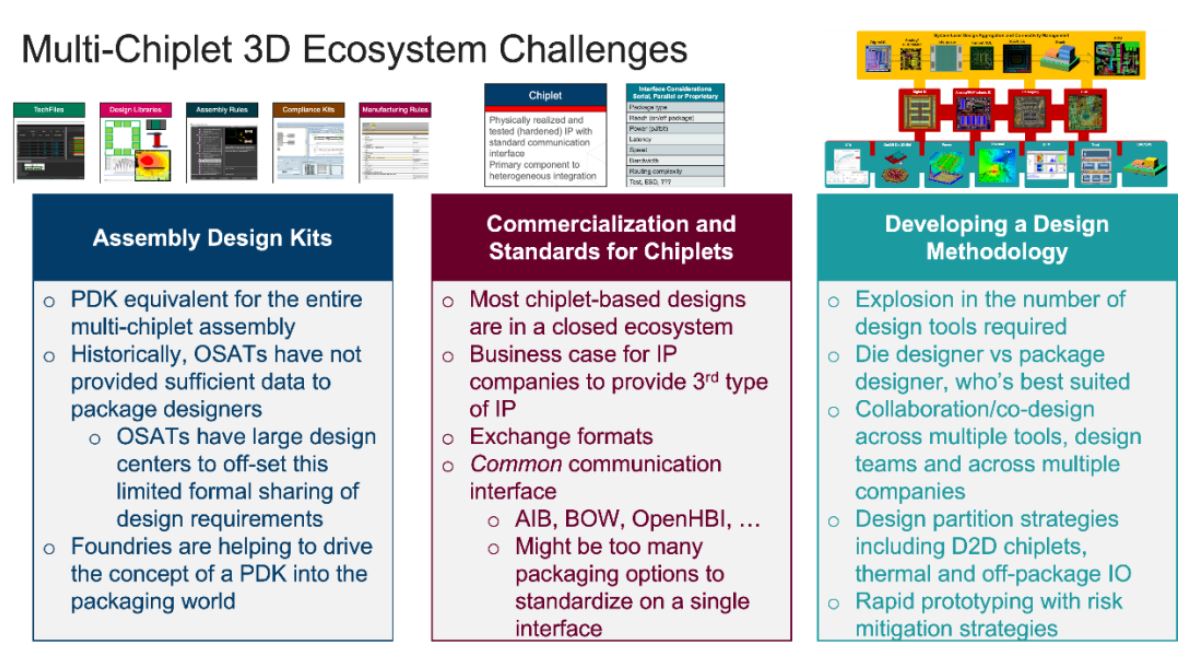

想要使这一新的设计生态成为现实,仍要面临诸多挑战,包括装配设计工具包(即Assembly Design Kits,ADK) 的可用性、裸片与裸片互连 (d2d) 的通用标准,以及 EDA 工具的全面支持。

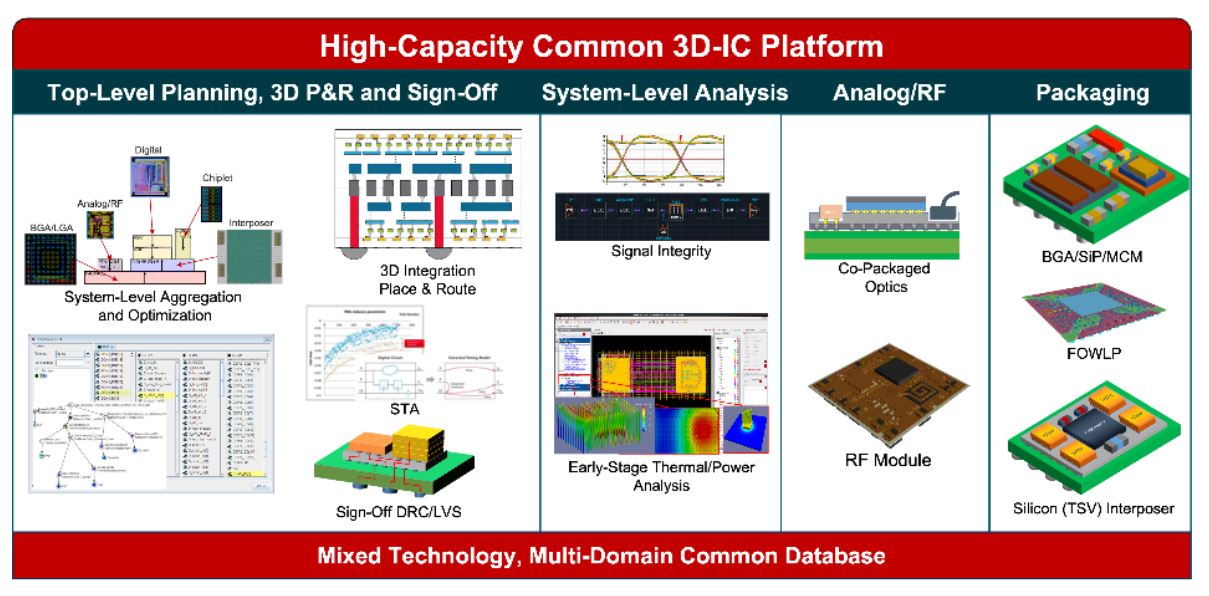

在打造支持这些制造流程的工具时,面临的一个挑战是设计规模可能非常庞大,具有超过 1,000 亿个采用了多种设计技术的晶体管。这就产生了对高容量、多领域、可进行多技术数据库相互沟通与转换的工具的需求,只有这样,我们才能拥有一个高弹性的通用 3D-IC 解决方案设计平台。

业界另一个关注领域是晶粒(chiplets )的销售模式。到目前为止,大多数晶粒(chiplets),除存储器外,都被设计成单一系统或一组系统的一部分。从长远来看,就像如今的封装元件一样,未来将会有纯裸片上市销售,也会有经销商(或新公司)销售来自多个制造商的裸片。随着晶粒(chiplets )之间的通信变得标准化,不仅仅是技术上具备挑战,商业模式上的挑战也会应运而生。让我们拭目以待吧!

审核编辑 黄宇

-

3D封装2013-06-22 11106

-

3D 模型封装2013-12-27 4343

-

3d封装2015-06-22 2868

-

3D PCB封装库2015-08-06 15249

-

带有3D的封装2015-11-27 4604

-

***集成库(原理,封装,3D)2018-08-05 6180

-

如何让AD在3D显示下去除3D封装的显示?2019-09-23 17181

-

AD16的3D封装库问题?2019-09-26 5057

-

浩辰3D的「3D打印」你会用吗?3D打印教程2021-05-27 8270

-

我国即将建立3D标准体系2010-02-03 793

-

3D元件封装库2016-03-21 2810

-

Altium Designer的LED 3D封装集成2019-06-26 2948

-

为什么选择3D,3D芯片设计要点分析2023-03-27 1276

-

3D影像因何而生2023-06-25 1418

-

当芯片变身 3D系统,3D异构集成面临哪些挑战2023-11-24 2321

全部0条评论

快来发表一下你的评论吧 !