使用SiC MOSFET时如何尽量降低电磁干扰和开关损耗

电子说

描述

对于一直在设法提高效率和功率密度并同时维持系统简单性的功率设计师而言,碳化硅(SiC)MOSFET的高开关速度、高额定电压和小RDS(on)使得它们具有十分高的吸引力。然而,由于高开关速度会导致高漏源电压(VDS)峰值和长振铃期,它们会产生电磁干扰,尤其是在电流大时。本文提供了一个较好的解决方案来优化电磁干扰和效率之间的平衡。这种方法已经采用1200V 40mOhm器件进行了双脉冲测试验证。

了解VDS峰值和振铃

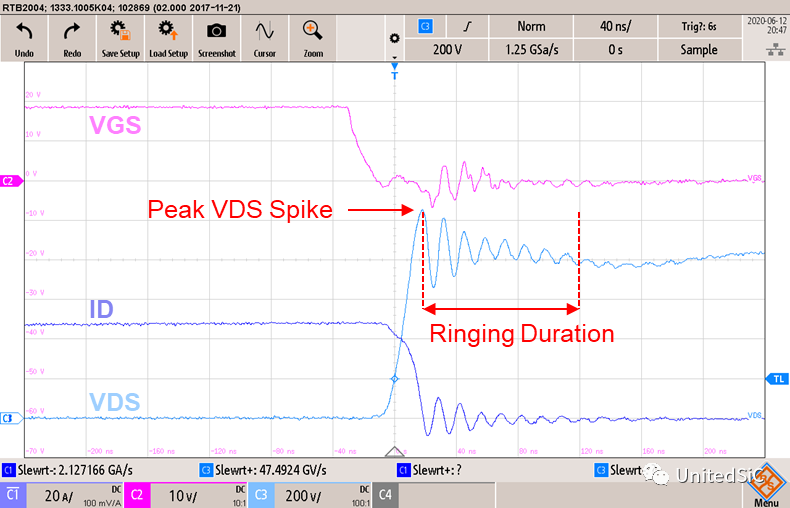

寄生电感是SiC MOSFET的VDS峰值和振铃的主要成因。从关闭波形(图1)中看,栅源电压(VGS)从18V至0V。关闭时的漏极电流(ID)为50A,VDS为800V。SiC MOSFET的高开关速度会导致高VDS峰值和长振铃期。该峰值降低了器件的设计余量以应对照明条件或负载突变,而长振铃期则带来的电磁干扰。在大电流下,这种情况更加明显。

图1.使用SiC MOSFET时在关闭情况下的VDS峰值和振铃(1200V,40mOhm)

常见电磁干扰抑制技术

传统的电磁干扰抑制方法是使用大栅极电阻(RG)降低电流流经器件的速度(dI/dt)。但是大RG会显著增加开关损耗,要在效率和电磁干扰之间进行权衡取舍。

另一种抑制电磁干扰的方法是降低功率回路杂散电感。要实现这一目的,需要更改电路板的布局,还需要使用体积较小、电感较低的封装。然而,尽量降低功率回路的效果是有限的,而且还需要遵守最小空隙和间隔方面的安全规定。使用较小的封装也会影响热性能。

可以使用过滤器来帮助达到电磁干扰要求,简化系统权衡。频率抖动等控制技术也能降低供电导致的电磁干扰噪音。

使用RC缓冲电路

采用简单的RC缓冲电路是一种更为有效和高效的方法。它能控制VDS峰值并缩短振铃期,同时实现更高的效率和可以忽略的关闭延迟。由于更快的dv/dt和额外的电容器,缓冲电路会有更高的位移电流,而这会降低关闭过渡期间的ID和VDS交叠。

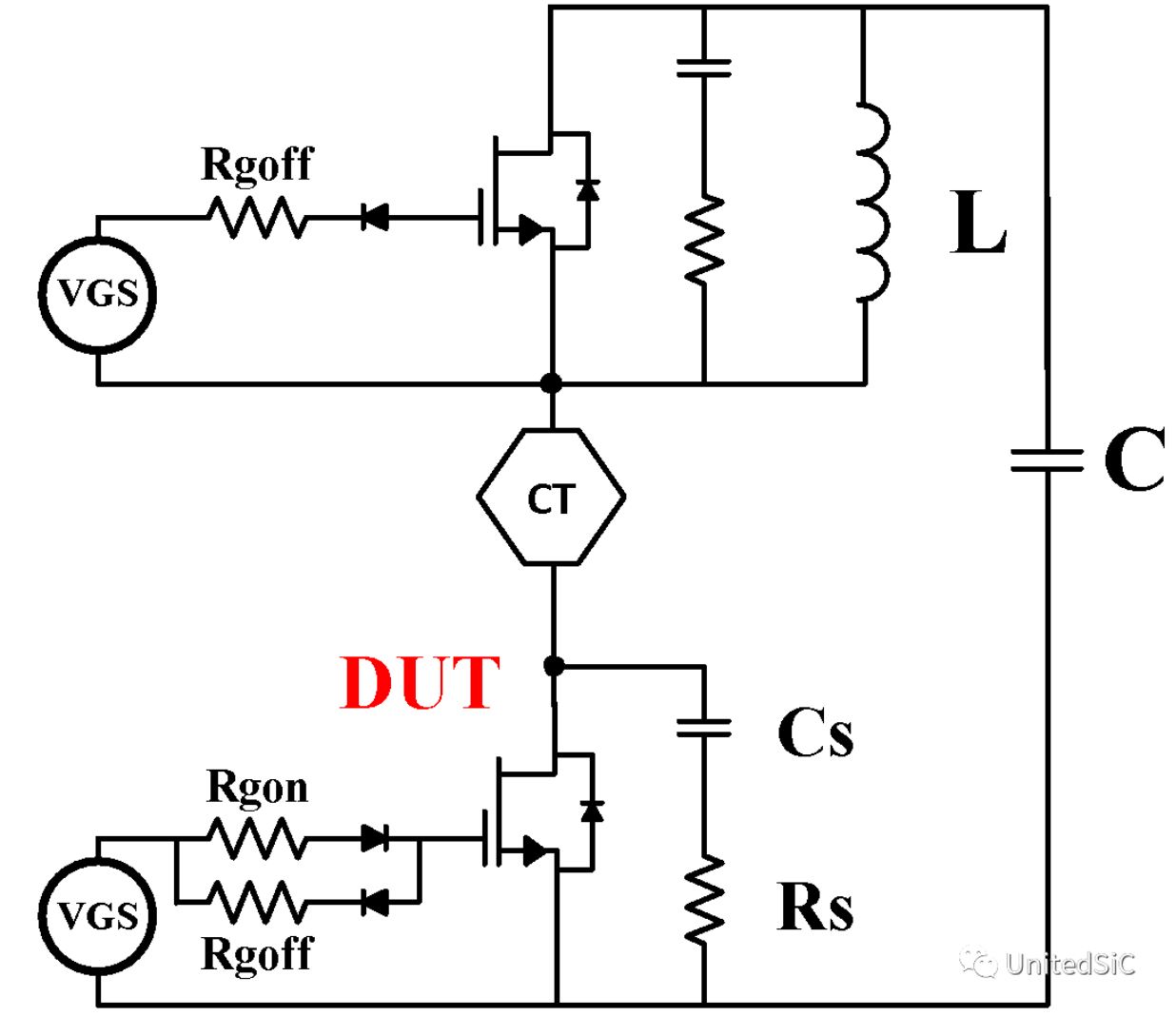

双脉冲测试(DPT)证实了RC缓冲电路的效果。它采用有电感负载的半桥配置。桥的高侧和低侧采用相同的器件,在低侧测量VGS、VDS和ID(图2)。电流变换器(CT)测量器件和缓冲电路电流。因此,测量的总开关损耗包含器件损耗和缓冲电路损耗。

图2.半桥配置(顶部和底部器件相同)

RC缓冲电路由一个简单的200pF电容器和10Ω电阻串联而成,跨SiC MOSFET的漏极和源极连接。

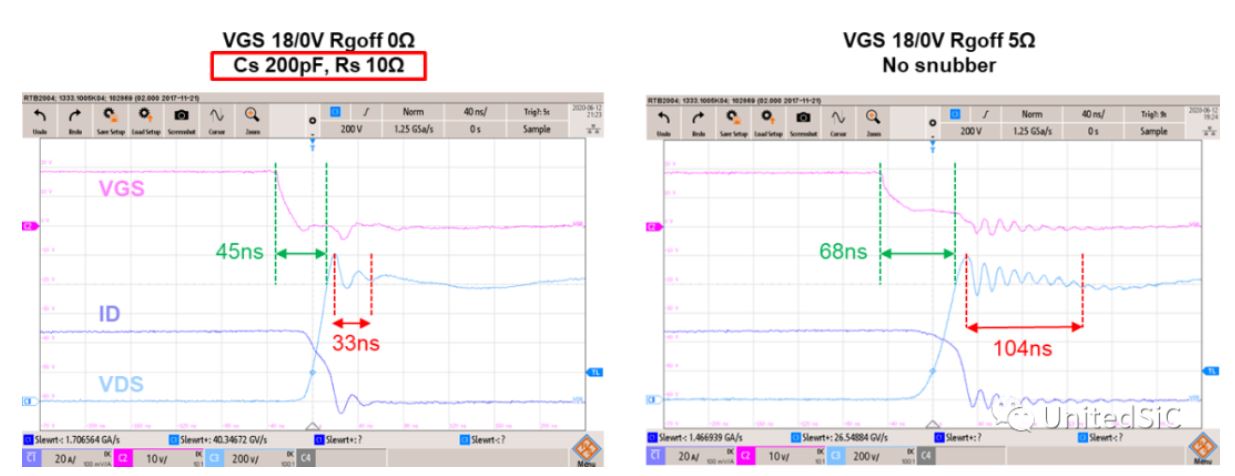

图3. RC缓冲电路(左)能比大RG(右)更有效地控制电磁干扰

图3比较了图1中的同一个器件的关闭情况。左侧波形采用含小RG(off)的缓冲电路,而右侧波形采用大RG(off)且无缓冲电路。两种方法都限制了关闭峰值漏源电压VDS。然而,由于将振铃期降低至仅33ns,缓冲电路更加高效,延迟时间也更短。

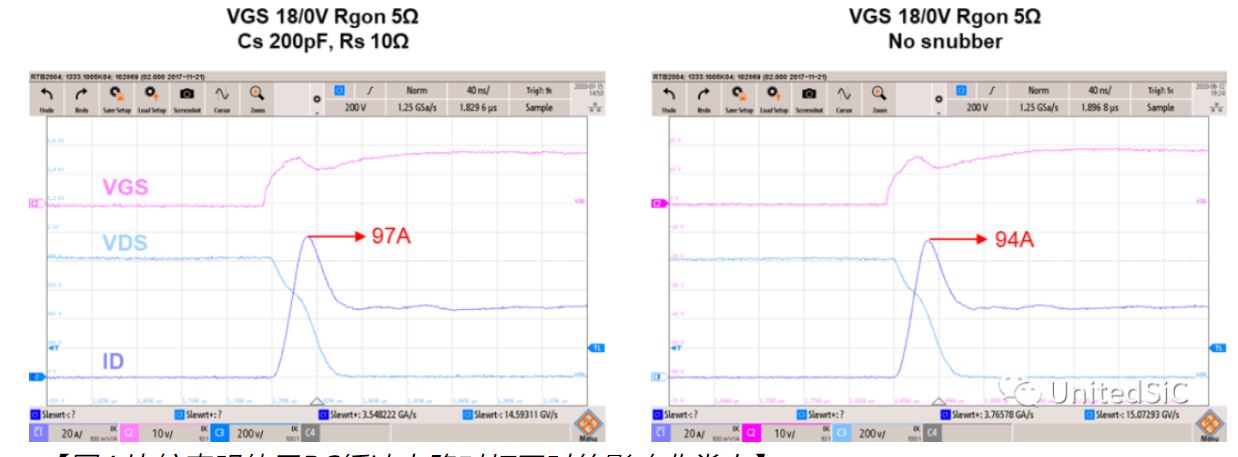

图4.比较表明使用RC缓冲电路对打开时的影响非常小

图4比较了在采用5Ω的RG(on)时,有RC缓冲电路(左)和没有缓冲电路时的波形。采用RC缓冲电路时的打开波形有一个峰值略高的反向恢复电流(Irr),但是没有其他显著区别。

RC缓冲电路能比大RG(off)更有效地控制VDS的峰值和振铃期,但是它会影响效率吗?

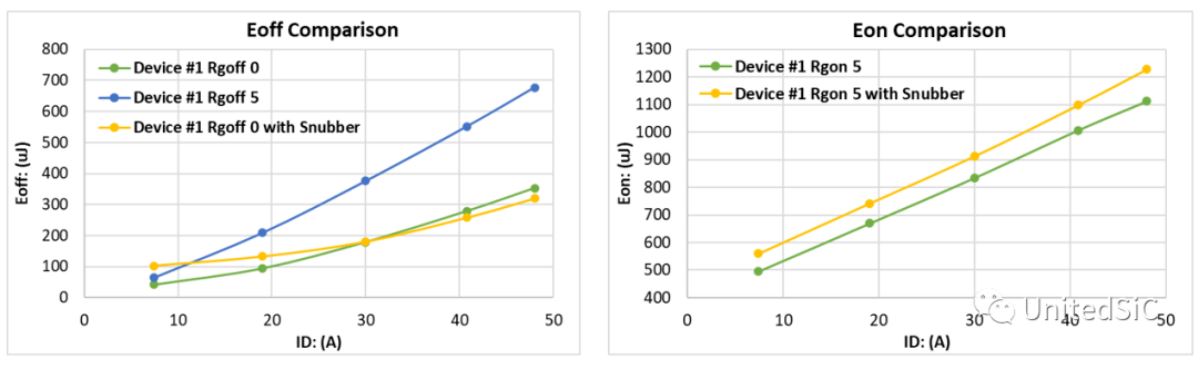

图5.缓冲电路和大RG(off)的开关损耗(Eoff、Eon)的比较

在48A电流下,大RG(off)的关闭损耗是含小RG(off)的缓冲电路的两倍以上,几乎与不采用缓冲电路时相当。因此,可以得出结论,缓冲电路更加高效,它允许更快地开关,并能更有效地控制VDS峰值和振铃。从打开损耗中可以看出,缓冲电路的Eon仅有微小的提高。

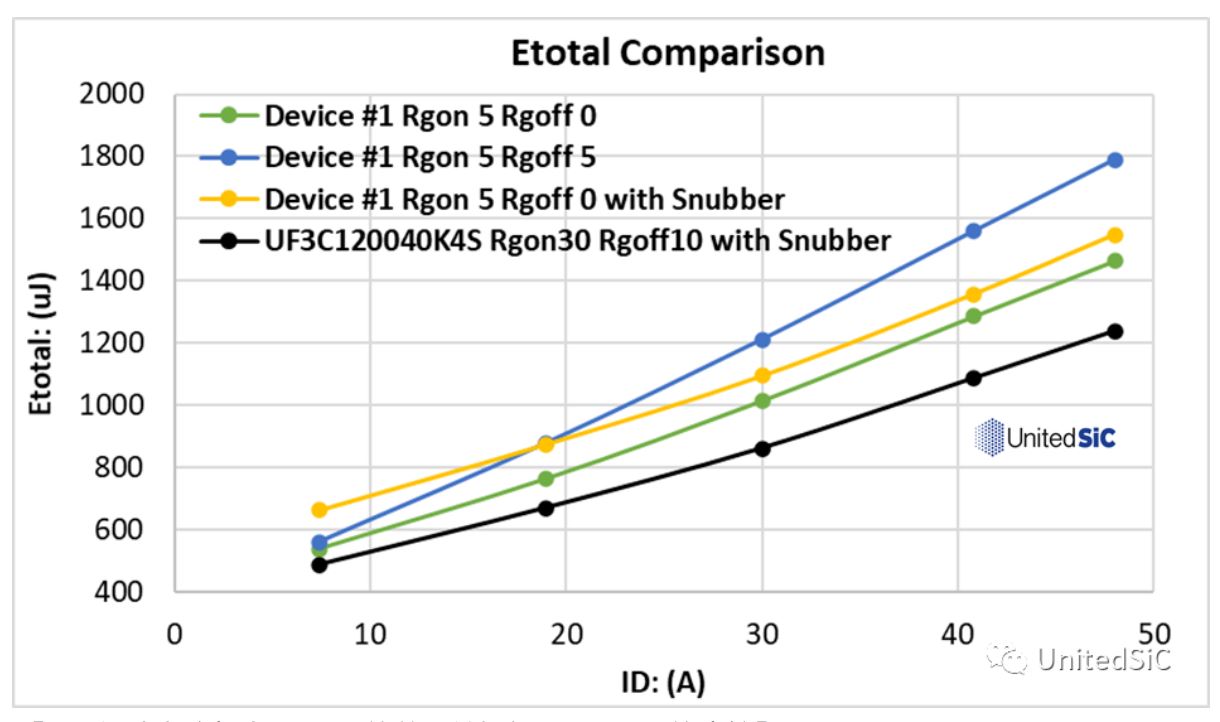

图6.缓冲电路与大RG(off)的总开关损耗(Etotal)的比较

为了更好地了解整体效率,我们将Eoff与Eon加在一起得到Etotal(图6)。在全速开关的情况下,电流超过18A时,缓冲电路更高效。对于在40A/40kHz下开关的40mΩ器件而言,采用大RG(off)与采用含小RG(off)的缓冲电路时的损耗之差为11W。总之,与使用大RG(off)相比,缓冲电路能更为简单、有效和高效地尽量降低电磁干扰和开关损耗。

文章来源: UnitedSiC

-

影响MOSFET开关损耗的因素2024-09-14 2783

-

PFC MOSFET的开关损耗测试方案2022-10-19 2939

-

内置SiC SBD的Hybrid IGBT 在FRD+IGBT的车载充电器案例中 开关损耗降低67%2022-07-27 4807

-

功率MOSFET的开关损耗分析2021-04-16 1588

-

尽量降低无线系统供电时的电磁干扰2021-03-20 677

-

【干货】MOSFET开关损耗分析与计算2021-01-30 5494

-

SiC-SBD大幅降低开关损耗2019-03-27 3384

-

开关损耗更低,频率更高,应用设备体积更小的全SiC功率模块2018-12-04 2967

-

全SiC功率模块的开关损耗2018-11-27 4783

-

为何使用 SiC MOSFET2017-12-18 6042

-

功率MOSFET的开关损耗:关断损耗2017-03-06 7346

-

功率MOSFET的开关损耗:开通损耗2017-02-24 6963

-

MOSFET开关损耗分析2016-01-04 996

全部0条评论

快来发表一下你的评论吧 !