【科普小贴士】MOSFET性能改进:超级结MOSFET(SJ-MOS)

电子说

1.4w人已加入

描述

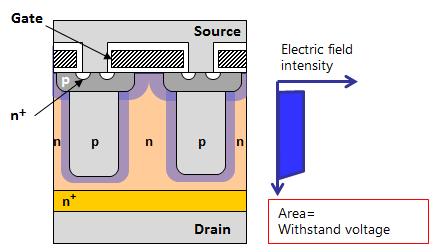

(1)SJ-MOS在N层具有柱状P层(P柱层)。P层和N层交替排列。(参见图3-9(b))

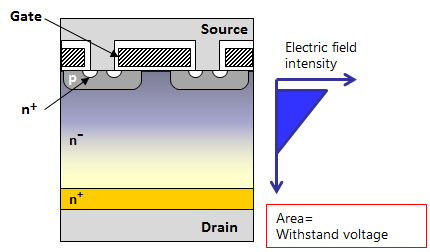

(2)通过施加VDS,耗尽层在N层中扩展,但其在SJ-MOS中的扩展方式与在一般D-MOS中不同。(关于电场强度,参见图3-9(a)/(b)。电场强度将表示耗尽层的状态。

(3)如果是D-MOS的情况,电场强度在P/N层接口处最强。当电场强度超过硅的极限时,会发生击穿现象,这就是电压极限。另一方面,如果是SJ-MOS的情况,电场强度在N层中是均匀的。

(4)所以,SJ-MOS可采用具有较低电阻的N层设计,以实现低导通电阻产品。

采用与DMOS相同尺寸的芯片,SJ-MOS可以实现更低的导通电阻。

图3-9(a)D-MOS(π-MOS)的结构和电场

图3-9(b)SJ-MOS(DTMOS)的结构和电场

文章来源:东芝半导体

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

超结MOSFET的基本结构与工作原理2026-01-04 2853

-

【科普小贴士】按结构分类的MOSFET特性摘要2023-12-13 970

-

【科普小贴士】MOSFET的性能:雪崩能力2023-12-07 1862

-

【科普小贴士】MOSFET的性能:电容的特性2023-11-23 2945

-

浅谈超级结MOSFET的效率改善和小型化2023-02-17 2392

-

高耐压超级结MOSFET的种类与特征2018-12-03 2897

-

超级结MOSFET2018-11-28 4148

-

超级结MOSFET的优势2018-10-17 3276

全部0条评论

快来发表一下你的评论吧 !