TC3xx芯片时钟系统的锁相环PLL详解

电子说

描述

前言

时钟好比MCU的心跳,只有时钟正常了,MCU的核及外设才能正常工作。从源头到系统到外设理解每一个时钟的来源及其具体值才能方便后面理解MCAL的GPT,PWM,ICU等模块的配置(MCAL模块中的Tick数就是基于模块时钟的)。本系列文章就来详细介绍TC3xx芯片的时钟系统及其具体配置。本文为TC3xx芯片时钟系统的锁相环PLL详解。

缩略词

| 简写 | 全称 |

| OSC | Oscillator Circuit |

| PLL | Phase-Locked Loop |

| DCO | Digitally Controlled Oscillator |

注:本文章引用了一些第三方工具和文档,若有侵权,请联系作者删除!

正文

2. 时钟倍频PLL

系统 PLL 可以将低频外部时钟信号转换为高速内部时钟,以获得最佳性能。它允许通过改变不同的分频器因子来使用多种输入和输出频率。

系统 PLL 还具有故障安全逻辑,可检测到非生成外部时钟行为,如异常频率偏差或外部时钟完全丢失。如果它在外部时钟上失去锁定,它可以执行紧急操作。

2.1 特点

DCO锁检测

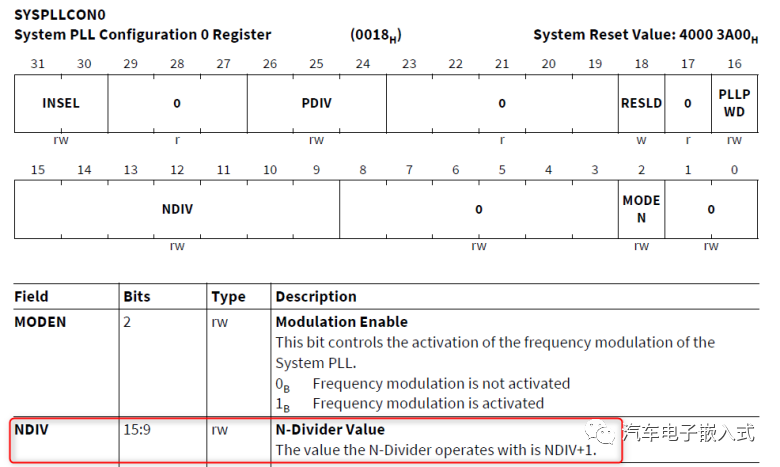

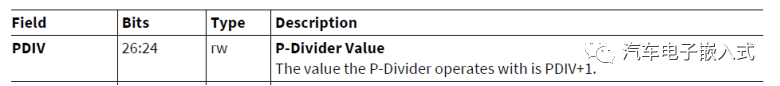

3 位输入分隔器 P (除以 PDIV+1)

7 位反馈分隔器 N (乘以 NDIV+1)

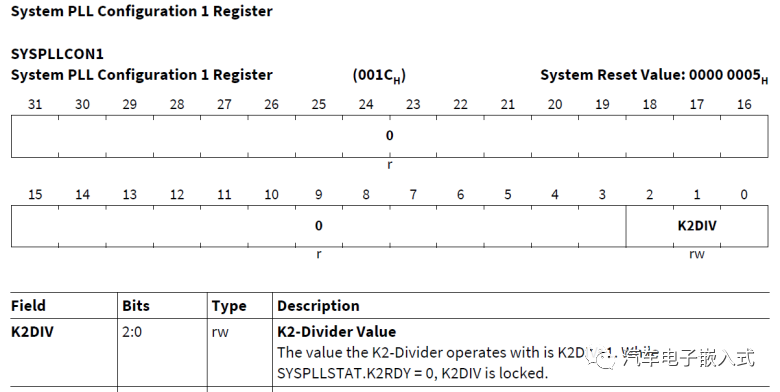

3 位输出分隔器 K2 (除以 K2DIV+1)

振荡器监视(Oscillator Watchdog)

-检测输入频率是否太低

-检测输入频率是否太高

低频率抖动调制

2.2 系统时钟锁相环PLL

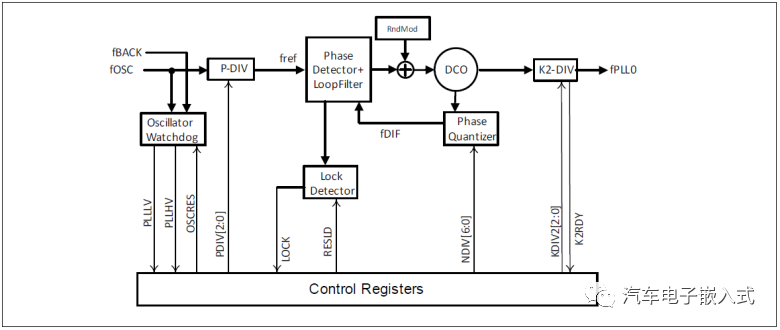

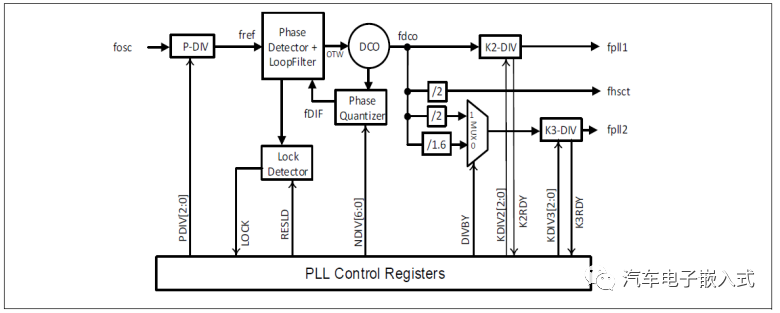

Figure 3 System PLL Block Diagram

输入频率 fOSC 除以因子 P ,乘以因子 N ,然后再除以因子 K2。

输出频率计算公式如下:

fPLL0 = (N* fOSC) / (P * K2)

fPLL0需要 fOSC 的输入时钟频率。 因此,建议通过检查 OSCCON.PLLV 来检查和监控输入频率 fOSC 是否可用。 为了更好地监控,还可以通过 OSCCON.PLLHV 监控上频。

系统操作频率由三个分频器(divider)的值控制: P , N 和 K2。修改两个分频器 P 和 N 对 DCO 频率有直接影响,可能导致锁定状态丢失。修改 K2 分频器对锁定状态没有影响,但仍会更改系统 PLL 输出频率 fPLL0.

注意:通过更改 K2-Divider 的值来更改系统操作频率,可以直接连接到设备的功耗。因此,必须谨慎行事。

当必须修改系统 PLL 输出频率的频率时,应遵循以下顺序:

应禁用为失去锁定而生成的 SMU 警报。

CCU 使用不同的时钟源时,可以配置系统 PLL 并检查其位置 DCO 锁定状态。第一个目标频率的选择方式应与 CCU 当前使用的目标频率相匹配,或仅略高一些。这可以避免在以后切换至系统 PLL 时发生系统操作频率 (因此也避免功耗) 的大变化。应按以下方式选择 P 和 N 分频因子(divider):

选择 P 和 N 时, fDCO位于其允许值的下半部分。 这会导致功耗略有降低,但抖动略有增加。

选择 P 和 N 时, fDCO位于其允许值的上部区域。 这会导致功耗略有增加,但抖动略有降低。

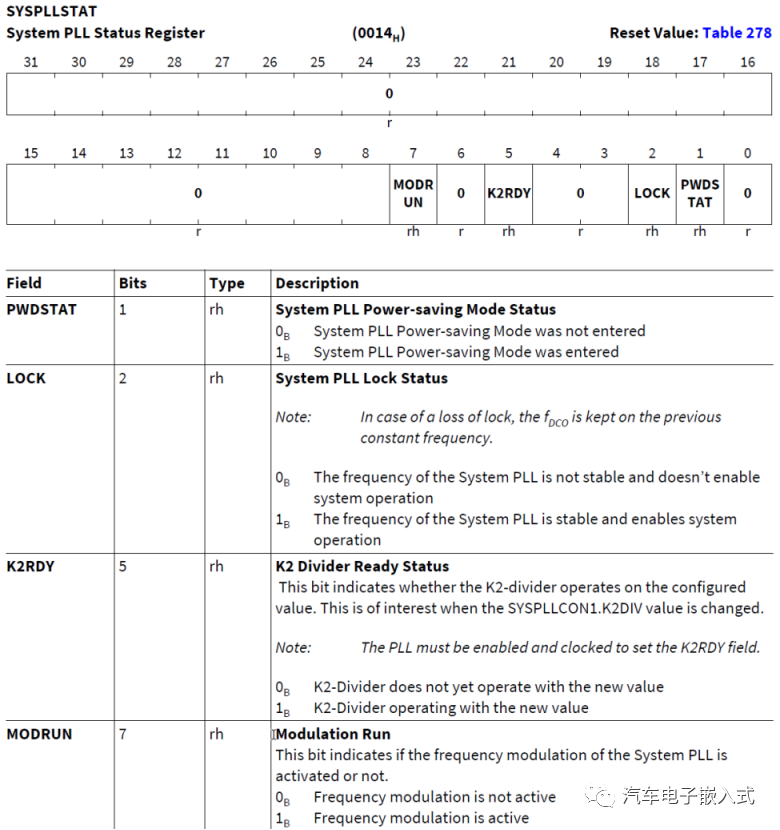

通过更新 P , N 和 K2 分频因子完成第一次PLL时钟配置后,应检查 DCO 锁定状态指示 (SYSPLLSTAT.LOCK = 1)。

系统 PLL 锁定后,可以切换至系统 PLL。系统 PLL 丢失锁定事件的 SMU 状态标志应被清除,然后再次启用SMU监控。

现在只能通过更改 K2-Divider 来配置目标系统 PLL 输出目标频率。根据 K2-Divider 的值,选择输出时钟的周期时间。这可能会对使用外部通信接口的操作产生影响。多步更改 k2-Divider ,以避免输出频率发生大变化,从而避免功耗发生大变化。

注意:

建议配置完P 和 N 分频器(divider)的新值后重置 DCO 锁定检测 (SYSPLLCON0.RESLD = 1) ,这样就能得到一个芯片预定义好的DCO锁的检测时间(让DCO锁有充足时间检测并锁定) 。

由于两个 PLL (System PLL and Peripheral PLL)的紧急从 PLL 切换至备用时钟同时激活,强烈建议仅在设置了外围 PLL 并将其锁定到目标频率时,才将系统时钟切换至系统 PLL。如果执行了顺序设置,则可能会发生外设 PLL 在设置过程中丢失锁定事件,这也会导致系统时钟切换至备用时钟。

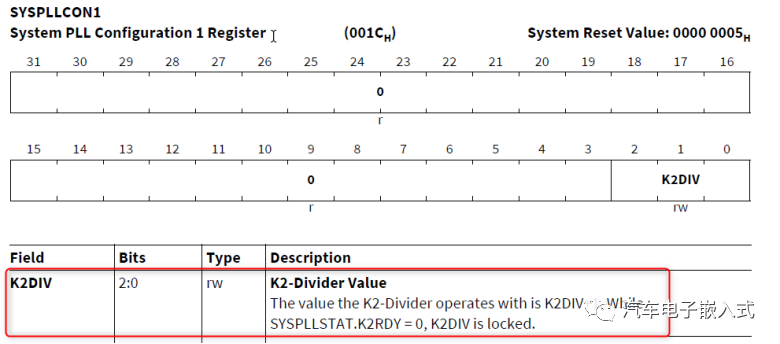

建议在设置 DCO 频率并锁定系统 PLL 后步进的设置系统 PLL K2-Divider (降低功率突变冲击)。此外,用户必须在再次更改 SYSPLLCON1.K2DIV 值之前检查 SYSPLLSTAT.K2RDY =1。SYSPLLCON1.K2DIV 寄存器在上一次写入仍在进行时被锁定,如 SYSPLLSTAT.K2RDY =0 所示。

System PLL Lock Detection

系统 PLL 具有锁定检测(lock detection)功能,用于监控系统 PLL 的 DCO 部分,以区分稳定和不稳定的 DCO 电路行为。如果两个输入fREF 和 fDIV 的差异太大,锁定探测器(lock detector)会将 DCO 电路标记为不稳定,因此 DCO 的输出fDCO. 低于某一级别的一个或两个输入频率的变化不会被锁定标记,因为 DCO 可以处理小的变化且保证系统没有任何问题。

System PLL Loss-of-Lock Event

由于晶体 / 陶瓷谐振器或外部时钟线断裂,系统PLL 可能会解锁。在这种情况下,会生成 SMU 警报事件。

System PLL Power Down Mode

系统 PLL 提供断电模式。如果根本不需要外围 PLL ,则可以进入此模式以节省电源。通过设置位 SYSPLLCON0.PLLPWD 进入断电模式。当系统 PLL 处于断电模式时,不会生成系统PLL 输出频率。

Frequency Modulation

系统 PLL 输出频率 fPLL0还可以通过低频调制进行修改,以减少 EMI。随机序列被添加到 DCO ,从而形成随机调制的 fDCO。 调制频率由 fREF定义。

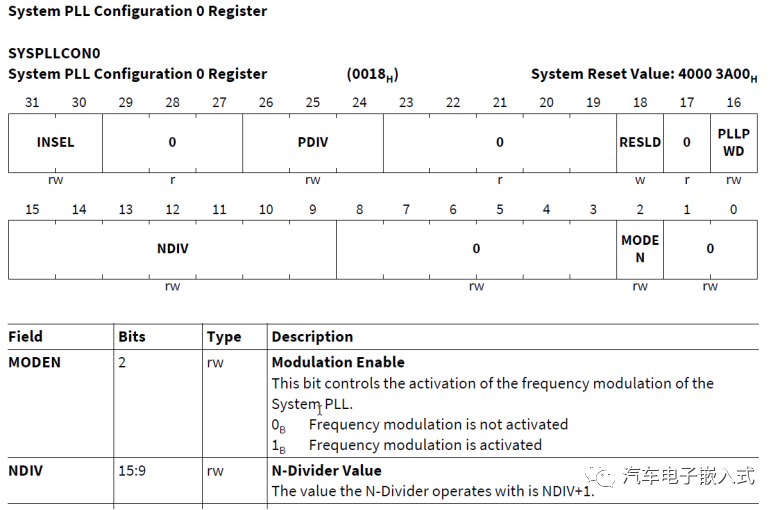

调制通过位 SYSPLLCON0.MODEN 启用。 调制本身会在配置的调制幅度 (MA) 范围内随机改变 DCO 频率。调制振幅通过 SYSPLLCON2.MODCFG[9:0] 选择。

SYSPLLCON2.MODCFG[9:0] = HEX[(64 * (MA / 100)) * (fOSC / P) *(N/ fMV)]

Example: for MA = 1.25%; fOSC = 20 MHz; P = 2; N = 60; fMV = 3.6 MHz the resulting bit field setting is 0x85.

调制的执行方式是,调制所增加的累积抖动保持在JMOD以下 (有关定义的值,请参阅数据表)。调制本身通过 fREF进行监控,因此应使用尽可能最小的值配置分压器。

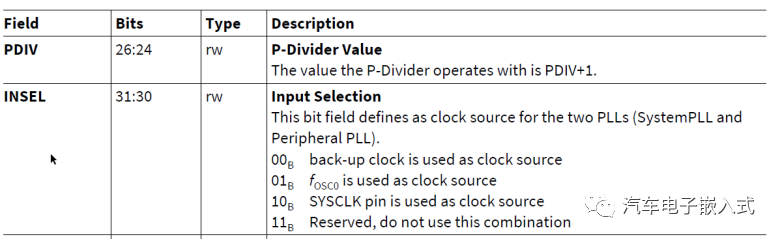

2.3 系统PLL寄存器

系统PLL状态寄存器

系统控制寄存器0

系统PLL配置寄存器1

2.4 外设时钟锁相环PLL

外设PLL配置基本和系统PLL类似,这里只给出时钟倍频图及其计算公式。

Figure 4 Peripheral PLL Block Diagram

fPLL1 = (N* fOSC) / (P * K2)

fPLL2 = (N* fOSC) / (P * K3 * 1.6) if DIVBY = 0 or fPLL2 = (N* fOSC) / (P * K3 * 2) if DIVBY = 1

fHSCT = fDCO / 2

通过配置外设PLL的配置寄存器就能配置P, K2, K3参数的具体值。

2.5 PLL实际应用配置

需求1:配置fOSC到100MHz.

公式:fPLL0 = (N* fOSC) / (P * K2)

fOSC == 20MHz

N = SYSPLLCON0.NDIV + 1 = 29(0x1D, 配置SYSPLLCON0.NDIV为29) + 1 = 30

P = SYSPLLCON0.PDIV + 1 = 0(配置SYSPLLCON0.PDIV为0) + 1 = 1

K2 = SYSPLLCON1.K2DIV + 1 = 5(配置SYSPLLCON1.K2DIV为5) +1 = 6

fPLL0 = (N* fOSC) / (P * K2) = (30 * 20)/(1 * 6) = 100MHz

查看SYSPLLSTAT寄存器的PWDSTAT和K2RD位域来判断时钟配置结果。

需求2:配置fPLL1到320MHz.

需求3:配置fPLL2到200MHz.

需求4:配置fHSCT到640MHz.

计算公式:

fPLL1 = (N* fOSC) / (P * K2)

fPLL2 = (N* fOSC) / (P * K3 * 1.6) if DIVBY = 0 or fPLL2 = (N* fOSC) / (P * K3 * 2) if DIVBY = 1

fHSCT = fDCO / 2

同样,我们配置:

N = 32

P = 1

K2 = 2

K3 = 2

fPLL1 = (N* fOSC) / (P * K2) = (32 * 20) / (1 * 2) = 320 MHz.

fPLL2 = (N* fOSC) / (P * K3 * 1.6) if DIVBY = 0 or fPLL2 = (N* fOSC) / (P * K3 * 2) if DIVBY = 1

= (32 * 20) / (1 * 2 * 1.6) = 200 MHz.

fHSCT = fDCO / 2 = = (N* fOSC) / (P) = 640 MHz.

示例代码:

#include "IfxScu_reg.h"

#include "IfxSmu_reg.h"

static uint8 Startup_ClockInit_ConfigPLL(void)

{

Ifx_SCU_SYSPLLCON0 SysPLLCon0;

Ifx_SCU_PERPLLCON0 ScuPerPllCon0;

Ifx_SCU_PERPLLCON1 ScuPerPllCon1;

uint32 TimeoutCount;

uint8 Error = 0;

LockEndinit_Core0();

/* Configure the system PLL */

SysPLLCon0.U = MODULE_SCU.SYSPLLCON0.U;

SysPLLCon0.B.PDIV = 0x00;

SysPLLCon0.B.NDIV = 0x1D;

SysPLLCon0.B.INSEL = 1; // fOSC is used as clock source

MODULE_SCU.SYSPLLCON0.U = SysPLLCon0.U;

/* Configure the peripheral PLL */

ScuPerPllCon0.U = MODULE_SCU.PERPLLCON0.U;

ScuPerPllCon0.B.DIVBY = 0x00;

ScuPerPllCon0.B.PDIV = 0x00;

ScuPerPllCon0.B.NDIV = 0x1F;

MODULE_SCU.PERPLLCON0.U = ScuPerPllCon0.U;

/* Power up the system PLL and peripheral PLL */

MODULE_SCU.SYSPLLCON0.B.PLLPWD = 1;

MODULE_SCU.PERPLLCON0.B.PLLPWD = 1;

/* Check if the configuration is valid */

TimeoutCount = 0x3000;

while((MODULE_SCU.SYSPLLSTAT.B.PWDSTAT == 1U) || (MODULE_SCU.PERPLLSTAT.B.PWDSTAT == 1U))

{

if (((--(TimeoutCount)) <= 0)

{

(Error ) = 1;

break;

}

}

/* Check if the configuration is valid */

TimeoutCount = 0x5000;

while((MODULE_SCU.SYSPLLSTAT.B.K2RDY == 0U) ||

(MODULE_SCU.PERPLLSTAT.B.K2RDY == 0U) ||

(MODULE_SCU.PERPLLSTAT.B.K3RDY == 0U))

{

if (((--TimeoutCount)) <= 0)

{

(Error ) = 1;

break;

}

}

MODULE_SCU.SYSPLLCON1.B.K2DIV = 5;

ScuPerPllCon1.U = MODULE_SCU.PERPLLCON1.U;

ScuPerPllCon1.B.K2DIV = 1;

ScuPerPllCon1.B.K3DIV = 1;

MODULE_SCU.PERPLLCON1.U = ScuPerPllCon1.U;

TimeoutCount = 0x5000;

while((MODULE_SCU.SYSPLLSTAT.B.K2RDY == 0U) ||

(MODULE_SCU.PERPLLSTAT.B.K2RDY == 0U) ||

(MODULE_SCU.PERPLLSTAT.B.K3RDY == 0U))

{

if (((--(TimeoutCount)) <= 0)

{

(Error ) = 1;

break;

}

}

/* Start PLL locking for latest set values*/

MODULE_SCU.SYSPLLCON0.B.RESLD = 1;

MODULE_SCU.PERPLLCON0.B.RESLD = 1;

/*Wait for PLL lock to be set*/

TimeoutCount = 0x3000;

while((MODULE_SCU.SYSPLLSTAT.B.LOCK == 0U) || (MODULE_SCU.PERPLLSTAT.B.LOCK == 0U))

{

if (((--(TimeoutCount)) <= 0)

{

(Error ) = 1;

break;

}

}

UnlockEndinit_Core0();

}

Note:下一篇文章介绍TC3xx芯片时钟系统的时钟分配CCU.

审核编辑:汤梓红

-

锁相环PLL的工作原理 锁相环PLL应用领域2024-11-06 4458

-

TC3xx芯片的Endinit功能详解2023-11-27 4559

-

频繁地开关锁相环芯片的电源会对锁相环有何影响?2023-10-30 1500

-

了解锁相环(PLL)瞬态响应 如何优化锁相环(PLL)的瞬态响应?2023-10-23 3376

-

pll锁相环的作用 pll锁相环的三种配置模式2023-10-13 5671

-

TC3xx芯片的MPU功能详解2023-09-19 5531

-

pll锁相环倍频的原理2023-09-02 5262

-

TC3xx芯片DMU介绍2023-08-31 4015

-

LabVIEW锁相环(PLL)2022-05-31 8100

-

锁相环(PLL)的工作原理及应用2022-03-29 16301

-

锁相环2011-10-26 17708

-

锁相环(PLL),锁相环(PLL)是什么意思2010-03-23 6461

-

锁相环原理2007-08-21 5597

全部0条评论

快来发表一下你的评论吧 !