使用SystemVerilog调试布局方法

电子说

描述

Xcelium工具中的SimVision是一个图形化的工具,支持对SystemVerilog代码的调试,同时内置svdebug布局帮助用户来调试基于System Verilog的验证环境。

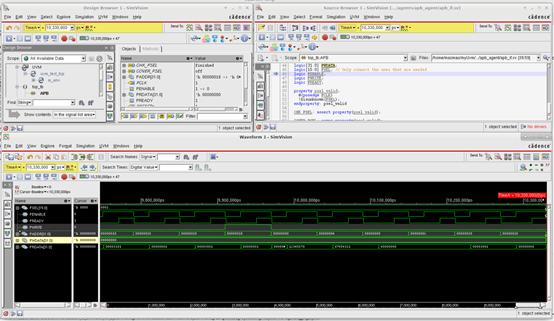

使用SystemVerilog调试布局

System Verilog调试布局由三部分组成。左上角Design Browser,可以访问仿真对象,右上角为Source Browser,用来展示源码,下侧窗口为Waveform window,用来显示波形。

启动SystemVerilog调试布局的方式

命令行使用 –layout svdebug 来指定,如:

xrun –s –gui –layout svdebug –linedebug top_tb.sv

使用菜单栏切换布局

Window – Layout – SystemVerilog Debugging

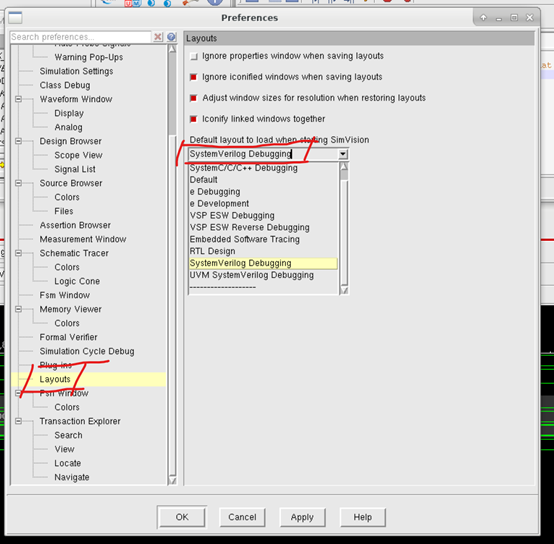

设置SystemVerilog为默认窗口布局的方式

启动SimVison图形界面

选择Edit – Preferences

打开Layouts 标签

选择System Verilog Debugging为默认窗口布局

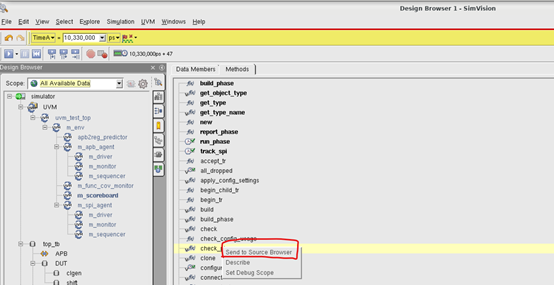

通过Design Browser查看SystemVerilog对象

这里可以看到对象的实例,包括它们之间的层级关系以及各个对象的数据成员和包含的task和function。还可以看到module实例及其层级关系。需要查看源码,可以右击目标选择Send to Source Browser。

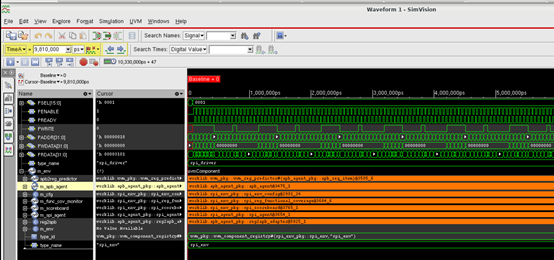

使用Waveform Window查看SystemVerilog对象

该窗口支持对 Static variables / Class variables /Queues / Packed structures / Packed arrays / Associative arrays / Dynamicarrays对象的查看

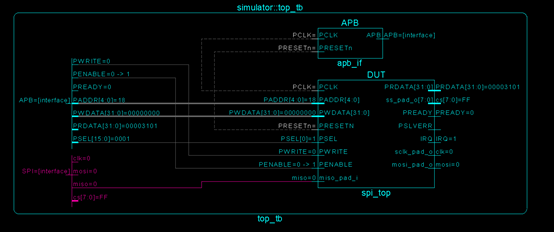

使用Schematic Tracer查看SystemVerilog对象

Schematic Tracer用来显示interface、modports与rtl之间的连接关系。

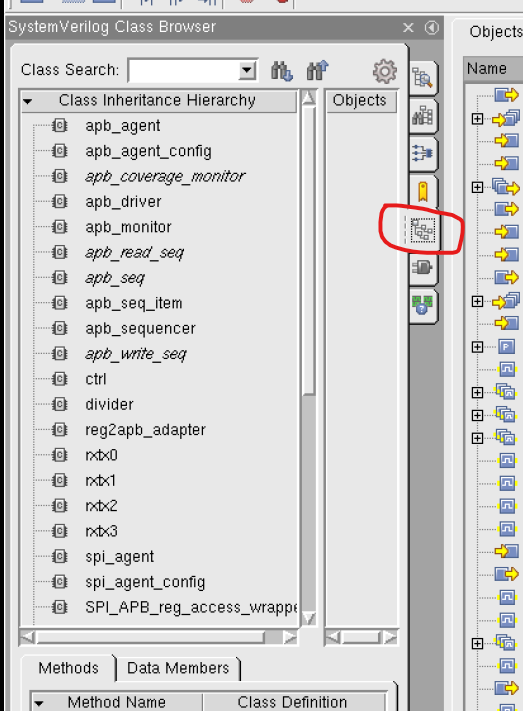

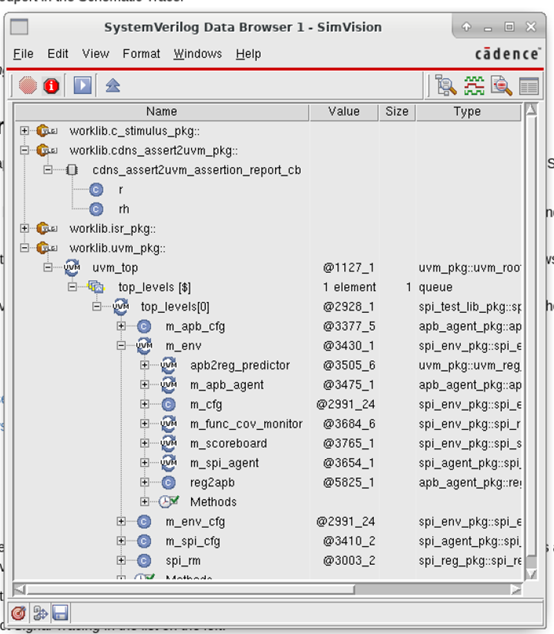

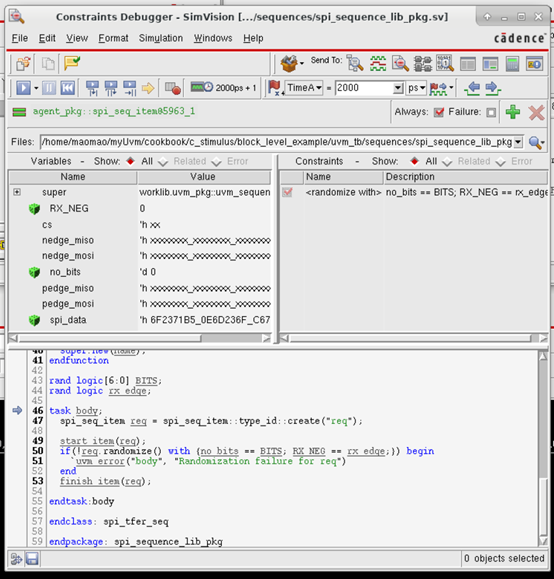

其他SystemVerilog调试窗口

SystemVerilog Class Browser

Data Browser

Constraints Debugger

审核编辑:黄飞

-

SystemVerilog的随机约束方法2023-09-24 3922

-

简述SystemVerilog的随机约束方法2023-01-21 3526

-

SystemVerilog中的Virtual Methods2022-11-28 1187

-

怎样去使用SystemVerilog中的Static方法呢2022-11-18 1904

-

SystemVerilog中的操作方法2022-10-31 4499

-

SystemVerilog有哪些标准?2021-06-21 1962

-

SystemVerilog的正式验证和混合验证2021-03-29 929

-

做FPGA工程师需要掌握SystemVerilog吗?2017-08-02 7097

-

systemverilog学习教程2015-04-01 8655

-

[启芯公开课] SystemVerilog for Verification2013-06-10 8956

-

SystemVerilog 的VMM验证方法学教程教材2012-01-11 59465

-

基于SystemVerilog语言的验证方法学介绍2011-05-09 1096

-

基于事件结构的SystemVerilog指称语义2009-12-22 595

-

SystemVerilog Assertion Handbo2009-07-22 1064

全部0条评论

快来发表一下你的评论吧 !