verilog中有符号数和无符号数的本质探究

电子说

描述

不知道有没有人像我一样,长久以来将verilog中的有符号数视为不敢触碰的禁区。不过俗话说啊解决恐惧的最好办法就是直面恐惧,又有俗话说要想工其事必先利其器,还有俗话说磨刀不误砍柴工,也有俗话说The only thing we have to fear is fear itself,所以今天咱们就尝试对verilog中数据的符号属性(有符号数和无符号数)探究根源。

本文的验证环境基于VCS通过auto_testbench生成,相关的vcs命令行细节请在auto_testbench工程目录下查询。

先说明一个大前提,有符号数即补码表示,无符号数即原码表示或者说必然是整数的补码表示,因此有符号数和无符号数均可以认为是数值的补码。

为了省流,还是先甩结论。有符号数和无符号数的最本质区别就是:符号位的识别和高位拓展。除此之外,另一个区别就是从人的角度如何如何读这个数,或者说$display(%d)打印时打印的值是什么(而从机器的角度它压根就不区分signed和unsigned)。也就是说,如果不涉及到位宽拓展的事,有符号数和无符号数在verilog运算中可以说毫无差别。

所以先给出两个结论,verilog中数据的符号属性会影响两件事:

1.符号位的识别和位宽拓展,有符号数最高位被识别为符号位,高位拓展时拓展符号位,无符号数高位拓展0;

2.数据的实际值(人的角度如何如何读这个数);

显然,这个这个结论和固有的认知出入有点大,不急咱们先看一个实验。下面的代码是一段不涉及到位宽拓展的运算,t0_va0为有符号数-1,也就是16'hffff:

wire signed[15:0]t0_en0 = t0_va0 + 16'hffff;

wire [15:0]t0_en1 = t0_va0 + 16'hffff;

wire signed[15:0]t0_en2 = t0_va0 + $signed(16'hffff);

wire [15:0]t0_en3 = t0_va0 + $signed(16'hffff);

wire signed[15:0]t0_en4 = t0_va0 - 16'h1;

wire signed[15:0]t0_en5 = t0_va0 - $unsigned(16'h1);

wire [15:0]t0_en6 = t0_va0 - 16'h1;

wire [15:0]t0_en7 = t0_va0 - $unsigned(16'h1);

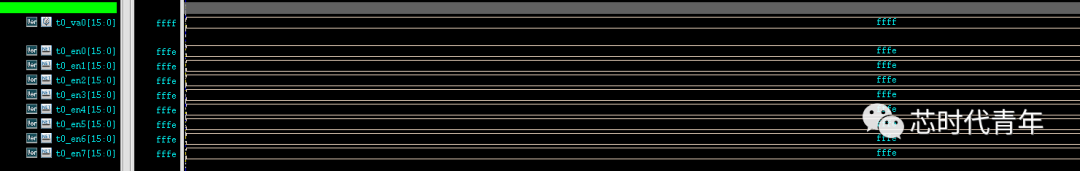

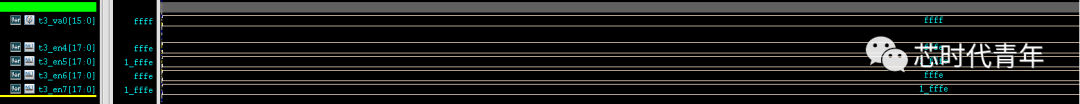

仿真的结果如下:

可以看到所有的结果都是一致的。而如果将va0信号改成无符号数:

wire signed[15:0]t1_en0 = t1_va0 + 16'hffff;

wire [15:0]t1_en1 = t1_va0 + 16'hffff;

wire signed[15:0]t1_en2 = t1_va0 + $signed(16'hffff);

wire [15:0]t1_en3 = t1_va0 + $signed(16'hffff);

wire signed[15:0]t1_en4 = t1_va0 - 16'h1;

wire signed[15:0]t1_en5 = t1_va0 - $unsigned(16'h1);

wire [15:0]t1_en6 = t1_va0 - 16'h1;

wire [15:0]t1_en7 = t1_va0 - $unsigned(16'h1);

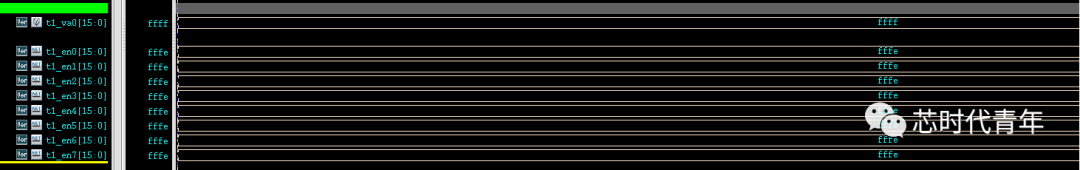

其仿真结果也是一致的:

而一旦涉及到运算结果位宽拓展结果就有所差别了,比如将结果的位宽都改成18bit:

wire signed[17:0]t2_en0 = t2_va0 + 16'hffff;

wire [17:0]t2_en1 = t2_va0 + 16'hffff;

wire signed[17:0]t2_en2 = t2_va0 + $signed(16'hffff);

wire [17:0]t2_en3 = t2_va0 + $signed(16'hffff);

wire signed[17:0]t2_en4 = t2_va0 - 16'h1;

wire signed[17:0]t2_en5 = t2_va0 - $unsigned(16'h1);

wire [17:0]t2_en6 = t2_va0 - 16'h1;

wire [17:0]t2_en7 = t2_va0 - $unsigned(16'h1);

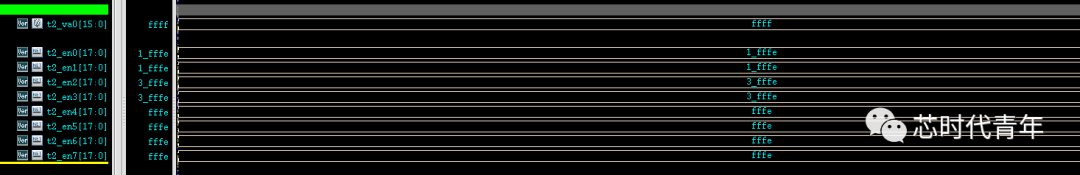

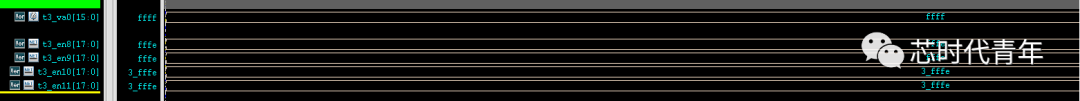

看到的波形就是这样:

这个事就有些神奇了,所以后面就是说明下这里面的区别,或者说在完成运算后工具是如何识别这个数的符号性以决定位宽拓展的结果的。在开始之前必须明确下一个有符号数(补码),'h1fffe和'hfffe对于机器是没有区别的,都是-2。

仿真工具在对一个运算结果进行位宽拓展时,会先识别这个数的符号属性,那么具体是怎么识别的呢?

1.有符号数和有符号数运算,结果为有符号数;

2.有符号数和无符号数运算,结果为无符号数;

3.无符号数和无符号数运算,结果为无符号数;

4.运算结果外又通过signed和unsigned定向指定时,最终的符号属性遵照指定结果;

5.等号左侧信号声明中的signed/unsigned不影响右侧运算结果的符号数属性;

好,咱们一个一个看。

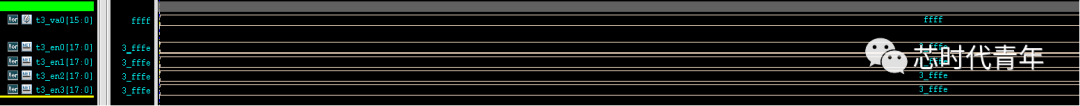

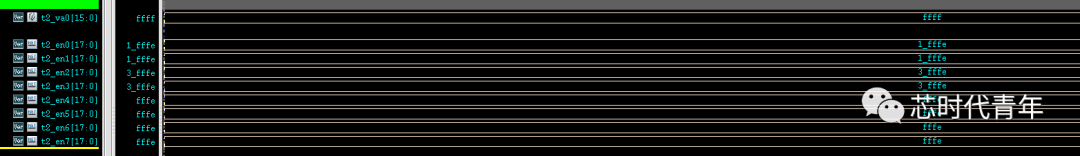

有符号数和有符号数运算,结果为有符号数。

wire signed[17:0]t3_en0 = t3_va0 - $signed(16'h1);

wire signed[17:0]t3_en1 = t3_va0 + $signed(16'hffff);

wire [17:0]t3_en2 = t3_va0 - $signed(16'h1);

wire [17:0]t3_en3 = t3_va0 + $signed(16'hffff);

很显然,两个有符号数进行操作结果是有符号数,位宽拓展时拓展符号位。同时这个波形还说明了等号左侧信号声明中的signed/unsigned不影响右侧运算结果的符号数属性。

有符号数和无符号数运算,结果为无符号数。

wire signed[17:0]t3_en5 = t3_va0 + 16'hffff;

wire [17:0]t3_en6 = t3_va0 - 16'h1;

wire [17:0]t3_en7 = t3_va0 + 16'hffff;

显然结果是无符号数,高位拓展时拓展的都是0。

显然结果是无符号数,高位拓展时拓展的都是0。

无符号数和无符号数运算,结果为无符号数。这个不说了,显而易见的事情。

运算结果外又通过signed和unsigned定向指定时,最终的符号属性遵照指定结果。

wire signed[17:0]t3_en9 = $unsigned(t3_va0 + $signed(16'hffff));

wire [17:0]t3_en10 = $signed(t3_va0 - 16'h1);

wire [17:0]t3_en11 = $signed(t3_va0 + 16'hffff);

因为在运算之后又通过signed和unsigned指定了符号属性,所以后面的位宽拓展就按照对应的属性来了。再次进一步的佐证,等号左侧信号声明中的signed/unsigned不影响右侧运算结果的符号数属性。

因为在运算之后又通过signed和unsigned指定了符号属性,所以后面的位宽拓展就按照对应的属性来了。再次进一步的佐证,等号左侧信号声明中的signed/unsigned不影响右侧运算结果的符号数属性。

好了现在我们再把前文的结论翻出来,verilog中的符号属性会影响两件事情:

1.符号位的识别和位宽拓展,有符号数最高位被识别为符号位,高位拓展时拓展符号位,无符号数高位拓展0;

2.数据的实际值(人的角度如何如何读这个数);

再看这个测试就很好解释了:

wire signed[17:0]t2_en0 = t2_va0 + 16'hffff;

//就是'hffff+'hffff = 'h1fffe

wire [17:0]t2_en1 = t2_va0 + 16'hffff;

//同上

wire signed[17:0]t2_en2 = t2_va0 + $signed(16'hffff);

//本质还是'hffff+'hffff = 'h1fffe,不过因为结果是有符号数,拓展位宽为18bit时拓展为18'h3fffe

wire [17:0]t2_en3 = t2_va0 + $signed(16'hffff);

//同上

wire signed[17:0]t2_en4 = t2_va0 - 16'h1;

//本质是'hffff-'h1,或者理解成'hffff+'hffff,加上一个负数位宽一定不需要高位拓展,所以结果是'hfffe

//再根据等号左侧的需求拓展为18bit,无符号数拓展0,结果为18'fffe

wire signed[17:0]t2_en5 = t2_va0 - $unsigned(16'h1);

//同上

wire [17:0]t2_en6 = t2_va0 - 16'h1;

//同上

wire [17:0]t2_en7 = t2_va0 - $unsigned(16'h1);

//同上

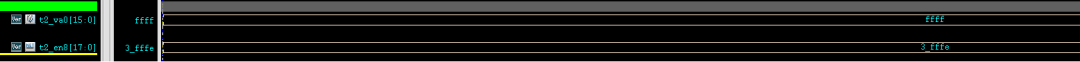

再来补充一个,大家看看结果应该是啥:

显然结果应该是18'h3fffe,因为左侧的运算结果是有符号数的16'hfffe,拓展成18bit时拓展符号位1:

最后呢再看一组额外的实验,感兴趣的可以分析一下结果:

logic [1:0]va_u;

logic signed[1:0]va_s;

logic [2:0]vb_u;

logic [2:0]vb_s;

logic [31:0]vc_u;

logic [31:0]vc_s;

initial begin

va_u = -1;

va_s = -1;//signed

$display("va_u='b%0b, va_s='b%0b", va_u, va_s);

$display("va_u=%0d, va_s=%0d", va_u, va_s);

vb_u = -va_u;

vb_s = -va_s;

$display("vb_u='b%0b, vb_s='b%0b", vb_u, vb_s);

$display("vb_u=%0d, vb_s=%0d", vb_u, vb_s);

vc_u = va_u;

vc_s = va_s;

$display("vc_u='b%0b, vc_s='b%0b", vc_u, vc_s);

end

仿真的结果为:

va_u=3, va_s=-1

vb_u='b101, vb_s='b1

vb_u=5, vb_s=1

vc_u='b11, vc_s='b11111111111111111111111111111111

-

请问AFE5801 AD转换后数字信号是用有符号数还是无符号数表示的?2025-02-11 422

-

verilog中数据的符号属性(有符号数和无符号数)探究根源2023-12-10 3273

-

C语言中无符号数和有符号数的左移和右移2022-01-13 1395

-

求无符号数的平均数2021-12-01 1099

-

详细分析Verilog编写程序测试无符号数和有符号数的乘法2021-05-02 8736

-

双状态无符号/有符号数据类型2021-01-18 2194

-

关于verilog中的无符号数和有符号数2020-11-18 18627

-

请问AFE5801 AD转换后数字信号是用有符号数还是无符号数表示?2019-05-24 3583

-

fpga 有符号数、无符号数2018-10-09 6915

-

有符号数,无符号数,浮点数探讨2015-04-29 6063

-

关于无符号数和有符号数的困惑2013-11-02 6699

-

原码、补码、反码、有符号数、无符号数概念.pdf2012-11-15 5439

-

采集的数据转换成有符号数的问题2012-05-02 6430

-

双字节二进制无符号数除法2009-01-19 2552

全部0条评论

快来发表一下你的评论吧 !