芯片后仿之SDF 3.0解析

描述

SDF文件是在VCS/NC-Verilog后仿真运行时将STD/IO/Macro门级verilog中specify的延迟信息替换为QRC/Star-RC抽取的实际物理延时信息,所以如果SDF文件的条件信息在verilog的specify中没有的话,就会报SDFCOM_INF的warning,意思是IOPATH not found。

本文解析SDF的Header Section信息、Cell Entries信息,尤其重点讲解Cell Entries的Delay Entries信息。

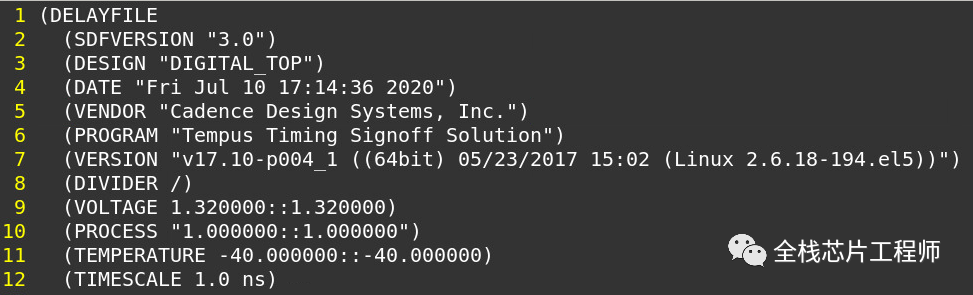

下文先讲SDF文件的第一部分Header Section

SDF Version Entry,包括1.0、2.1、3.0,SDF3.0是1995年release。

Design Name Entry,设计顶层名

Date Entry,SDF生成日期,PT或Tempus产生

Vendor Entry,Vendor信息,如下图

Program Version Entry

Hierarchy Divider Entry

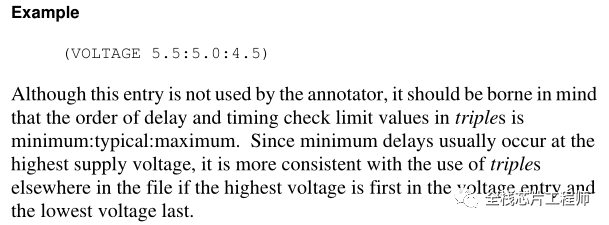

Voltage Entry,SDF3.0官方解释如下

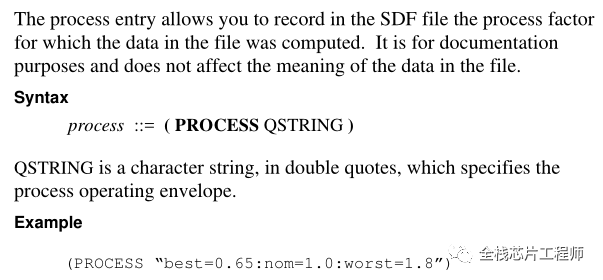

Process Entry,SDF3.0官方解释如下

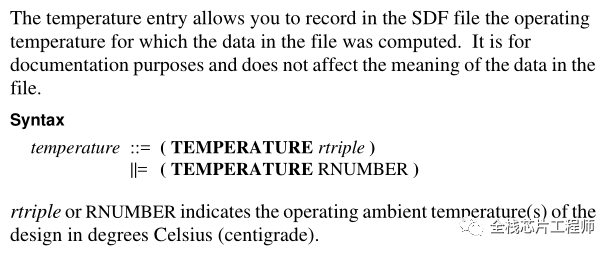

Temperature Entry,SDF3.0官方解释如下

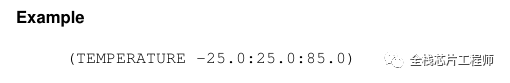

Timescale Entry,SDF3.0官方解释如下

下文继续讲解SDF文件的第二部分Cell Entries:

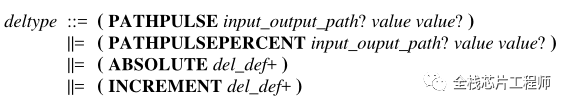

完整的Delay Entries信息格式如下:

完整的Delay Entries信息格式如下:

PATHPULSE

PATHPULSEPERCENT

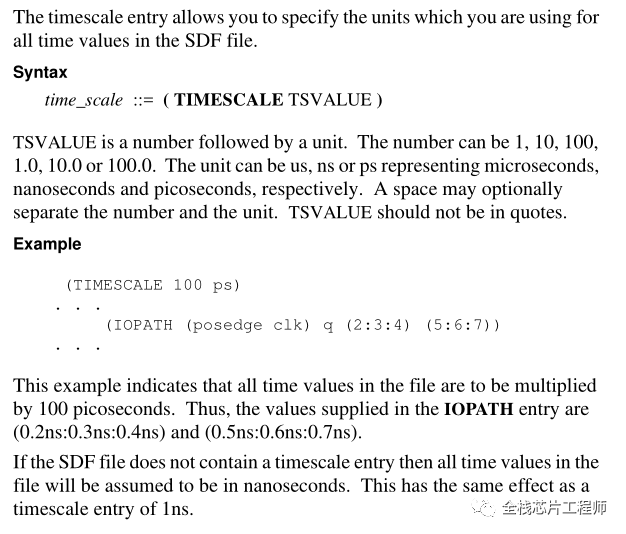

ABSOLUTE Delays

INCREMENT Delays

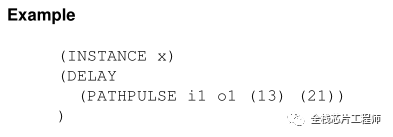

1. PATHPULSE 举例说明:

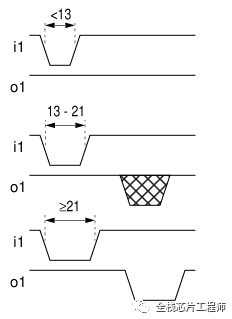

当从i1到o1输出的低电平脉冲小于13ns时,该低电平脉冲直接被忽略;

当从i1到o1输出的低电平脉冲介于13ns~21ns时,输出为X态;

当从i1到o1输出的低电平脉冲大于21ns时,正常输出低电平;

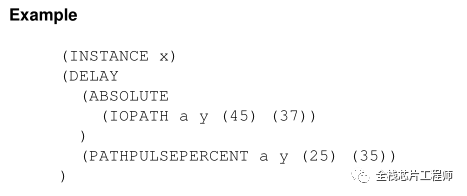

2. PATHPULSEPERCENT 本质上和PATHPULSE是一回事,只不过是按照path延时比例来计算什么时候丢弃输入脉冲宽度不足的信号(pulse rejection limit),什么时候将输入脉冲宽度不足的信号显示为X态(X limit)。比如:

2. PATHPULSEPERCENT 本质上和PATHPULSE是一回事,只不过是按照path延时比例来计算什么时候丢弃输入脉冲宽度不足的信号(pulse rejection limit),什么时候将输入脉冲宽度不足的信号显示为X态(X limit)。比如:

以上图为例,the high-to-low delay is 37, 因此,the pulse

rejection limit is 25% of 37 and the X limit is 35% of 37. 3. ABSOLUTE Delays ABSOLUTE Delays中的物理延时数据就是用来替换verilog specify中的延时数据的。

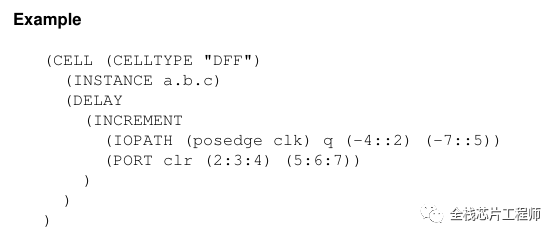

4. INCREMENT Delays

用来叠加在verilog specify中的延时数据上的,INCREMENT Delays是存在负数的情况的,叠加后的延时若是负数的话,某些EDA工具可能不支持或直接强制延时为0。

审核编辑:汤梓红

-

芯片后仿之SDF 3.0解析(三)2024-04-16 3952

-

运行后实现时序仿真后重新生成sdf文件2018-11-07 5882

-

如何将PT产生的SDF文件反标设计进行后仿真?2021-06-23 4083

-

SDF是什么?有何应用2021-09-02 1124

-

NodeMCU V3.0 Arduino开发之点灯测试程序2021-11-01 1483

-

NodeMCU V3.0 Arduino开发之点灯2021-10-25 856

-

STM8S全解析之系列文章3---STM8S芯片配置,软件框架搭建2021-12-03 810

-

ZigBee3.0数据包解析2022-02-28 3128

-

什么是数字后仿?浅谈芯片数字后仿的那些事2023-03-15 11968

-

解析SDF的Header Section信息与Cell Entries信息2023-05-06 3643

-

详解芯片SDF文件 MCU芯片全流程设计2023-05-08 13992

-

芯片后仿及SDF反标2023-06-08 5727

-

芯片后仿真要点2024-10-23 2842

全部0条评论

快来发表一下你的评论吧 !