什么是三端子电容?三端子电容好在哪?

描述

原文来自我的原创书籍《硬件设计指南 从器件认知到手机基带设计》:

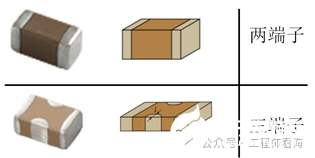

电容分为陶瓷电容、电解电容等种类,陶瓷电容在移动智能产品中使用广泛,又可分为两端子电容和三端子电容。人们常说三端子电容高频特性好,那么作为一名硬件工程师,你了解三端子电容吗?图1-9 是两端子电容和三端子电容的实物对比图,可以看到三端子电容多了几个引脚,正是由于这种设计差异,给三端子电容带来了巨大的性能优势,当然,也带来了昂贵的价格,鱼与熊掌难兼得。

图1-9 两端子电容与三端子电容

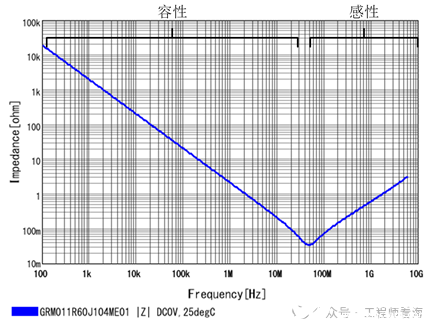

理想的电容,随着频率的增加,阻抗越来越低,也就是说频率越高,电容的“电阻”越小,越接近短路状态,信号也就越容易通过,见图1-6 的阻抗-频率曲线,这就是电容“隔直通交”的原因(后文介绍的低通滤波电路就是电容阻抗-频率的一个典型应用)。然而,实际电容是有寄生参数的,由于等效串联电阻ESR和等效串联电感ESL的存在,使得电容的阻抗频率特性产生了巨大变化。图1-10 是实际两端子电容的阻抗频率特性,我们可以看到在低频段,容性起主导作用,阻抗随着频率增加而降低,然而高频段是感性起主导作用,阻抗随着频率增加而增加,这部分正是我们不希望看到的。

图1-10 实际电容阻抗频率曲线

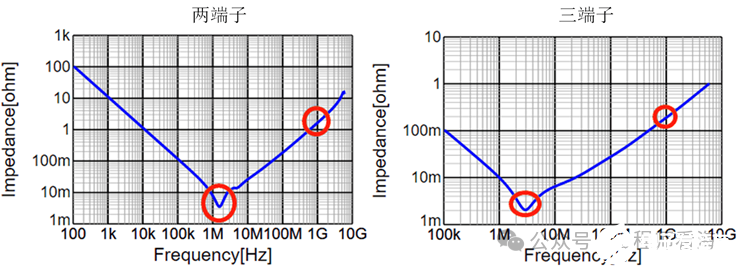

所谓三端子电容高频特性好,就是它的ESL低。我们在图1-11 对比22uf的两端子电容和三端子电容的阻抗差异,可以看到两端子电容在1MHz处阻抗大约3mΩ,三端子电容谐振频率高一些,在3MHz处阻抗只有大约2mΩ。我们再看高频部分,两端子电容在1GHz处甚至超过了1Ω,而三端子电容只有110mΩ。如果想降低两端子的高频阻抗就需要并联更多电容(电感越并越小,进而高频阻抗减小),换句话说就是两端子电容需要通过多个电容并联的方式才能达到1个三端子电容在高频处的阻抗特性,三端子电容高频特性是非常不错的!

图1-11 两端子电容对比三端子电容

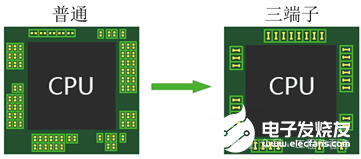

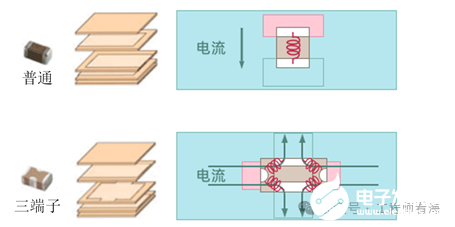

正是因为三端子电容高频特性好,因此在电源PDN优化时,有时会使用三端子电容来代替普通电容,既提高系统电源稳定性,又减小电容布局面积,如图1-12 所示。为什么三端子电容的高频特性好呢?(各位读者一定要养成自主提问的习惯)同样的问题:为什么三端子电容的ESL小?那是因为三端子电容结构特殊,缩短了电流路径,使得ESL具有并联的特性,进而减小了ESL,如图1-13 所示,普通电容沿着电流方向具有一个ESL,而三端子电容结构特殊使得这些ESL并联,导致了ESL的降低(电感越并越小),进而使得高频特性好。

图1-12 三端子电容减少布局面积

图1-13 三端子电容ESL低

虽然三端子电容的高频特性好,封装也小,但是它价格却很高,如果问怎么权衡价格,那么笔者的回答是:在忽略面积的设计中,一个字“拆”,就是使用多个、多种普通电容并联的方式优化电源,降低成本;如果空间实在有限,当布局放不下多个电容时再考虑在最紧凑的位置使用少量三端子电容优化电源。

如果看到这里,请点赞、收藏、分享三连!

限时免费扫码进群,交流更多行业技术

审核编辑 黄宇

- 相关推荐

- 热点推荐

- 电容

-

合粤牛角电容 VS 普通电解:PFC 电路中为何更认 “牛角端子”?2025-09-28 688

-

宇阳科技三端子MLCC产品介绍2025-06-03 1072

-

电流端子和电压端子的区别2023-12-09 6030

-

什么是三端子电容?为什么三端子电容的ESL小?2023-11-22 2476

-

馈通三端子电容器究竟好在哪里?2023-09-22 14737

-

什么是三端子电容?片状三端子电容器的安装方法2023-03-29 2220

-

作为一名硬件工程师你了解三端子电容吗?2022-11-03 2835

-

什么是片状三端子电容?怎样去安装它呢2022-08-17 7660

-

三端子电容器在高频电路中的应用2022-05-19 4049

-

三端子 #电容 究竟好在哪?半导体说 2021-07-15

-

三菱plc端子排列方法2020-03-08 10262

-

片状三端子电容器的注意事项及使用技巧2016-09-27 5636

-

噪声对策基础(五):片状三端子电容器2012-04-13 6217

-

三端子电容器的结构与等效电路图2009-07-17 6065

全部0条评论

快来发表一下你的评论吧 !