基于有限元模型的IC卡芯片受力分析研究

电子说

描述

摘要:

在智能卡三轮测试中,失效表现为芯片受损,本文基于有限元模型来研究智能 IC 卡(Integrated circuit card)芯片受力分析与强度提升方法,针对其结构尺寸参数变化时对芯片的机械强度影响做了相关有限元仿真,分析芯片的受力情况,从芯片大小、芯片厚度、芯片偏转角度、EMC 层厚度、PVC 厚度、Lead frame 厚度、芯片粘接胶厚七个因素,对比了 IC 卡单因素尺寸参数变化对芯片应力的影响,并依据正交设计表分析 IC 卡的七个因素的参数变化时芯片的受力情况,得到 EMC 层厚度、Lead frame 和PVC 卡片厚度的变化对芯片承受的最大应力影响显著,且随着这三个部件厚度的增加芯片所受最大应力减小的结论,为有效提升 IC 卡芯片的机械强度提供了方法。

0 引言

《GB/T 17554.3-2006 识别卡测试方法第三部分带触点的集成电路卡及其相关接口设备》标准规定需要对 IC 卡(Integrated Circuit Card,集成电路卡)的机械强度进行测试 [1] 。

该标准规定,芯片面积大于 4mm 2 时,机械强度测试方法为进行三轮测试,而小于 4mm 2 时的测试方法为点压力测试。IC 卡卡片的实际生产控制中,无论芯片面积是否小于 4mm 2 ,卡片生产使用相关环节均安排进行三轮测试。

三轮测试的严重失效一般是在压力作用下,IC卡中封装的芯片出现物理损伤。芯片承受的强度与IC 卡的各部件的物理规格有关,如芯片的大小、芯片厚度和封装时芯片的偏转角度等。在进行受力仿真过程中首先找到芯片在三轮测试过程中受力最大的危险位置,根据该位置分析 IC 卡各部件尺寸参数变化时芯片受力情况,并分析 IC 卡各部件的单因素尺寸参数变化对芯片应力的影响。本次仿真分析基于正交试验,共设计了 18 组试验。

本次 仿真 通过 ABAQUS 仿 真 软 件 完 成 ,ABAQUS 是一款有限元分析软件,具备强大的分析能力和模拟复杂系统的可靠性。软件包括丰富的、可模拟任意几何形状的单元库,并拥有各种类型的材料模型库。在复杂的固体力学结构力学系统中,能驾驭非常庞大复杂的问题和模拟高度非线性问题,本次仿真中涉及到了多部件的静态应力、位移分析和动态分析,涵盖了接触和几何两大非线性问题。ABAQUS 仿真软件可以实现多部件的快速建模并且求解的收敛性可以得到保障。

1 IC 卡有限元模型

1.1 IC 卡结构

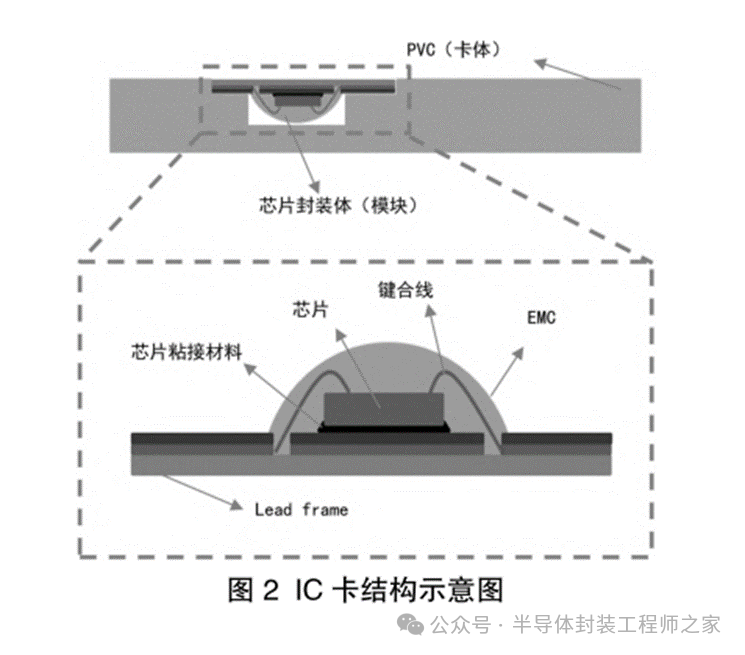

IC 卡由芯片封装体(行业中常称作“模块”)和PVC 卡片组成,芯片封装体包括芯片、Lead frame、键合线、芯片粘接层、EMC 层(注塑胶,多为环氧塑封料)等组成,芯片封装体和 PVC 卡片空腔部分进行装配组成 IC 卡[2] ,IC 卡实物图如图 1 所示、IC 卡结构示意图见图 2。

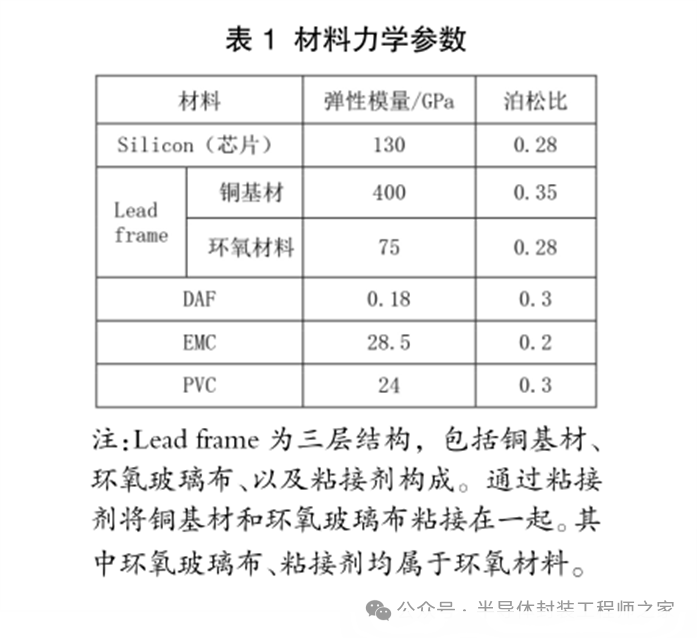

1.2 IC 卡的材料力学参数

表 1 为 IC 卡所用到的不同材料的力学参数。三轮测试用的轮子的弹性模量为 210 GPa,泊松比为 0.31。

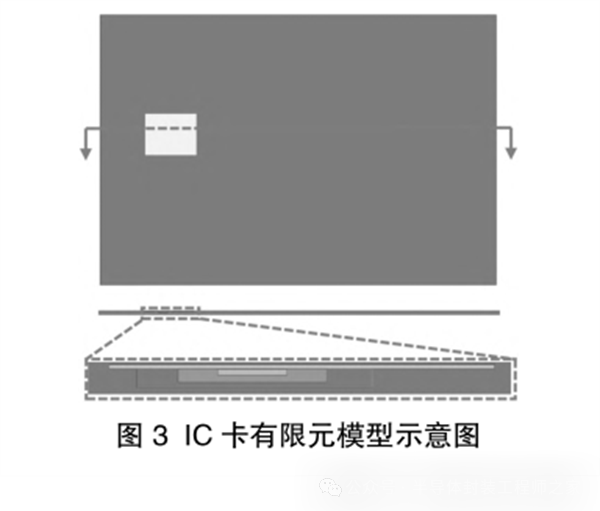

1.3 IC 卡有限元模型

IC 卡实际模型较为复杂,模型各部件存在尺寸跨度大的问题,若按照 IC 卡实物图进行有限元建模,建模难度大,因此对模型进行了相应的简化和等效。首先 IC 卡的各部件除了 EMC 层外,其他部件可以看作是薄板,实际情况中 EMC 层类似水滴型,这种形状在建模时难度较大,因此等效为矩形。IC 卡中的键合线因直径只有 25μm 或更细,建模时特意进行了忽略。最终建立 IC 卡有限元模型如图 3。

1.4 模型网格划分及网格收敛性验证

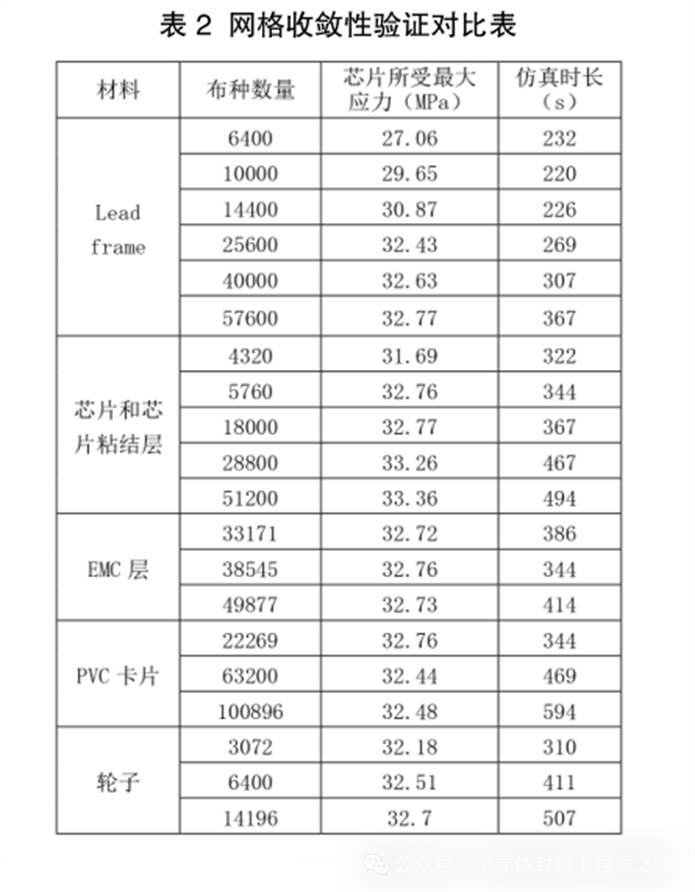

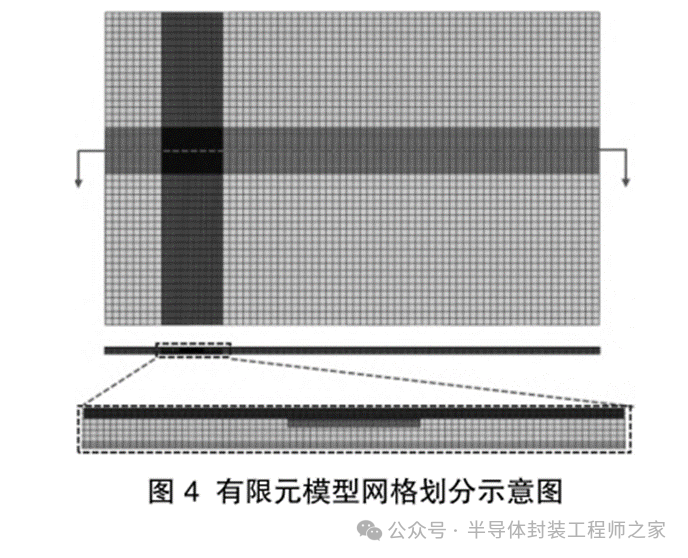

因 IC 卡有限元模型涉及部件较多,有些部件不是主要关注部件,例如 PVC 卡片远离芯片的部分。因此对 PVC 卡片进行分区划分时,每个区域网格布种数量不一致。PVC 空腔部分要与 Lead frame和封装后芯片的胶体层接触,接触部分网格布种数量与 Lead frame 的网格布种数量一致,以保证在有限元仿真过程中应力和位移在接触面上很好地传递,使结果更加准确;对于主要关注部件——— 芯片,网格布种数量相应加密,芯片粘接层与芯片、Lead frame(含铜基材、环氧材料、粘接剂)的网格布种数量一致 [3] 。

对模型进行网格收敛性验证,选出合适的网格数量进行划分。网格收敛性计算通过改变芯片、Lead frame 等各个部件的网格布种数量,查看芯片应力变化,当网格数量和计算时长适中且计算结果没有太大改变时,该网格数量即为仿真时所适用的数量。表 2 为网格收敛性验证对比表。

根据表中数据最终选择的有限元网格模型包括217319 个单元、283271 个节点。图 4 是有限元模型网格划分示意图。

2 基于动力学的三轮测试仿真结果分析

2.1 动力学仿真参数设置

根据《GB/T 17554.3-2006 识别卡测试方法第三部分带触点的集成电路卡及其相关接口设备》,三轮测试 IC 卡机械强度要求设置动力学仿真所需参数,包括 IC 卡插入速度、IC 卡插入初始位置和终止位置的确定等。以下是 IC 卡三轮测试操作要求:

(1)将带有芯片的卡片放在机器测试滚轮之间,将芯片在三个钢制滚轮间循环滚动;

(2)芯片面向上时,滚动 50 次;

(3)芯片面向下时滚动 50 次,循环频率均为0.5 Hz;

(4)卡片滚动时芯片上需加一定重量的力,经过往复循环测试后验证卡片中的芯片功能是否正常。标准中规定所加的力是 8 N,实际测试时可以进行 8N、12N、15N 等强度的测试。

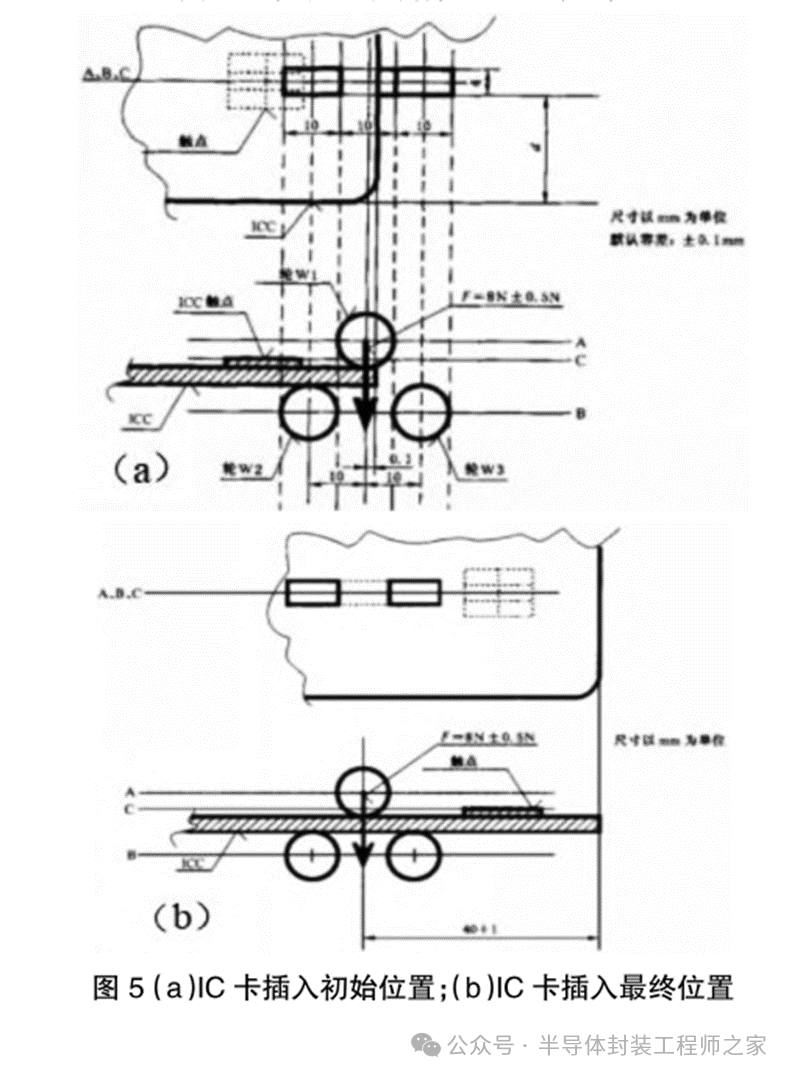

图 5 为 IC 卡插入初始位置和终止位置示意图。

从图 5 中可以看出,三个测试滚轮的直径为10mm,测试过程中滚轮厚度方向中心线与 IC 卡Lead frame 中心线保持一致,IC 卡插入初始位置上侧滚轮垂直方向中心线与 IC 卡一侧边缘相距0.1mm,最终插入 40mm,由插入距离和三轮测试循环频率可以算出 IC 卡插入速度为 40mm/s,测试过程中上侧滚轮对 IC 卡施加垂直向下 8N 的力。IC 卡的一端受三轮测试仪夹持装置的夹持进行插拔测试,这也是仿真过程中对 IC 卡施加的边界条件。

2.2 动力学仿真及危险位置确定

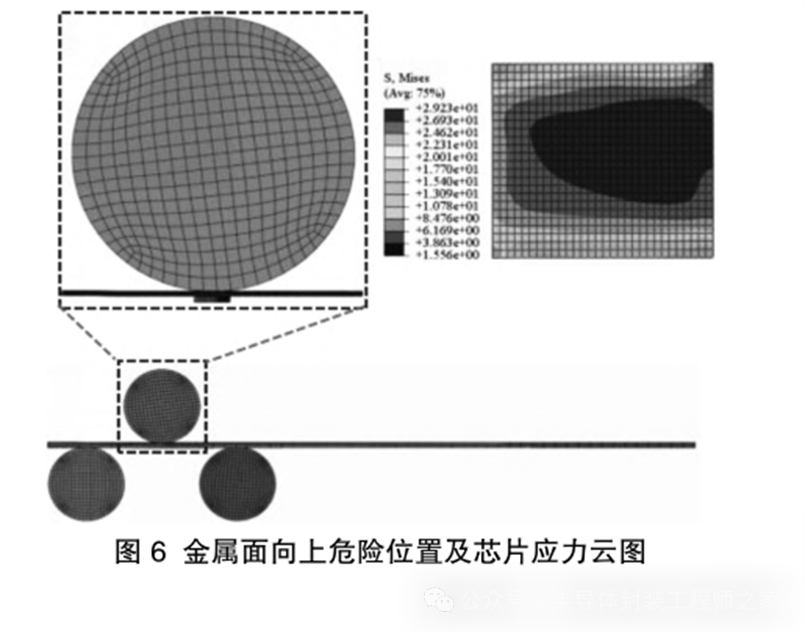

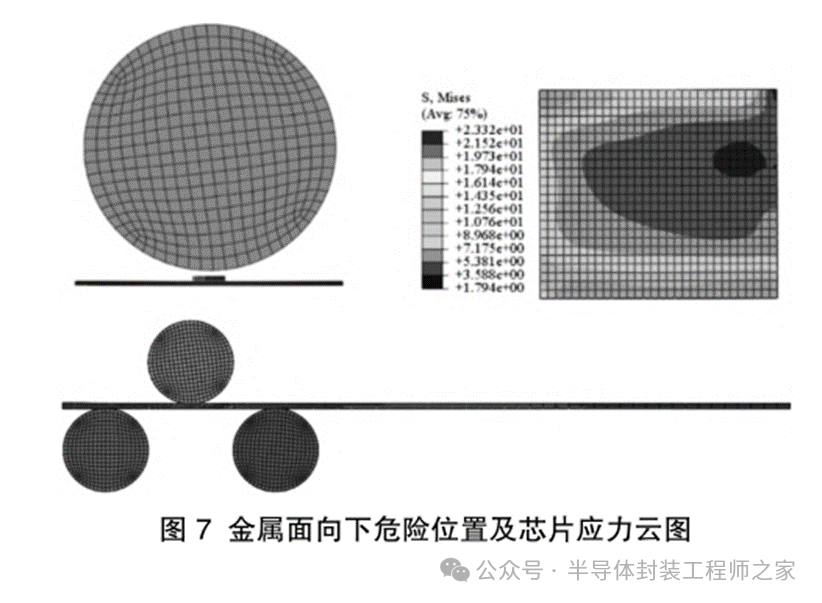

整体仿真思路:将 IC 卡金属面向上和金属面向下的测试过程进行动力学仿真,提取 IC 卡和芯片动态应力云图,找到芯片应力最大位置,将该位置视为危险位置,对危险位置进行重新建模,通过静力学仿真对比不同工况下芯片的受力情况。通过动力学仿真找到的两组危险位置如图 6 和图 7 所示:

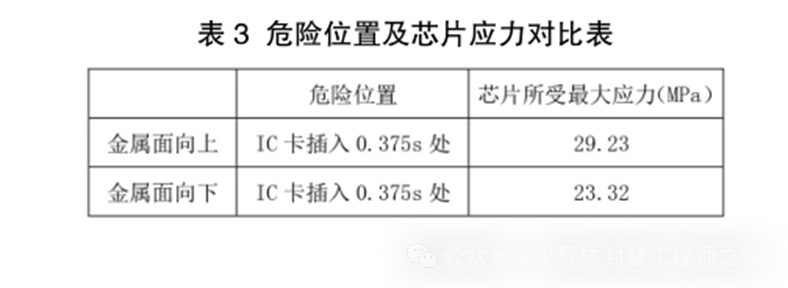

表 3 展示了金属面向上,IC 卡插入 0.375s 处芯片受力更大,将此位置确定为危险位置,基于动力学仿真的结果,对卡插入 0.375s 时刻的位置建模,进行后续的多因素仿真分析。

3 基于静力学的IC 卡多因素仿真结果分析

3.1 仿真中考虑的设计因素及设计水平

考虑多因素对芯片应力的影响时选用正交设计法,原理是根据正交性从全面试验中挑选出部分有代表性的点进行试验,这些有代表性的点具备均匀分散、齐整可比的特点,最后可以用极差分析方法对结果进行处理,得到各因素的影响主次关系。

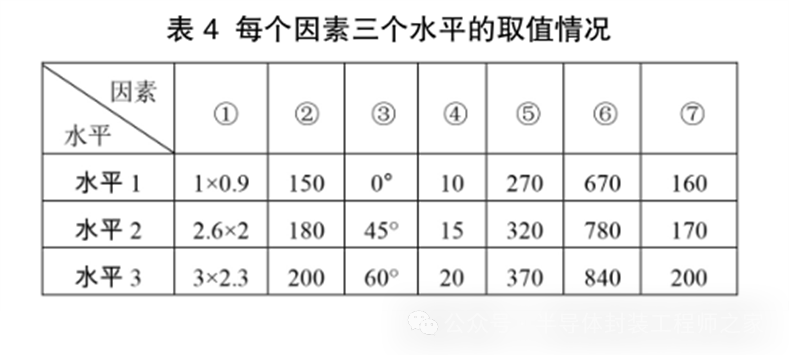

本次正交设计考虑的有七个因素,包括芯片大小(单位 mm,记为因素①)、芯片厚度(单位μm,记为因素②)、芯片偏转角度(单位。 ,记为因素③)、芯片粘接胶厚度(单位μm,记为因素④)、EMC 层厚度(单位μm,记为因素⑤)、PVC 厚度(单位μm,记为因素⑥)、Lead frame(常称作“条带”,单位 μm,记为因素⑦)等,每个因素选取三个水平,每个水平的取值情况见表 4,各个取值是结合实际产品规格及生产经验获得。

查询正交设计表格,本次选择的是一个 18 次的正交试验。

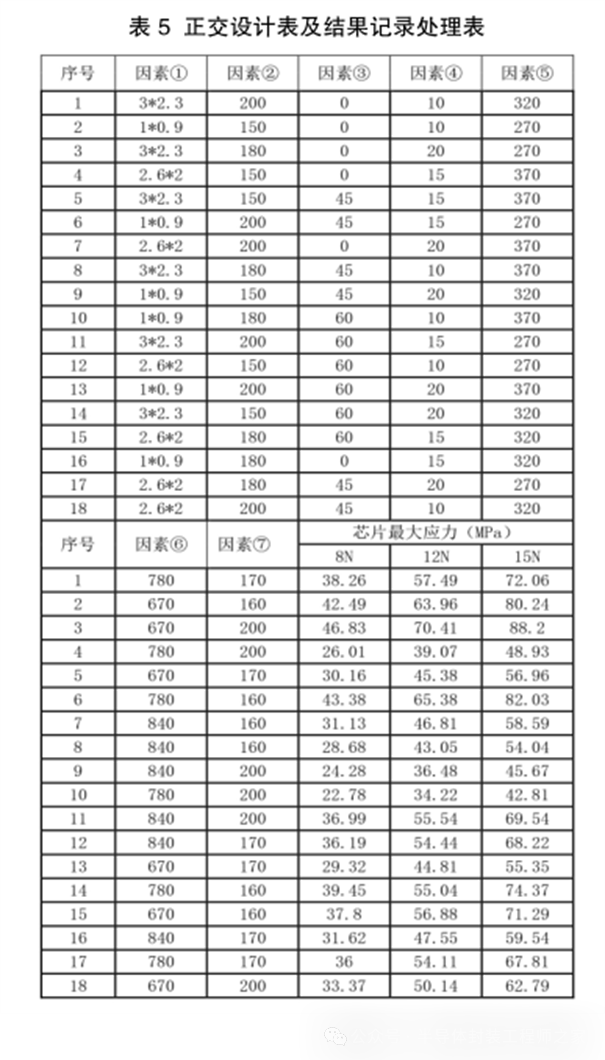

因智能卡应用广泛,如银行卡、电信卡、社保卡等,以及各个企业对质量管控的差异,实际确定产品质量时,经常进行不同工况下的试验。因此我们对每组试验安排了 3 个工况下的静力学仿真:上侧滚轮施加 8N、12N 和 15N 的工况,累积共进行 54 次仿真运算。通过后处理提取芯片应力云图,并找到芯片上所受最大应力,记录在表 5 中,并对结果进行极差分析,以上侧滚轮施加 8N 的力为例进行分析,找到各因素的影响主次关系。

以上侧滚轮施加的不同机械测试强度计算各因素的每一个测试强度的应力总和 K(每因素的水平1、水平 2、水平 3,分别记为 K1、K2、K3)、计算各因素不同水平下的每一个测试强度平均应力 k(每因素的水平 1、水平 2、水平 3,分别记为 k1、k2、k3)、计算各因素不同水平下的的每一个测试强度平均应力的极差 R(R= max {k1,k2,k3}-min{k1,k2,k3})。依据R 值的大小关系,判断各因素对机械强度的影响程度。判断规则为 R 值越大,影响程度越大。K、k、R 计算结果如表 6。

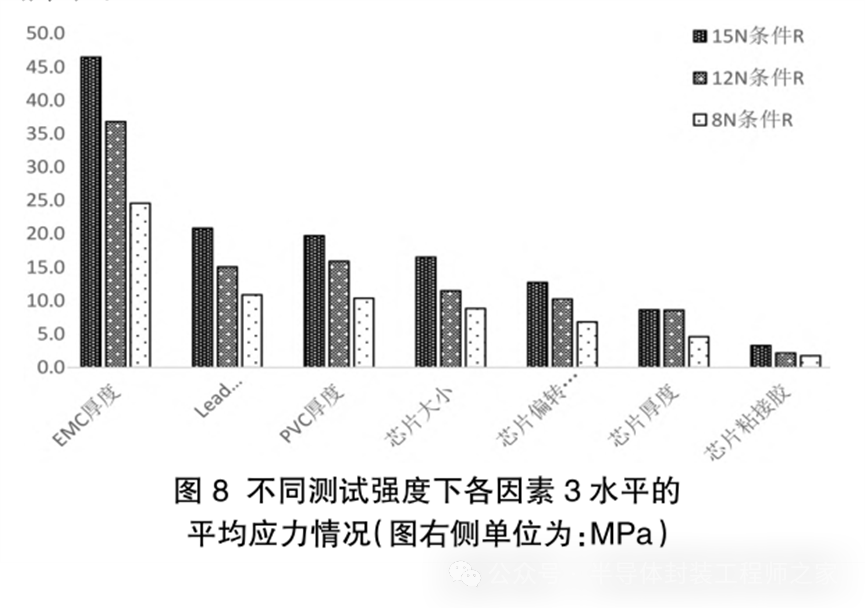

对 8N、12N、15N 分别计算 R 值,结果如图 8所示:

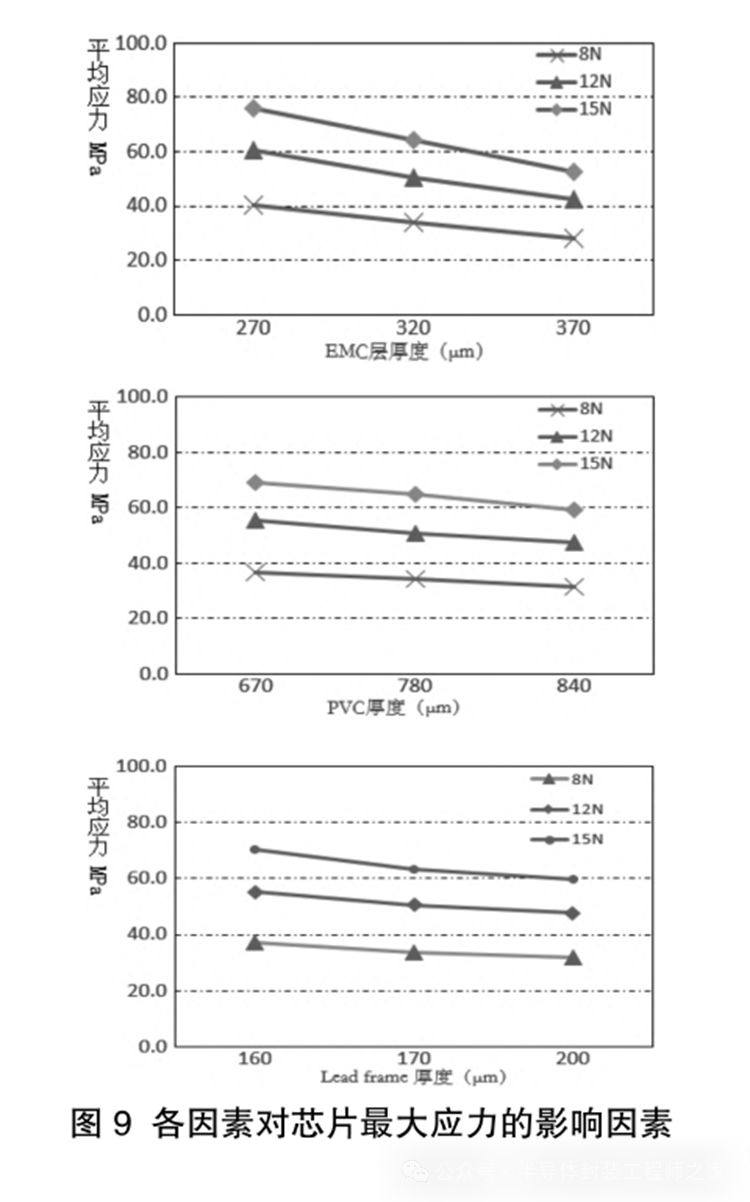

综合 8N、12N 和 15N 的分析结果可以看出,EMC层、PVC 卡片和 Lead frame 厚度的变化对芯片应力的影响较大,而芯片粘结层厚度的变化对芯片应力无较大影响。随着上侧滚轮施加力的增大,芯片上所受的应力也呈增大的趋势,但是上侧滚轮施加不同大小的力时,各个因素对芯片所受最大应力的影响趋势相同,通过 k 查看各因素对芯片最大应力的影响趋势,如图 9 所示,限于篇幅,图 9 只列出 EMC层、PVC 卡片和 Lead frame 厚度三个因素的趋势。

由图 9 可以看到,芯片最大应力随 EMC 层、PVC 卡片和 Lead frame 厚度的增加而减小。图 9 未展示的因素情况为:芯片最大应力随芯片偏转角度的增加先减小后增大,随芯片大小、芯片粘结层和芯片厚度的增加而增大。

3.2 芯片有关因素最大应力的影响分析

因为当前芯片的工艺技术、芯片的尺寸等更新迭代较快,而智能卡所用的封装材料几乎没有迭代。为了给予实际生产更多指导意义,特对芯片的应力情况单独进行了如下几个方面的分析。

3.2.1 芯片厚度对芯片最大应力的影响趋势分析

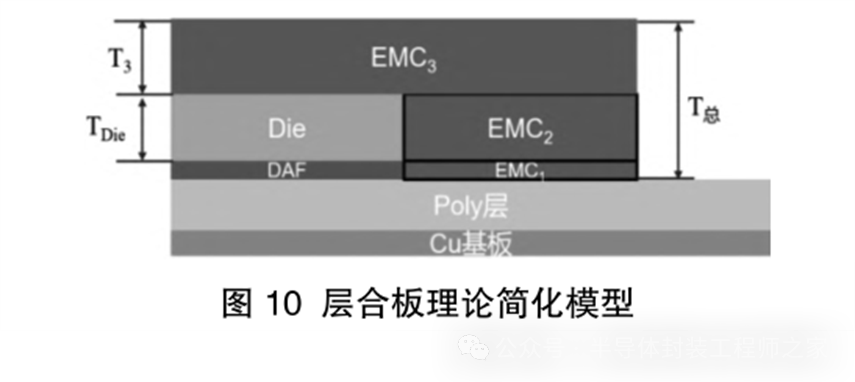

之前仿真分析时变化芯片厚度保持 EMC 层总厚度不变,如图 10 所示,考虑到 EMC 层和芯片的厚度变化可能存在交互作用,因此采用经典层合板理论并做了两组对比仿真,即固定 EMC 3 厚度 T 3 和固定 EMC 层总厚度 T 总 ,变化芯片厚度查看芯片所受最大应力的变化趋势。

固定 EMC 层总厚度(T 总 )时,仿真得到了三组芯片不同厚度时芯片的最大应力。

固定胶体上 EMC 3 层总厚度时,仿真得到了三组芯片不同厚度时芯片的最大应力。

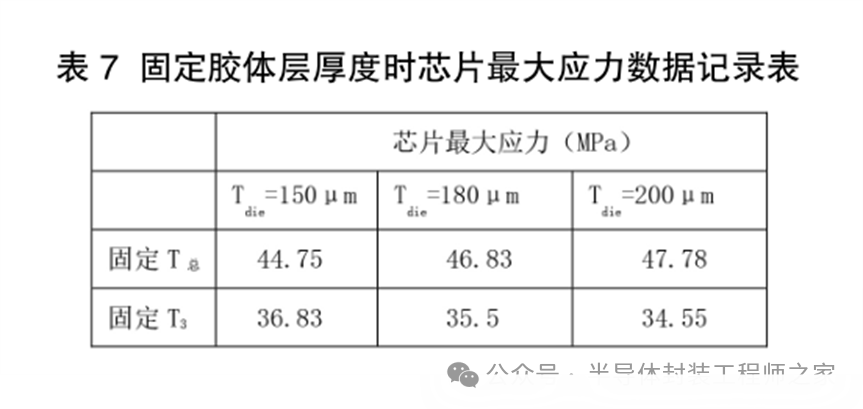

以上数据记录如表 7 所示。

由表 7 可以看到,固定 EMC 层总厚度时,芯片最大应力随芯片厚度增加而增大,当固定 EMC 3 层厚度时,芯片最大应力随芯片厚度增加而减小。

3.2.2 不同工况下芯片的受力分析

在仿真软件中,查看不同工况下芯片应力云图,发现当上侧滚轮施加的力增大时,芯片所受应力整体呈现增加趋势,但是应力分布趋势相同,具体受力情况读者可以参考表 5 进行分析。

在仿真软件中,对比所有试验组的芯片应力云图,发现芯片受力较大的面是与 EMC 层接触的面,且芯片所受最大应力处于该面或者该面的边角处。

3.2.3 不同偏转角度时芯片的受力分析

选取芯片大小 3mm×2.3mm,在仿真软件中,对比不同偏转角度时芯片的应力云图,发现芯片所受最大应力先减小后增大。芯片旋转到 45。 时,芯片所受应力最小。

3.2.4 芯片不同大小时芯片应力分布情况

选取偏转角度为 0。 ,在仿真软件中,对比芯片不同大小时芯片的应力云图,发现应力在芯片表面的分布情况不受芯片大小的影响。

4 结论

通过以上分析,可取得以下结论及 IC 卡集成电路芯片机械强度提升方法:

(1)EMC 层、Lead frame 和 PVC 卡片厚度的变化对芯片最大应力影响显著,且随着这三个部件厚度的增加芯片所受最大应力减小,芯片粘结层厚度变化对芯片最大应力无较大影响。因此增加 PVC 厚度、EMC 层厚度、Lead frame 的厚度可以提升智能卡机械强度的表现。特别是 EMC 层厚度,在封装条件允许的情况下,应采取较大的 EMC 层厚度值。

(2)芯片与 EMC 层接触的面是芯片受力较大的面,且芯片所受最大应力在该面或该面的边角处。推测对芯片表面进行适当的改善,也是提升智能卡机械强度表现的方法。

(3)芯片大小相同时对芯片进行偏转,芯片所受最大应力先减小后增大,且芯片受力较大的区域与滚轮下压的区域一致。因此,芯片封装时适当旋转角度,例如 45。 ,可以提升智能卡机械强度的表现。

(4)当固定 EMC 总厚度时变化芯片厚度,随着芯片越厚芯片最大应力越大;当固定 EMC 3 厚度时变化芯片厚度,随着芯片越厚芯片最大应力越小。因此,芯片厚度增加,可以提升智能卡机械强度的表现,在芯片封装时在情况允许下,应采取较大的芯片厚度值。

审核编辑:刘清

-

六相感应电机转子感应电压有限元分析与研究2025-06-10 269

-

基于有限元模型的IC 卡芯片受力分析研究2024-02-25 1358

-

微环隙带压下套管受力和位移的有限元计算模型2021-04-30 765

-

如何有效的学习CAE有限元分析2020-07-07 1667

-

基于Ansoft的开关磁阻电机有限元分析与研究2017-01-21 1173

-

基于多维测力台的有限元分析研究2012-02-16 853

-

有限元分析讲座2011-05-06 690

-

有限元分析及应用_曾攀2011-05-02 2164

-

【PDF】matlab有限元法计算分析程序编写2011-02-28 7288

-

膜式空气弹簧非线性弹性特性有限元分析2009-08-23 1070

-

[转帖]压电效应的有限元分析及压电悬置控制方法的研究(硕士论文)2009-03-20 3834

-

有限元分析2008-06-17 6107

全部0条评论

快来发表一下你的评论吧 !