半导体先进封装技术之CoWoS

制造/封装

描述

过去数十年来,为了扩增芯片的晶体管数量以推升运算效能,半导体制造技术已从1971年10,000nm制程进步至2022年3nm制程,逐渐逼近目前已知的物理极限,但随着人工智能、AIGC等相关应用高速发展,设备端对于核心芯片的效能需求将越来越高; 在制程技术提升可能遭遇瓶颈,但是运算资源需求持续走高的情况下,透过先进封装技术提升芯片之晶体管数量就显得格外重要。

半导体先进封装技术

这两年「先进封装」被聊得很多,「封装」大概可以类比为对电子芯片的保护壳,保护电路芯片免受外界环境的不良影响。当然芯片封装还涉及到固定、散热增强,以及与外界的电气、讯号互连等问题,而「先进封装」的核心还在「先进」二字上,主要是针对 7nm 以下晶圆的封装技术; 然而,人工智能浪潮下,带动AI伺服需求成长,也带动英伟达GPU绘图芯片需求,而GPU的CoWoS先进封装产能供不应求,那究竟什么是CoWoS?

什么是CoWoS?

CoWoS 是一种 2.5D、3D 的封装技术,可以分成「CoW」和「WoS」来看。「CoW(Chip-on-Wafer)」是晶片堆叠; 「WoS(Wafer-on-Substrate)」则是将芯片堆叠在基板上。

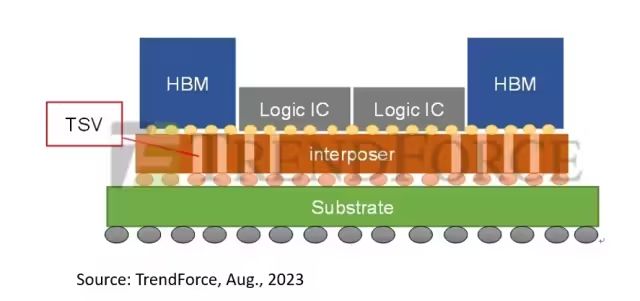

CoWoS 就是把芯片堆叠起来,再封装于基板上,最终形成 2.5D、3D 的形态,可以减少芯片的空间,同时还减少功耗和成本。下图为CoWoS封装示意图,将逻辑芯片及HBM(高带宽记忆体)先连接于中介板(Interposer)上,透过中介板内微小金属线来整合左右不同芯片的电子讯号,同时经由「砂穿孔(TSV)」技术来连接下方基板,最终透过金属球衔接至外部电路。

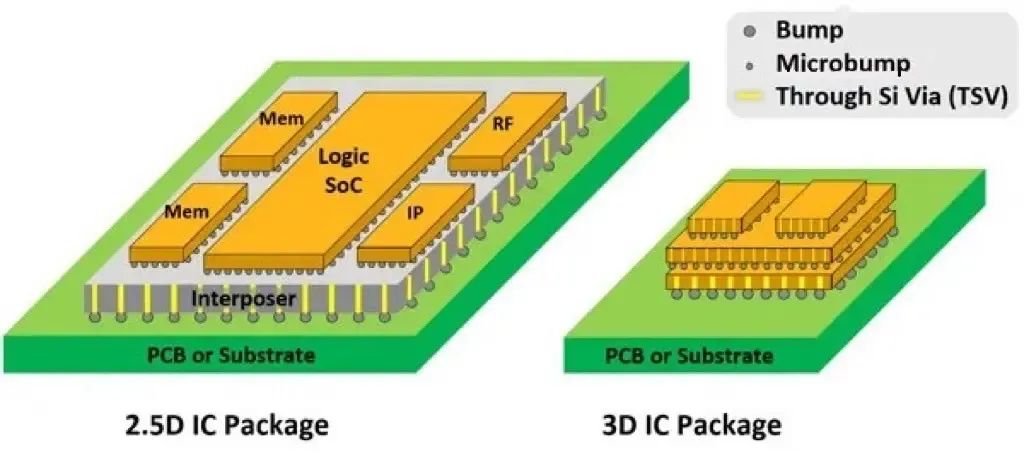

而2.5D与3D封装技术则是差别在堆叠方式。2.5D 封装是指将芯片堆叠于中间层之上或透过硅桥连接芯片,以水平堆叠的方式,主要应用于拼接逻辑运算芯片和高带宽存储器; 3D 封装则是垂直堆叠芯片的技术,主要面向高效能逻辑芯片、SoC 制造。

2.5D和3D封装的差异

先进封装,但不在封装厂完成!

说到先进封装,首先想到的会是台积电而非传统封测大厂,因为先进封装已经面临到 7nm 以下,而传统封装厂研发速度已无法跟进晶圆制程的脚步,其中 CoWoS 中的 CoW 部分过于精密,只能由台积电制造,所以才会造就这番景象。同时,台积电拥有许多全世界的高阶客户,为此「一条龙」的服务更能同时维持制程与封装部分的良率,未来面对高阶客户的交付工作也将更为极致。

CoWoS技术优势

相较于传统的芯片封装技术,CoWoS技术有以下几个优势:

高度密集:此技术可以使多个芯片在一个封装中实现高度集成,从而可以在更小的空间内提供更强大的功能。在需求高度集成的行业(例如互联网、5G、人工智能等)中得到广泛应用。

高速和高可靠性:由于芯片与晶圆直接相连,从而可以提高信号传输速度和可靠性。同时,此技术还可以有效地缩短电子器件的信号传输距离,从而减少传输时延和能量损失。

高性价比:CoWoS技术可以降低芯片的制造成本和封装成本,因为它可以避免传统封装技术中的繁琐步骤(例如铜线缠绕、耗材成本高等),从而可以提高生产效率和降低成本。

CoWoS的应用发展

高端芯片走向多个小芯片、内存,堆叠成为必然发展趋势,CoWoS 封装技术应用的领域广泛,包含高效能运算 HPC、AI 人工智能、数据中心、5G、物联网、车用电子等等,可以说在未来的各大趋势,CoWoS 封装技术会扮演着相当重要的地位。

其中,苹果公司在iPhone X中采用了CoWoS技术封装A11芯片,从而提高了设备的性能和效率。

早年,,,苹果iPhone处理器一直是三星的禁脔(luan:禁止别人染指的肉,比喻某种珍美的,仅独自享有),,,但台积电却能自2016年以后,成为苹果“A系列”处理器的独家供应商,从iPhone 7 A10 到iPhone 11 A13,其中A10是16nm工艺,A11是10nm技术,A12是7nm工艺,A13是7nm+EVU技术,按道理说,7nm+EUV也是三星掌握的技术,苹果为何偏偏选择台积电?关键之一,就是台积电开发的全新封装技术CoWoS以及InFO。

苹果

2013年量产的用于iPhone 5s的A7处理器由三星代工,黑色树脂里面,采用的是超薄PoP(Package On Package)封装,,直接将一颗1GB的DRAM与处理器叠在一起封装,

三星是目前唯一可以量产DRAM和处理器的公司,也拥有自营的封测厂,它来代工,整个A7处理器在一个屋顶下完成,在成本、整合上拥有巨大优势。

这个时候台积电导入了CoWoS技术,理论上可让处理器减掉多达70%的厚度。由于三星Galaxy系列智能手机对苹果手机威胁越来越大,同时苹果也想摆脱对三星的依赖,台积电这个时候对CoWoS技术做了简化,降低了成本,,设计出了InFo封装技术满足苹果需求,2016年11月一举拿下苹果iPhone 7订单,

此后到现在一直通吃苹果订单。

过去的芯片效能都仰赖半导体制程的改进而提升,但随着元件尺寸越来越接近物理极限,芯片微缩难度越来越高,要保持小体积、高效能的晶片设计,半导体产业不仅持续发展先进制程,同时也朝晶片架构着手改进,让芯片从原先的单层,转向多层堆叠。也因如此,先进封装也成为延续摩尔定律的关键推手之一,在半导体产业中引领浪潮。

中介层(Interposer)分类

有源与无源

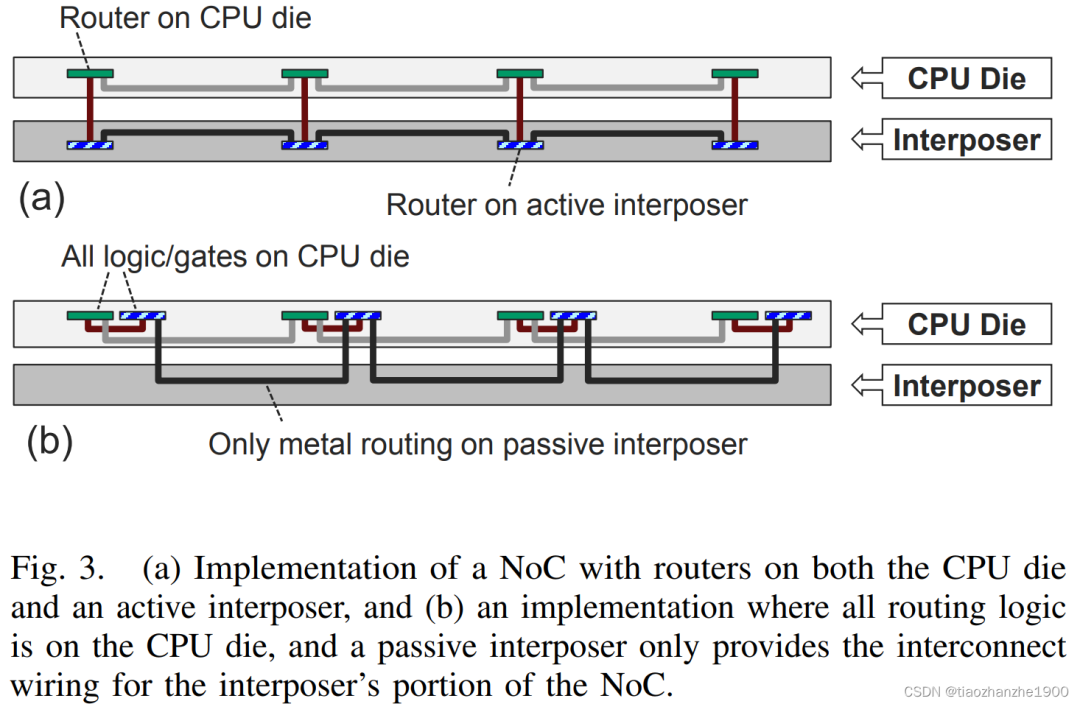

passive interposer: interposer上没有任何的晶体管,仅仅走线

active interposer: interposer上可以集成处理逻辑,如router logic

台积电根据中介层(interposer)的不同,将其“CoWoS”封装技术分为三种类型。一种是“CoWoS_S(Silicon Interposer)”,它使用硅(Si)衬底作为中介层。这种类型是2011年开发的第一个“CoWoS”技术,在过去,“CoWoS”是指以硅基板作为中介层的先进封装技术。

另一种是“CoWoS_R(RDL Interposer)”,它使用重新布线层(RDL)作为中介层。

第三个是“CoWoS_L(Local Silicon Interconnect and RDL Interposer)”,它使用小芯片(chiplet)和RDL作为中介层。请注意,“本地硅互连”通常被台积电缩写为“LSI”。

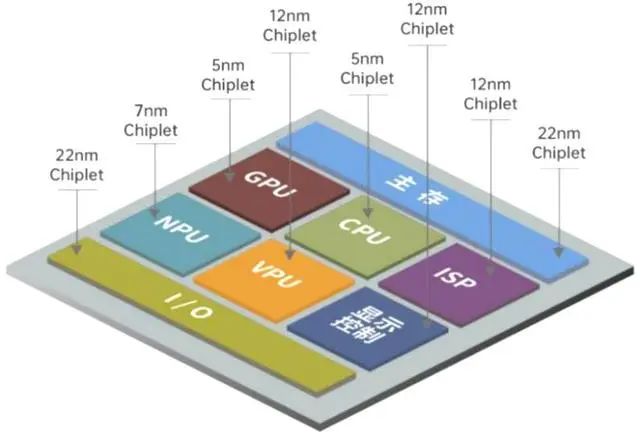

先进封装是实现Chiplet的前提

芯片上数据的输入和输出 (I/O) 是计算芯片的命脉。处理器必须与外部世界进行数据的发送和接收。摩尔定律使业界的晶体管密度大约每2年增加2倍,但 I/O数据的传输速率每4年才增加2倍,所以芯片需要容纳更多的通信或I/O点才能跟上晶体管密度的增加速度。

Chiplet对先进封装提出更高要求。在芯片小型化的设计过程中,需要添加更多I/O来与其他芯片接口,裸片尺寸有必要保持较大且留有空白空间,导致部分芯片无法拆分,芯片尺寸小型化的上限被pad(晶片的管脚)限制。并且单个晶片上的布线密度和信号传输质量远高于Chiplet之间,要实现Chiplet的信号传输,就要求发展出高密度、大带宽布线的“先进封装技术”。

芯片的工作是执行指令,处理数据,芯片间的互联需要巨大的带宽和超低的延时。既然单颗芯片的面积不能无限增加,将一颗芯片拆解为多颗芯片,分开制造再封装到一起是一个很自然的想法。芯片间的互联需要构建强大的数据通路,即超高的频率、超大的带宽、超低的延时,以台积电 CoWoS 技术为代表的先进封装技术也使之得到了解决。

审核编辑:黄飞

-

全面详解CoWoS封装技术特点及优势2023-07-11 12274

-

先进封装技术的发展趋势2018-11-23 3648

-

国内最近的三条半导体新闻首条先进半导体封装测试示范产线启动2019-04-20 6023

-

华进半导体作为国家级先进封装技术研发中心的探索之路2020-09-26 6360

-

浅谈半导体封装技术和先进封装技术解析2022-04-27 15361

-

CoWoS先进封装是什么?2023-07-31 5523

-

什么是先进封装?先进封装技术包括哪些技术2023-10-31 3827

-

半导体先进封装技术2024-02-21 1554

-

曝台积电考虑引进CoWoS技术2024-03-18 1447

-

什么是 CoWoS 封装技术?2024-06-05 1750

-

CoWoS封装产能飙升:2024年底月产将破4.5万片,云端AI需求驱动扩产潮2024-07-11 1451

-

什么是CoWoS封装技术?2024-08-08 9439

-

CoWoS先进封装技术介绍2024-12-17 4354

-

日月光扩大CoWoS先进封装产能2025-02-08 1195

-

半导体传统封装与先进封装的对比与发展2025-07-30 1016

全部0条评论

快来发表一下你的评论吧 !