网表时序仿真案例:浅说$width语法

电子说

描述

1.$width语法

在verilog中,$width是时序检查函数,用于检查脉冲的位宽是否符合要求。

$width ( reference_event , timing_check_limit , threshold [ , [ notify_reg ] ] ) ;

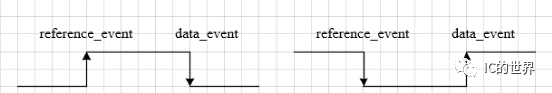

reference_event代表一个上升沿(下降沿)触发事件。

语法中隐形地表达了data_event。

data event = reference event signal with opposite edge。

如果reference_event为上升沿,则最近的一个下降沿是data_event,两者的时间间隔为脉冲宽度。

如果reference_event为下升沿,则最近的一个上降沿是data_event,两者的时间间隔为脉冲宽度。

图1:event示意图[1]

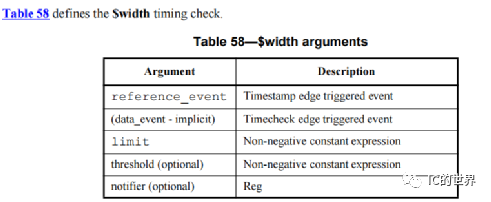

图2:参数说明[2]

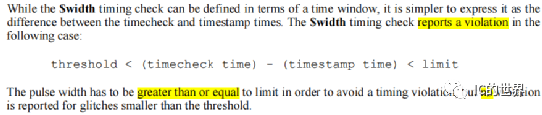

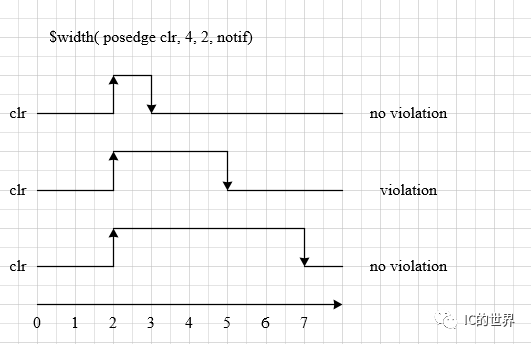

•期望的场景:脉冲宽度 >= limit

•不期望的场景:

○产生timing violation场景的:threshold < 脉冲宽度< limit

○不产生timing violation场景的:脉冲宽度

图2:width检测时序示意图[1]

NOTE:很多时候threshold的值为0.

2.案例说明

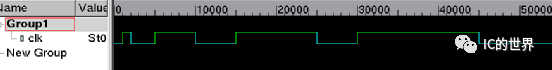

此案例中,使用的仿真工具为VCS,limit为 6000ps。小于6000ps的脉冲位宽均产生了Timing violation。

threshold为2000ps,位宽小于threshold的脉冲也产生了Timing violation,此处检查比协议要求得更加严格。

"/auto/asic/design/try/top/rtl/width_tb.v", 34: Timing violation in width_tb

$width( posedge clk:1000, : 2000, limit: 6000 );

"/auto/asic/design/try/top/rtl/width_tb.v", 34: Timing violation in width_tb

$width( posedge clk:5000, : 10000, limit: 6000 );

$finish called from file "/auto/asic/design/try/top/rtl/width_tb.v", line 10.

$finish at simulation time 100000

V C S S i m u l a t i o n R e p o r t

module width_tb;

reg clk;

initial begin

$fsdbDumpfile("width_tb.fsdb");

$fsdbDumpvars(0, width_tb);

#100;

$finish;

end

initial begin

clk = 1'b0;

#1;

clk = 1'b1;

#1;

clk = 1'b0;

#3;

clk = 1'b1;

#5;

clk = 1'b0;

#5;

clk = 1'b1;

#10;

clk = 1'b0;

#5;

clk = 1'b1;

#15;

clk = 1'b0;

end

specify

$width(posedge clk,6,2);

endspecify

endmodule

-

基于 FPAG xilinx vivado 仿真模式介绍2018-01-24 5625

-

什么是Modelsim的功能仿真和时序仿真?2019-09-20 4573

-

请问用什么语法可以实现这个max=val?2021-06-25 1545

-

视觉模块OpenMV浅说LED灯2021-07-20 1590

-

网表仿真与RTL仿真相比有何优势2021-11-04 5540

-

时序计算和Cadence仿真结果的运用2009-12-21 896

-

Modelsim的功能仿真和时序仿真2012-11-13 16400

-

modelsim仿真详细过程(功能仿真与时序仿真)2017-12-19 76690

-

基于ModelSim使用modelsim手动时序仿真教程2021-07-23 3331

-

时序分析概念min pulse width介绍2023-07-03 5288

-

时序仿真与功能仿真的区别在于2023-09-08 7393

-

时序仿真与功能仿真的区别有哪些?2023-09-17 8685

-

fpga时序仿真和功能仿真的区别2024-03-15 4054

-

浅说路灯智慧云盒网关2025-04-08 799

全部0条评论

快来发表一下你的评论吧 !