差分放大电路的缺点,你知道几个?

描述

1. 差分放大器结构

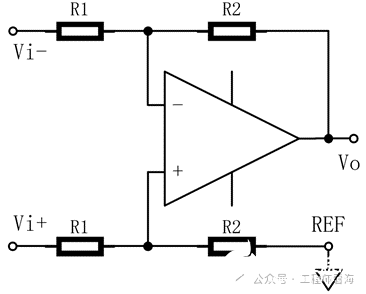

话不多说,直接干货,图1是差分放大电路的基本结构,由一个运算放大器和4个外围匹配电阻组成,常用来进行电流检测或差分信号放大,差分放大器有几个固有的弊端,如果不了解这些弊端,将影响我们的电路设计,看看这些弊端,你知道几个?(本文整理自看海的原创视频课程《运放秘籍》第二部:仪表放大器专项)

图1 差分放大电路

2. 差分放大器弊端一:输入阻抗低

差分放大器的输入阻抗非常低,这与它的匹配电阻相关,而且差分放大器两个输入端的阻抗并不对称。怎么计算两个输入端的输入阻抗呢?

如图1 中,计算Vi-的输入阻抗时,我们只看Vi-,忽略Vi+,参考图2 左图。此时的电路是一个反相放大的结构,由《运放秘籍》前期课程可知,反相放大电路的输入阻抗就约等于输入电阻R1。

图2 差分放大输入阻抗计算

计算Vi+的输入阻抗时,我们只看Vi+,忽略Vi-,参考图2 右图。此时的电路类似一个同相放大的结构,Vi+是被R1和R2分压后再被同相放大的,Vi+经过R1和R2到地,因此,Vi+的输入阻抗大约是电阻(R1+R2)的值。

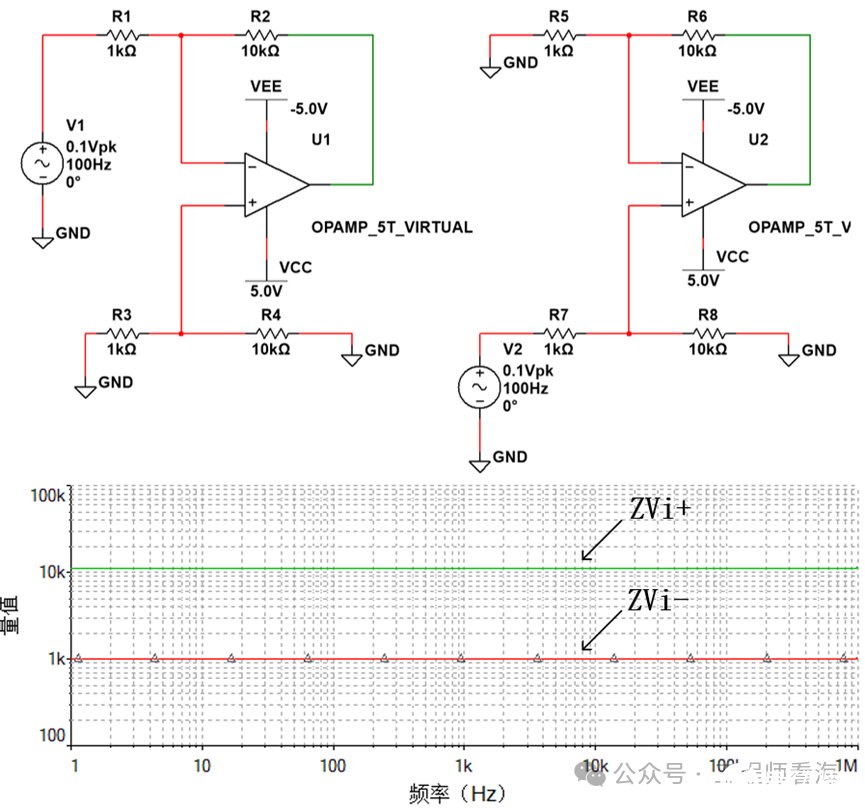

我们做下输入阻抗的仿真,见图3 ,Vi-的输入阻抗是1KΩ,Vi+的输入阻抗是11KΩ,与我们前文分析的一致,详细仿真方法参考《运放秘籍》完整内容。

图3 差分放大输入阻抗仿真

差分放大器的输入阻抗不但低,而且两个输入端的阻抗并不对称,如果连接到差分放大器的信号源的两个引脚源阻抗不匹配,也会降低CMRR,这就是差分放大电路的二:共模抑制比低。

看海的完整视频课程《运放秘籍》

【淘宝】

https://m.tb.cn/h.5H0RtTBtXal81GG?tk=EVntW95Izth CZ0002 「运放秘籍第二部辟地_运算放大器Multisim仿真视频教程_工程师看海」

3. 差分放大器弊端二:共模抑制比低

差分放大器最完美的状态是图1电路中的两个R1完全相等、两个R2完全相等,然而,我们无法找到两个阻值一模一样的电阻,常见的电阻也有1%的误差。这会使得电阻失配,将大大降低共模抑制比CMRR。

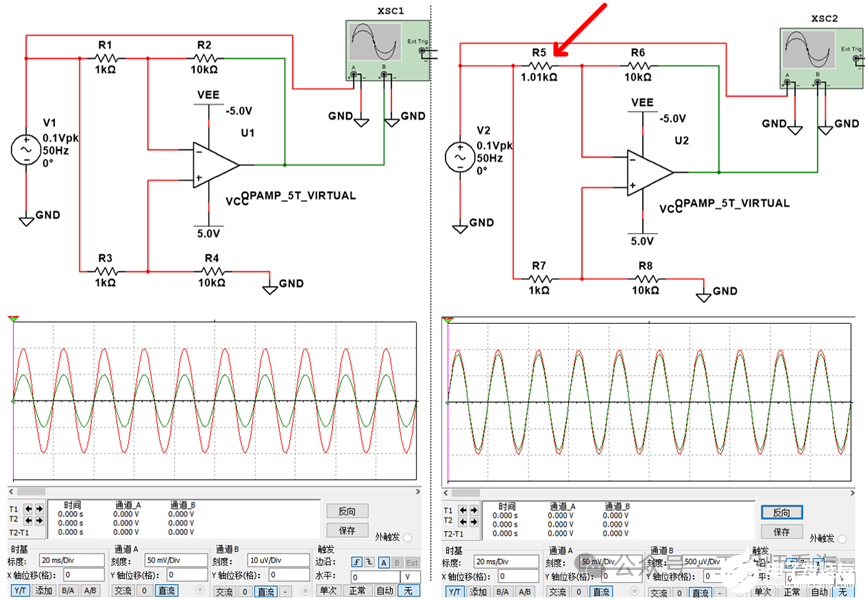

图4 中,我们简单体会下差分放大器的CMRR,左边仿真图中,电阻是完全匹配的,输入的共模信号是0.1V@50Hz,此时输出是10uV,也就是说0.1V的共模输入信号被转换成了10uV的输出信号(虚拟运放模型的CMRR是100dB),换句话说就是,在外围电阻完全匹配的情况下,差分放大器的CMRR并不是无穷大,这受限于运算放大器。

图4 差分放大CMRR与电阻失配

而图4右图中,我们只把其中的一个电阻,按照最大误差1%从1KΩ改成了1.01KΩ,则在相同共模输入的情况下,输出变成了大约1000uV,是左图的10uV的100倍。这就是电阻失配,将降低共模抑制比,使得抑制共模干扰的能力大大降低。

能不能增加差分放大电路的输入阻抗和共模抑制比?于是,就有了经典的3运放仪表放大器。

看海的完整视频课程《运放秘籍》

【淘宝】

https://m.tb.cn/h.5H0RtTBtXal81GG?tk=EVntW95Izth CZ0002 「运放秘籍第二部辟地_运算放大器Multisim仿真视频教程_工程师看海」

点击链接直接打开 或者 淘宝搜索直接打开

如果看到这里,请点赞、收藏、分享三连!

限时免费扫码进群,交流更多行业技术

审核编辑 黄宇

-

差分放大电路和差模放大电路相同吗2024-10-15 2083

-

恒流源差分放大电路有什么优点2024-08-02 3178

-

差动放大电路和差分放大电路一样吗2023-08-27 14752

-

什么是差分放大电路?差分放大电路的作用有哪些呢?2023-08-22 6588

-

什么是差分放大电路?差分放大电路如何抑制零漂电压稳定工作点2023-08-10 4865

-

差分放大电路的作用和特点 差分放大电路抑制零漂的原理分析2023-07-28 6673

-

教你轻松掌握差分放大电路2022-08-22 3717

-

差分放大电路的概念及作用2022-08-09 10674

-

差分放大电路为什么用了几个102电容?2019-05-06 3008

-

差分放大电路特点_差分放大电路的作用2018-03-21 121236

-

差分放大电路图2008-01-05 3107

全部0条评论

快来发表一下你的评论吧 !