调整MOSFET栅极驱动器以用于GaN FETs

描述

氮化镓(GaN)场效应晶体管已经彻底改变了电力电子行业,具有比传统硅MOSFETs更小的尺寸、更快的开关速度、更高的效率和更低的成本等优势。然而,GaN技术的快速发展有时超过了专用GaN专用栅极驱动器和控制器的发展。因此,电路设计人员经常求助于为硅MOSFETs设计的通用栅极驱动器,从而需要仔细考虑各种因素以获得最佳性能。

GaN晶体管与Si MOSFETs

与硅MOSFETs相比,eGaN FETs表现出不同的特性,影响其与专为后者设计的栅极驱动器一起工作。一些主要差异包括:

较低的栅极电压水平:eGaN FETs要求导通时的栅极电压为5 V,关断时的栅极电压为0 V,最大栅极额定值为6 V,这使得驱动栅极驱动器的电源必须进行相应设计。驱动器或控制器的欠压闭锁(UVLO)也应与5 V栅极驱动对齐。

更快的开关速度:Si MOSFETs的RDS(on)QG可能是GaN的3倍以上,RDS(on)QGD高达10倍。因此,开关节点上可能存在75 V/ns或更高的dv/dt,因此栅极驱动器需要不受这种压摆率的影响。更快的开关速度也会使寄生电感更加明显,因此设计中需要采用低电感布局技术。

更高的反向导通压降:与硅MOSFET不同,eGaN FETs没有寄生体二极管,但它们以更大的压降反向传导电流,与MOSFET的1 V相比约为2.5 V,这意味着栅极驱动器在整流开关的死区时间内可以看到更高的负开关节点电压。因此,栅极驱动器应包括自举过压管理,并且能够在低至-5 V的负开关节点电压下工作。

物理结构:eGaN FETs具有横向结构,而额定电压》20 V的Si MOSFETs通常是垂直器件。因此,引脚位置可能不同,使用Si MOSFET专用栅极驱动器时会带来布局挑战。GaN专用栅极驱动器设计为与大多数GaN晶体管布局兼容。将MOSFET驱动器用于GaN FET时的布局冲突要求理解设计中可能做出的权衡。

MOSFET栅极驱动器兼容性审查

在设计驱动GaN FETs的MOSFET栅极驱动器之前,它必须满足某些要求。

与5 V电源兼容:栅极驱动器必须与驱动级的5 V电源兼容,无论是外部稳压电源还是内部低压差稳压器(LDO)。

欠压锁定兼容性:UVLO必须与5 V驱动器级兼容。低端驱动器级的典型UVLO介于3.75–4V和高端的3.25 - 3.75 V之间。

压摆率抗扰度:栅极驱动器应表现出超过开关节点最大预期dv/dt的压摆率抗扰度,最好大于50 kV/ s,如果无法满足这一要求,可能需要以降低转换器效率为代价降低开关速度。

自举电源:许多MOSFET驱动器使用自举电路为上层器件驱动器供电,大多数驱动器使用自举二极管。只有使用外部自举二极管的栅极驱动器才适合与GaN FETs一起使用,这一点在建议中会很明显。内置LDO后置自举二极管的驱动器是首选。

死区能力:eGaN FETs出色的开关特性支持MHz范围内的工作条件,同时保持较高的转换器效率。因此,尽可能缩短死区时间(甚至低于10 ns)非常有益。一些为MOSFETs设计的控制器无法实现如此低的死区时间,从而抵消了GaN器件的优势。考虑使用GaN FETs的控制器时,优先考虑具有低死区功能的控制器。

转换MOSFET驱动器以使用GaN FETs

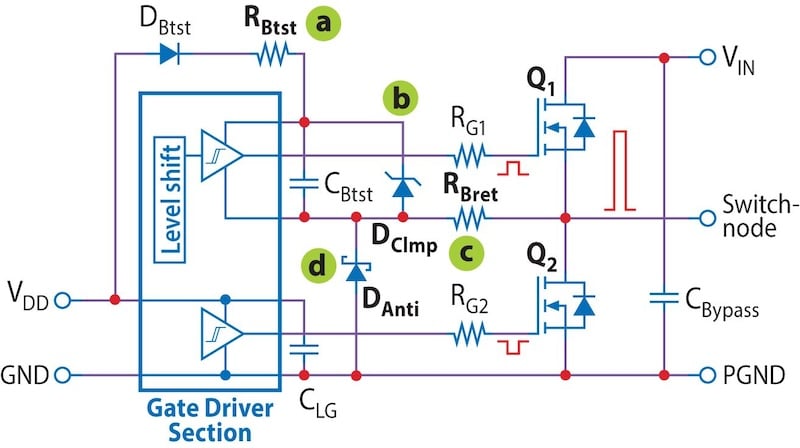

确定兼容的MOSFET驱动器后,可以实施以下步骤来确保与GaN FETs的最高兼容性。请参考图1了解详细信息以及附带的解释。除这些建议外,还应始终遵循通用GaN FET驱动建议。

自举二极管:用于外部自举二极管,使用尺寸、电容和额定电流尽可能小的肖特基二极管,如BAT54KFILM,并将其与限流电阻串联,如图1(a)所示。这肖特基二极管确保最低的电压损失(V嘘电视节目盐水),使驱动器电压尽可能接近5 V。当任何保护电路启动时,小串联电阻会限制自举二极管中的电流。应当注意,该电阻可能会影响自举电容再充电所需的最小脉冲宽度。自举二极管后集成5 V LDO的驱动器不需要串联电阻或随后介绍的额外电路保护,因为这些建议已变为可选。

自举箝位:自举电容两端的齐纳二极管可以将电压箝位在6 V以下,以防止低端器件反向导通时的死区期间过压。齐纳电压为5.6 V的MM5Z5V6ST1G就是一个很好的例子,如图1(b)所示。自举电容和齐纳二极管应尽可能靠近彼此放置,并尽可能靠近栅极驱动器。

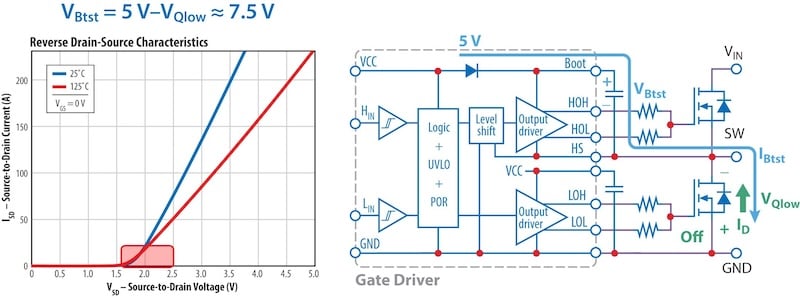

栅极返回电阻:如图1(c)所示,在低端GaN FET反向导通期间,为高端FET增加一个栅极返回电阻可以保护IC免受开关节点上较大负电压的影响,如图2所示。该电阻值还取决于上部器件门电路所需的关断阻尼和时序。使用该电阻要求栅极的导通电阻等效降低,以补偿其电阻。

图1(a-d)。

推荐用于GaN FET兼容性的Si栅极驱动器增强。图片由提供

博多的电力系统

[PDF]

4.反向导通箝位:如图1(d)所示,一个反并联肖特基二极管跨接在半桥拓扑的低端,可以限制驱动器承受的负开关节点电压的幅度。当开关节点降至低于参考地的特定电压以下时,一些栅极驱动器变得敏感或甚至可能失效。该二极管的额定电压应与低端GaN FET的额定电压相匹配。额定电流可能显著低于低端FET,因为它仅在空载时间导通,因此应根据其额定脉冲电流进行选择。

控制器IC和集成栅极驱动器

控制器IC将许多功能集成到单个IC中,包括栅极驱动器。其中一些IC可能不支持GaN器件的最佳布局,因此了解设计折衷以实现最佳性能非常重要。

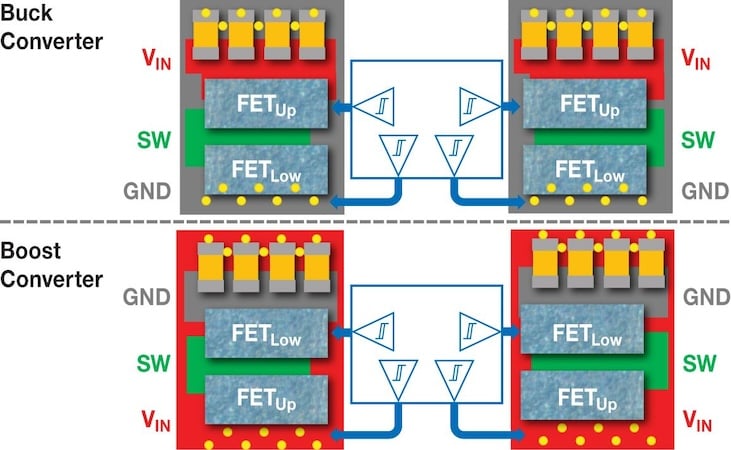

使用GaN FETs设计功率级时,务必遵循一般布局建议。考虑的顺序仍然是共源电感(CSI),然后是电源和栅极环路电感。这意味着功率级基本上设计成一个模块,栅极信号连接到控制器IC,如图3所示。功率级模块建议布局的变化有助于选择适合控制器IC的最佳模块。在2相控制器的情况下,可能需要在两种可选设计之间进行选择。设计标准是将通常为硬开关的控制FET(开关)置于同步整流器之上。例如,在降压转换器中,应优化布局,使高端FET栅极环路中的寄生电感最小。对于中的低端FET也是如此升压转换器如图3所示。

图二。

死区时间内的自举充电路径。图片由提供者使用

博多的电力系统

[PDF]

图3。

推荐布局。图片由提供者使用

博多的电力系统

[PDF]

调整MOSFET栅极驱动器以用于GaN FETs

为了使MOSFET栅极驱动器适用于GaN FETs,设计人员必须确保兼容性,实施建议的修改,并优化布局以充分发挥的潜力氮化镓技术。仔细关注这些指南,设计人员可以使用通用栅极驱动器和控制器,为成功大规模生产铺平道路GaN基功率转换器.

审核编辑 黄宇

-

最实用的栅极驱动芯片选型指南2019-01-29 30818

-

TEA2017AAT与 GaN MOSFET如何实现负栅极电压?2026-05-06 41

-

为什么我们需要#mosfet栅极驱动器?jf_97106930 2022-08-27

-

高速栅极驱动器助力实现更高系统效率2019-03-08 2434

-

栅极驱动器是什么2021-01-27 3969

-

栅极驱动器是什么,为何需要栅极驱动器?2021-07-09 6359

-

如何利用氮化镓实现高性能栅极驱动?2023-02-24 12595

-

ADI隔离栅极驱动器和WOLFSPEED SiC MOSFET2021-05-27 1499

-

MOSFET和IGBT栅极驱动器电路的基本原理2021-11-29 3514

-

用于SiC MOSFET的栅极驱动器2022-08-03 2897

-

用于电机驱动的MOSFET驱动器2023-08-02 2496

-

隔离式栅极驱动器的演变(IGBT/SiC/GaN)2023-12-18 1137

-

适配MOSFET栅极驱动器以驱动GaN FETs2024-02-29 2217

-

栅极驱动器芯片的原理是什么2024-06-10 4265

-

什么是栅极驱动器?栅极驱动器的工作原理2024-07-19 26184

全部0条评论

快来发表一下你的评论吧 !