台积电它有哪些前沿的2.5/3D IC封装技术呢?

描述

2.5/3D-IC封装是一种用于半导体封装的先进芯片堆叠技术,它能够把逻辑、存储、模拟、射频和微机电系统 (MEMS)集成到一起,是未来封装的发展方向。作为晶圆代工一哥的台积电,是半导体技术革新的领头羊,那么它有哪些前沿的2.5/3D IC封装技术呢?

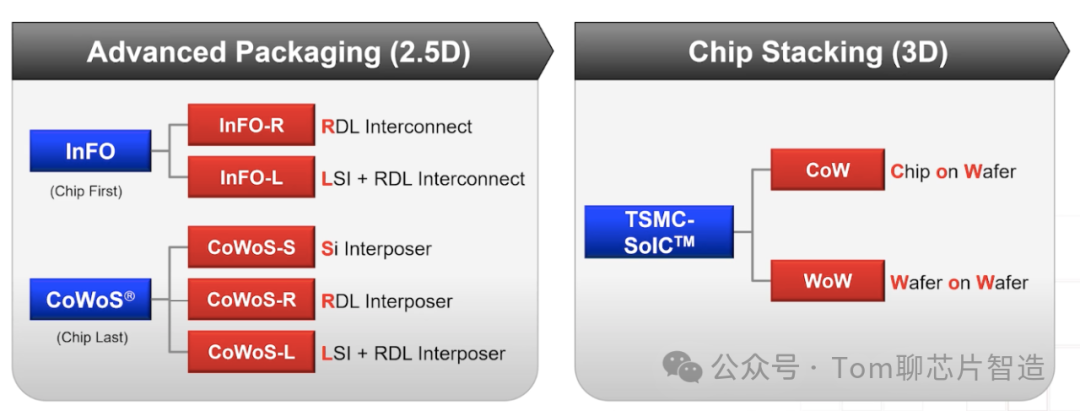

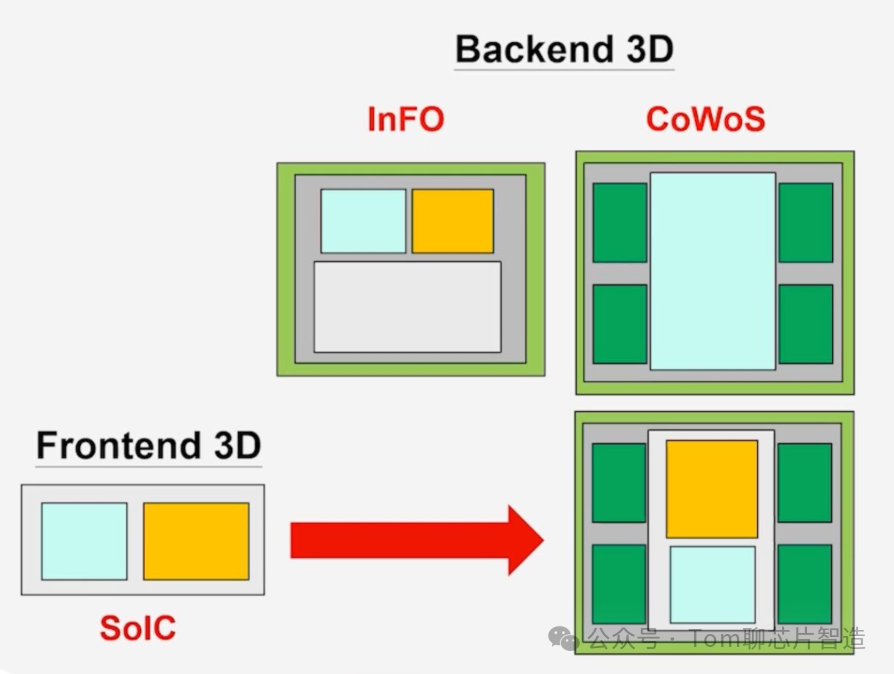

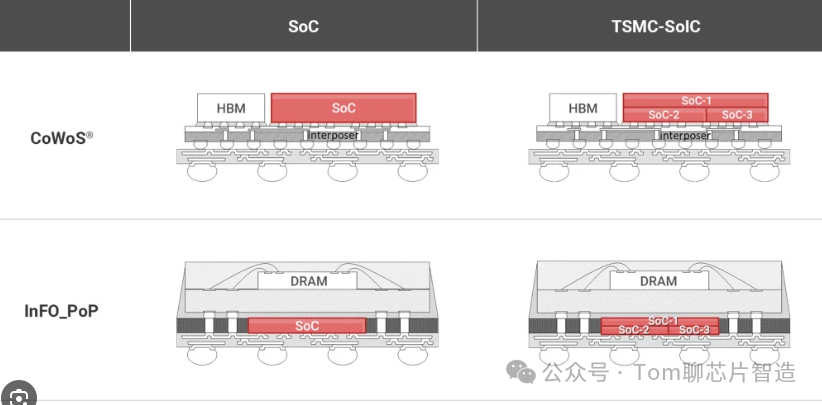

台积电的2.5/3D IC 封装主要有TSMC-SoIC,InFO,CoWoS三种类型。

TSMC-SoIC

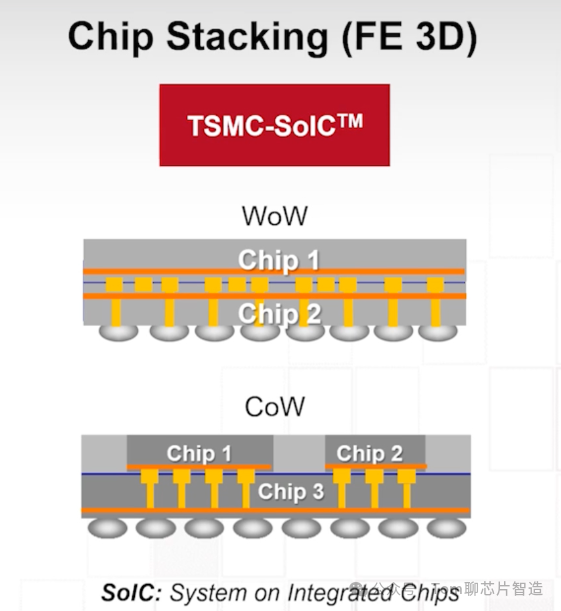

TSMC-SoIC(System on Integrated Chips),能对10纳米以下的制程进行晶圆级的集成,最关键的创新是采用了无凸点(no-Bump)的键合结构。

传统的3D IC封装技术通常用微凸点(micro-bumps)作为芯片间的互连结构。然而,微凸点的间距限制了互连密度,因而限制了整体的集成密度和性能。

相比之下,SoIC技术采用了无凸点的直接键合技术,这种技术能够减小芯片间距离,从而弥补了传统3D IC封装的短板。

TSMC的SoIC又包含了CoW(Chip-on-Wafer)和WoW(Wafer-on-Wafer)两种形式。

CoW是将单独的芯片(Chip)直接键合到一个待加工的晶圆(Wafer)上,而WoW则是将整个晶圆与另一个晶圆直接堆叠并键合。

InFO

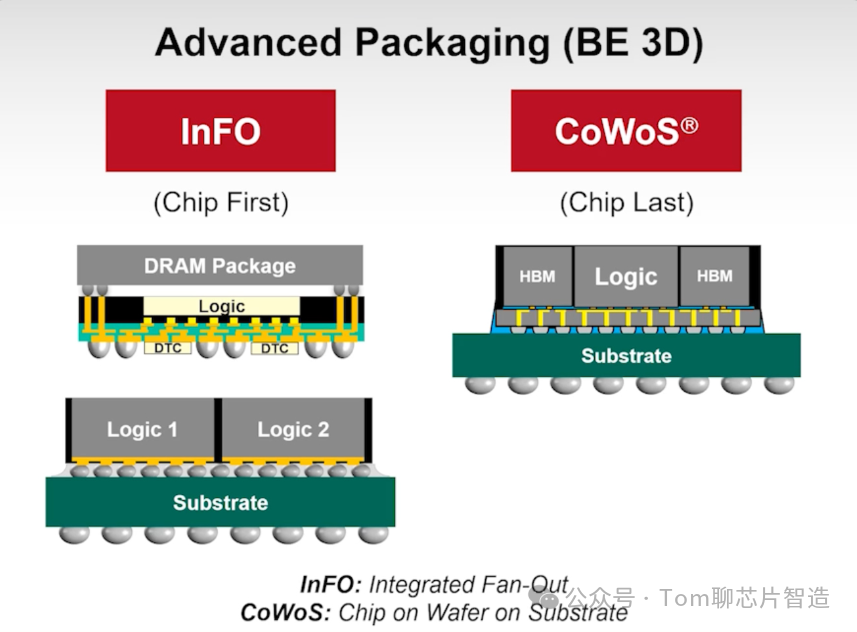

InFO(Integrated Fan-Out),是一种先进的扇出型晶圆级封装(FOWLP)技术。InFO技术通过在晶圆上实现裸晶的扇出式布线(Fan-Out),使得芯片不需要传统的基板,直接在芯片的外围形成更多的I/O连接点。随着技术的发展,TSMC推出了几种不同的InFO技术变体,以满足不同应用的需求,包括InFO-PoP、InFO-oS、InFO-LSI等。

CoWoS

CoWoS(Chip-on-Wafer-on-Substrate)是一种先进的2.5D封装技术,它是将多个不同功能的芯片首先封装到一个硅转接板上,利用这个硅转接板上的高密度布线实现芯片间的互连,然后整个结构再被安装到一个更大的封装基板上。CoWoS包括CoWoS-S,CoWoS-R,CoWoS-L. TSMC-SoIC,InFO,CoWoS之间的关系?

审核编辑:刘清

-

2.5D和3D封装技术介绍2025-01-14 3619

-

台积电CoWoS封装A1技术介绍2024-12-21 5341

-

5G手机全球出货量首次超过4G手机 台积电3D Fabric技术如何助力手机和HPC芯片2022-09-20 3116

-

台积电开发SoIC新3D封装技术,中芯国际考虑跟随2020-12-30 3419

-

台积电在台湾进行3D硅片制造技术研发2020-11-27 1985

-

谷歌和AMD帮助台积电测试和验证3D堆栈封装技术,有望成为首批客户2020-11-23 2401

-

台积电3D封装芯片计划2020年量产2020-11-20 3059

-

台积电揭露3D IC封装技术成功,揭开半导体制程的新世代2019-05-27 3564

-

台积电完成全球首颗3D IC封装技术2019-05-04 3065

-

台积电完成全球首颗 3D IC 封装2019-04-25 5229

-

重磅 | 封装厂集体失业?台积电完成首颗3D封装,领先业界2019-04-24 3258

-

台积电完成全球首颗3D IC封装技术,有望持续独揽苹果大单2019-04-23 3507

全部0条评论

快来发表一下你的评论吧 !