用于不同体态芯片互连的凸点制备及性能表征

描述

共读好书

陈聪 李杰 姜理利 吴璟 张岩 郁元卫 黄旼 朱健

(南京电子器件研究所 微波毫米波单片集成和模块电路重点实验室)

摘要:

随着轻量化、小型化及模块功能多样化的发展,由二维平面到三维高度上的先进封装技术应运而生。微凸点作为实现芯片到圆片异构集成的关键结构,可有效缩短信号传输距离,提升芯片性能。利用电沉积法在 Si基板上以 Cu作支撑层、Ni作阻挡层淀积微米级别的 Au/Sn凸点,所制得的多层凸点直径约 60 μm、高度约 54 μm,其高度可控、尺寸可调,并研究了 Die内凸点高度的一致性,同时对凸点进行了剪切强度和推拉力测试。结果表明,Die内凸点高度均匀性≤2%,剪切力可达 61.72 g以上,与化合物芯片(另一侧为 Au)键合后推拉力可达 7.5 kgf,可实现与化合物芯片的有效集成。

引言

随着异构集成模块功能和特征尺寸的不断增加、芯片尺寸的不断减小,I/O 数量相应大幅增加,对芯片的布线密度提出了更加苛刻的要求。三维异构集成技术的诞生为此提供了解决思路[1⁃3],通过对立体空间的充分利用实现高密度、多材料的芯片堆叠,在降低功耗、提升性能的同时使得电子产品的尺寸和质量得以大幅缩减[4⁃6]。而金属/焊料微凸点之间的互连是实现芯片三维叠层的关键,为了提高芯片三维叠层封装互连的可靠性,制备出具有高互连可靠性的微凸点对微电子封装技术的进一步发展具有重要的作用。

与传统的引线键合相比,凸点结构使得互连长度更短,互连电阻和电感更小,器件的电性能得到了明显提高和改善。与此同时,芯片工作时产生的热可通过凸点直接传到基板上,大幅提高了散热性能。更为重要的是,凸点可呈周边式和面阵式分布,提高了封装密度,缩减了封装体积。以 Au/Sn合金为例,作为半导体后道封装中常用的焊料之一,因其优良的导热和导电性、润湿性、耐腐蚀性和抗蠕变性以及在焊接中无需助焊剂等优点在三维封装技术中得到了广泛应用[7⁃8]。对于 Au/Sn 合金而言,比例控制至关重要,这将决定金属间化合物的组合,从而决定键合的质量,比例的差异将导致膜组成发生变化而脱离共融数值,从而降低键合特性[9] 。

目前,因凸点下金属层(UBM)和凸点沉积工艺的不同,相应的凸点制备工艺存在较大差异。常用的凸点制备技术主要包括:蒸发/溅射沉积法、丝网印刷法、植球法和电沉积法等。随着凸点尺寸及节距的减小,丝网印刷法、植球法等的成本急剧上升,电沉积法成为小尺寸微凸点制备的唯一选择[10] ,具有 工 艺 简 单 、易 于 批 量 生 产 及 凸 点 定 位 精 确 等优点。

本文利用电沉积法在 Si 基板上以 Cu 作支撑层、Ni作阻挡层淀积微米级别的 Au/Sn 凸点,前者用于增加凸点高度,后者用于实现芯片互连。在对其外观形貌进行监测的基础上研究单个电路单元(Die)内凸点高度的一致性,同时对凸点进行相关性能测试,主要包括剪切强度和推拉力测试,以评估该工艺方法下所制备的 Au/Sn凸点的可靠性。

1 实验

1.1 试样制备

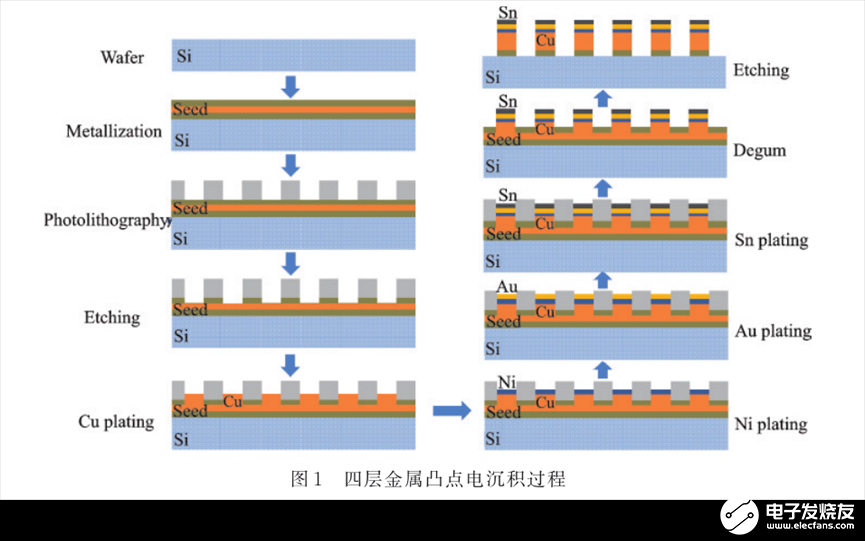

以直流模式自下而上依次进行 Cu⁃Ni⁃Au/Sn四层金属凸点材料的淀积,整体高度控制在 50 μm左右。其中,Cu⁃Ni⁃Sn的电沉积由德国微电镀技术(MOT)公司所生产的电镀系统完成,Au 的淀积由上海新阳晶圆水平电镀系统完成,相应的药水均由对应厂家提供。工艺过程中,在维持添加剂浓度适当的前提下通过调节电流密度、电流值及工艺时间,以改善凸点表面形貌及高度的一致性,进而对相关工艺参数进行固定。需要指出的是,本文所制得的 Au/Sn凸点的高度及厚度比例是经过筛选的,包括 Au/Sn=6 μm/4 μm,6 μm/5 μm,6 μm/6 μm,8 μm/7 μm,10 μm/10 μm 及 5 μm/5 μm 等。最终的验证结果表明,Au/Sn比例接近于 1/1,Sn层高度适当(5~6 μm)时,效果相对较优。具体工艺参数的设定与圆片的占空比及目标高度有关,故此处仅说明相 关的 电流 密度 ,具体 为:Ni ⁃ 2.5ASD、Au ⁃0.3ASD、Sn⁃2ASD(ASD,指电极单位面积所通电的安培数,常以 A/dm2 表示),并根据测试结果进一步确定工艺时间。作为支撑层的 Cu层较高,对于整个凸点高度的一致性起着决定性影响,故需对淀积Cu 的工艺参数进行一定筛选。若不考虑相关前置工艺,四层金属凸点的电沉积过程如图 1所示。

1.2 检测方法

试样工艺完成后去胶、腐蚀、甩干,并进行相关检验,主要包括:利用金相显微镜观测 Au/Sn 凸点表面形貌;采用 P⁃17 台阶仪测量圆片及 Die 内凸点高度,并计算高度一致性;制样后利用扫描电子显微镜(SEM)观测凸点整体形貌及各层金属厚度;利用剪切力测试设备测试其剪切强度;在与化合物芯片键合后(另一侧为 Au)利用拉力测试装置进行推拉力测试,以评估其键合质量。

2 结果与分析

2.1 关键工艺参数筛选

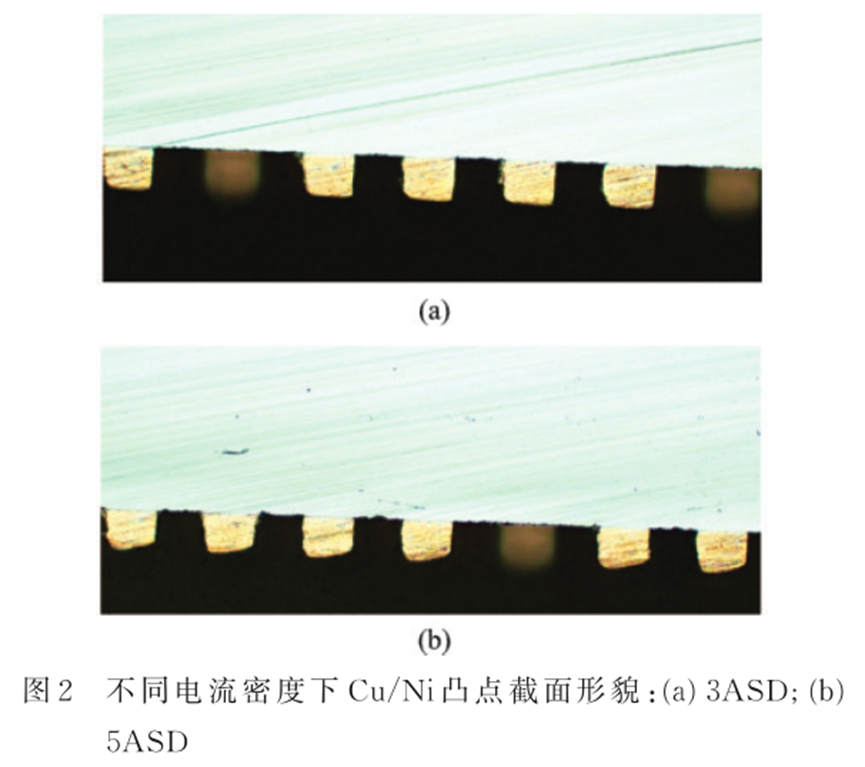

凸点各层金属自下而上分别为 Cu/Ni/Au/Sn,作为支撑层的 Cu层较高,对于整个凸点高度的一致性起着决定性影响。因此,首先对 Cu淀积时的工艺参数进行筛选,此处选取关键工艺参数,即电流密度,以研究不同电流密度下圆片内九点区域处(自上而下、从左到右)Cu/Ni凸点的高度差异,并对圆片内凸点的一致性进行验证,具体结果见表 1。结果 表 明 ,3ASD 下电 沉积 速率 约为 0.6 μm/min,5ASD 电沉积速率约为 1.0 μm/min,这一数值同理论 Cu 电沉积速率相吻合。但因理论占空比与实际值存在差异,故实际高度值与理论值有所偏差。同时,受限于机台,在相同工艺条件下 Cu/Ni凸点的片间重复性较差。可以明确的是,就一致性而言,3ASD下 Cu/Ni凸点的片内均匀性相对较优。

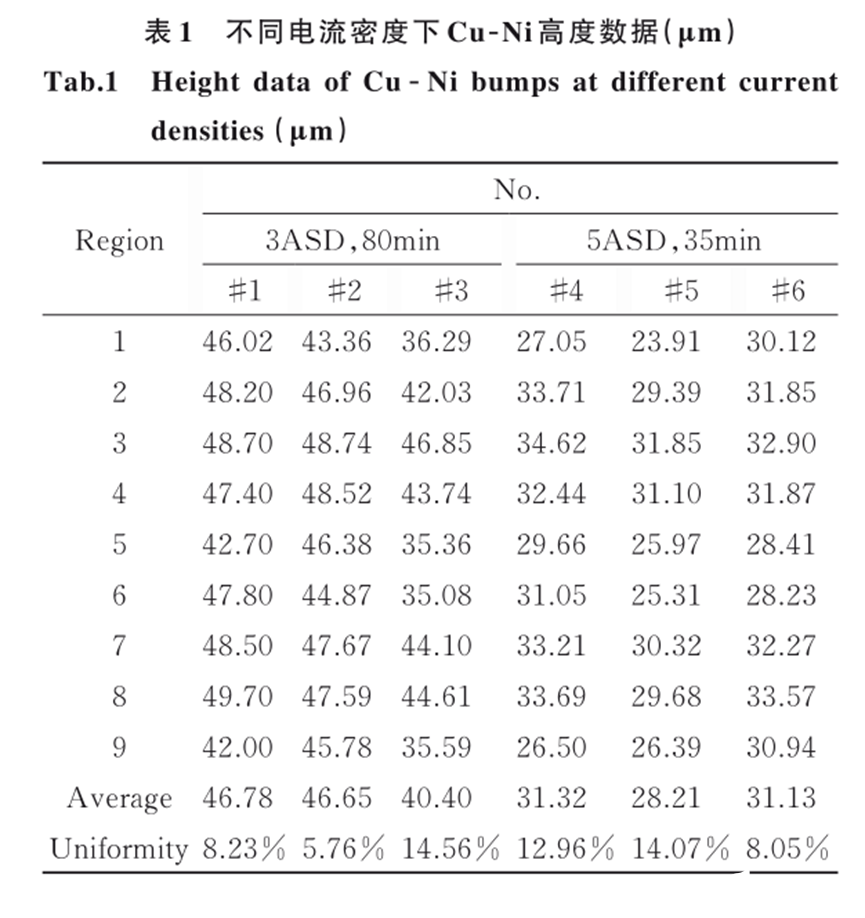

为进一步对比不同电流密度下 Cu/Ni凸点的差异性,分别对 3ASD 和 5ASD 下所制得的微凸点进行划片后观测,结果如图 2 所示。结果表明,3ASD下所制得的凸点较为平整,表面无明显倾斜。这是因为随着电流密度的增加,阴极极化作用随之增强,但当其过高时,镀层表面分布极不均匀平整,各点间生长速率存在差异,进而导致镀层质量下降。因此,综合考虑时间成本和镀层质量,本文选择3ASD作为最佳电流密度。

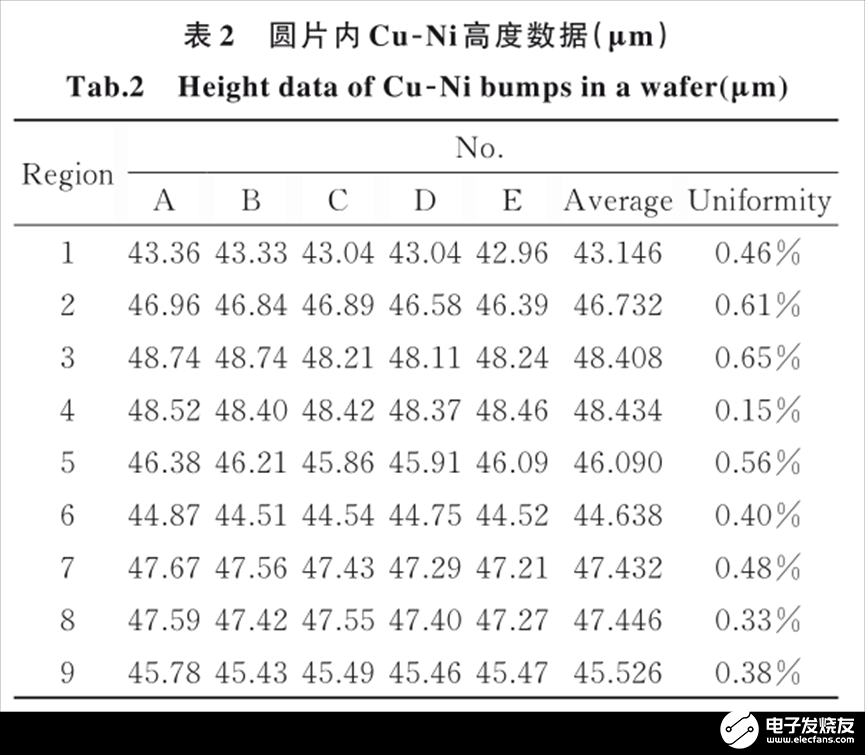

就芯片到圆片的堆叠(D2W)工艺而言,Die 内凸点高度的一致性较片内均匀性而言更为重要,故进一步对 3ASD 下九点区域处 5 连续 Cu/Ni凸点的一致性进行测量,此处选#2片,具体结果见表 2。结果显示,虽然片内均匀性不佳,但各个区域内 Cu/Ni凸点高度波动不大,5连续凸点(A⁃E)高度均匀性最高不超过 0.7%,此处一致性计算方法为:最大偏差/均值/2×100%。

2.2 形貌分析

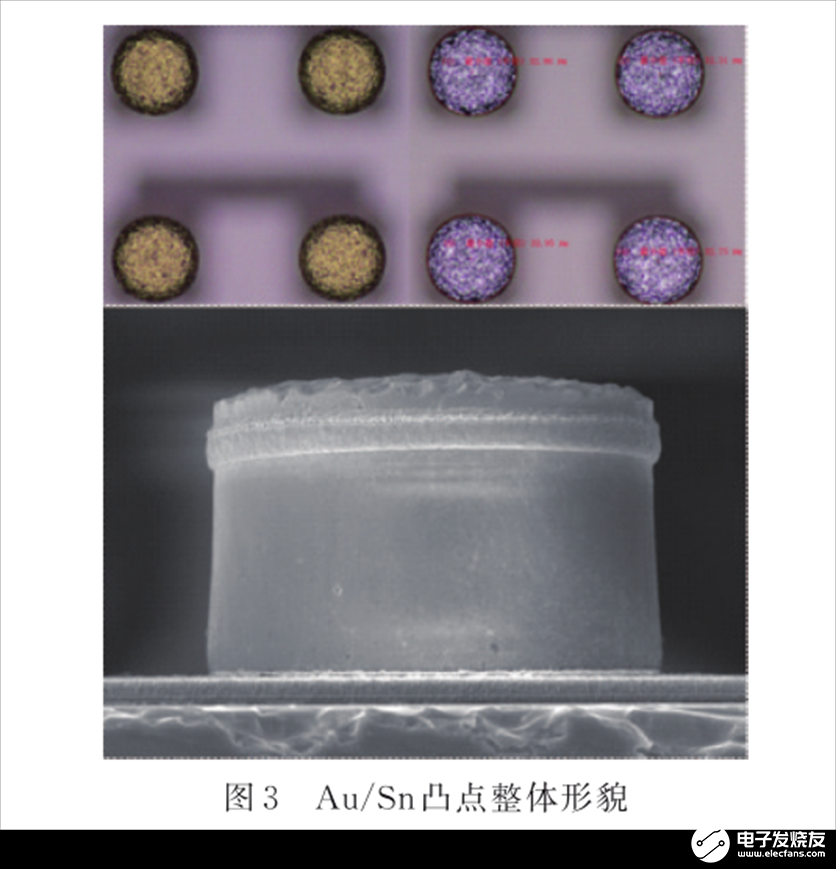

采用直流模式进行电沉积工艺,在 Cu柱顶端进一步沉积一层 Ni进而制备 Au/Sn 凸点,其中,Ni作阻挡层。电沉积工艺所得 Au/Sn 凸点如图 3 所示,其直径约为 65 μm,表面圆滑,尺寸均匀,可见分层明显。需要注意的是,Au 电镀液含氰,所用光刻胶存在不耐受的问题,故在电沉积 Au 时存在细微的外扩现象,因此,在工艺开发时需考虑外扩量,以保证 Au/Sn层厚度均满足要求。

2.3 高度均匀性分析

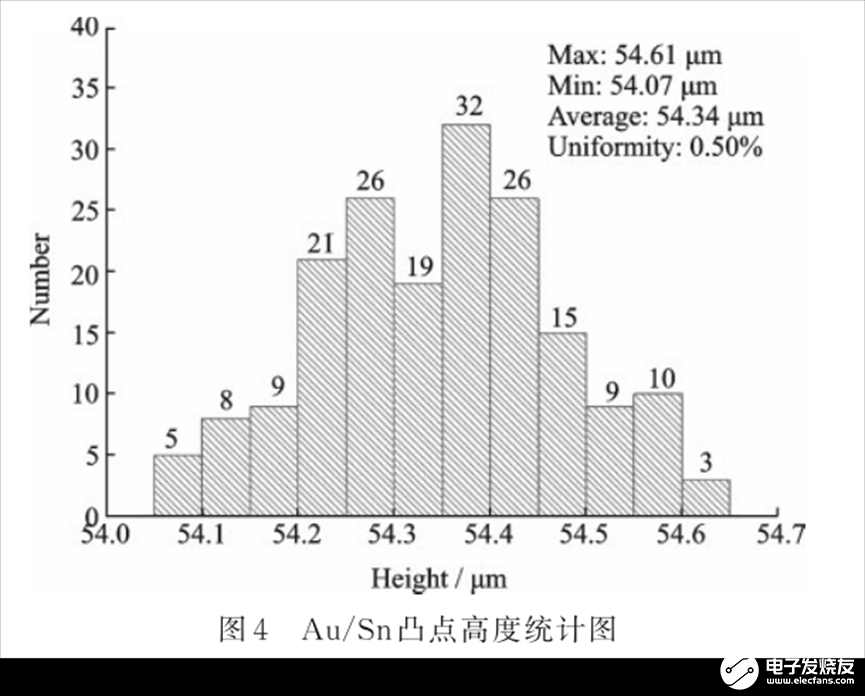

上述对最佳电流密度进行筛选时,但尚未对淀积 Au/Sn后整个凸点的一致性进行验证,故在圆片内随机抽取 1 个 Die,其中共包括 183 个凸点,利用台阶仪测量所有 Au/Sn 凸点的高度,结果见图 4。测量结果显示,在抽取的单个 Die内,Au/Sn凸点高度分布于 54.07~54.61 μm 之间,最大偏差不超过0.54 μm,高度均值为 54.34 μm,一致性高达 0.5%。

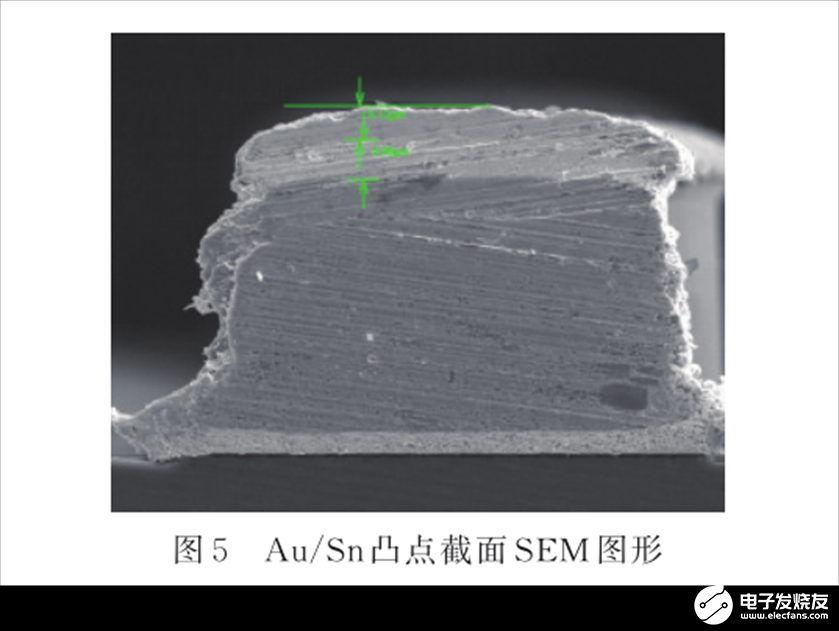

凸点整体高度关系着能否键合完全,而 Au/Sn凸点比例控制则决定着键合质量。为更精确地获取 Au/Sn 各层高度,划片后对其进行截面分析,得到如图 5所示的 Au/Sn凸点剖面图形。图中,Cu层与 Au层之间存在清晰的界面,而 Ni层与 Cu层之间的界面并不清晰。一方面,Ni层相对较薄;另一方面,制样过程中的切削在一定程度上对 Ni层有所掩盖。同样,由于自扩散作用的存在,Au相与 Sn相之间的界面相对模糊,若忽略测量误差,Au相与 Sn相的厚度比例约为 5.95 μm/5.13 μm,接近于 1/1。

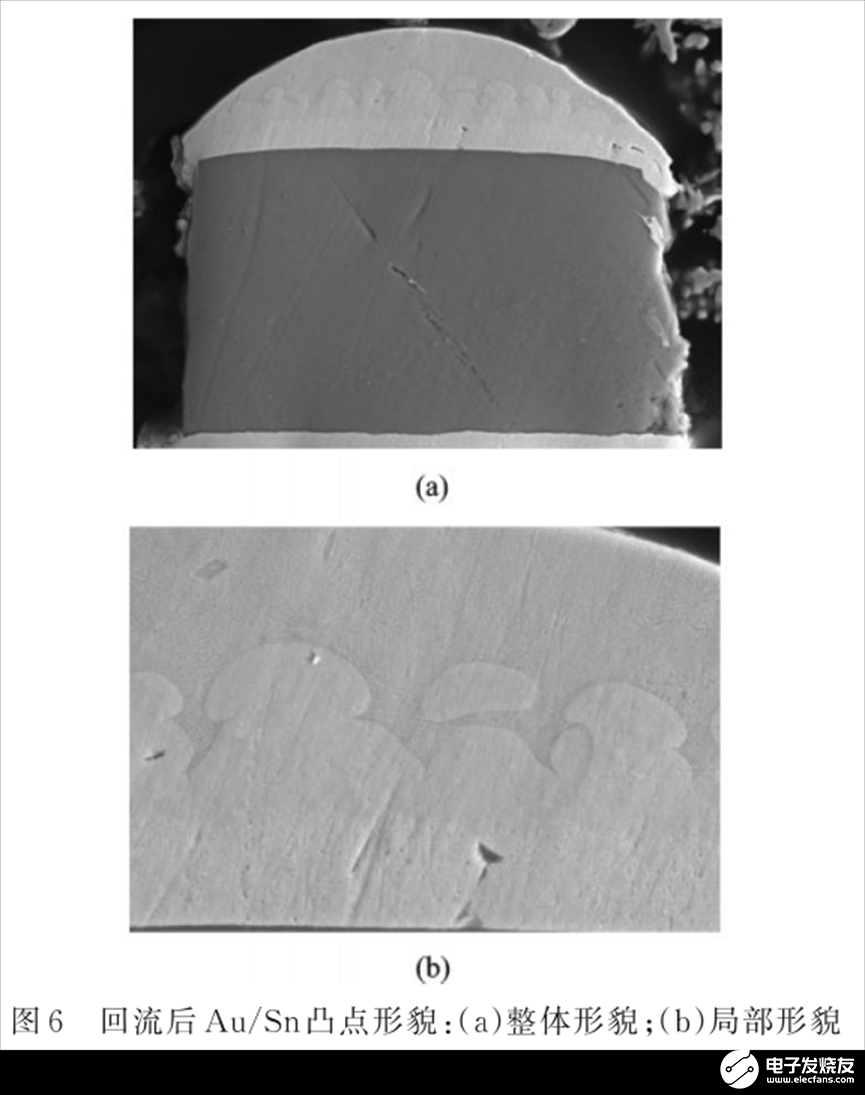

为更好地分析此工艺条件下 Au/Sn 凸点的比例 是 否 合 适 ,对 样 品 进 行 了 回 流 ,回 流 条 件 为280℃,回流后得到的 Au/Sn 凸点形貌如图 6 所示。由图可见,回流后 Au/Sn 凸点呈“蘑菇状”,表面圆滑,形成了明显的 Au/Sn 共晶组织。同时,表层金属 Sn 在回流后未沿凸点边缘外溢,表明 Sn 含量相对合适。

2.4 剪切力测试

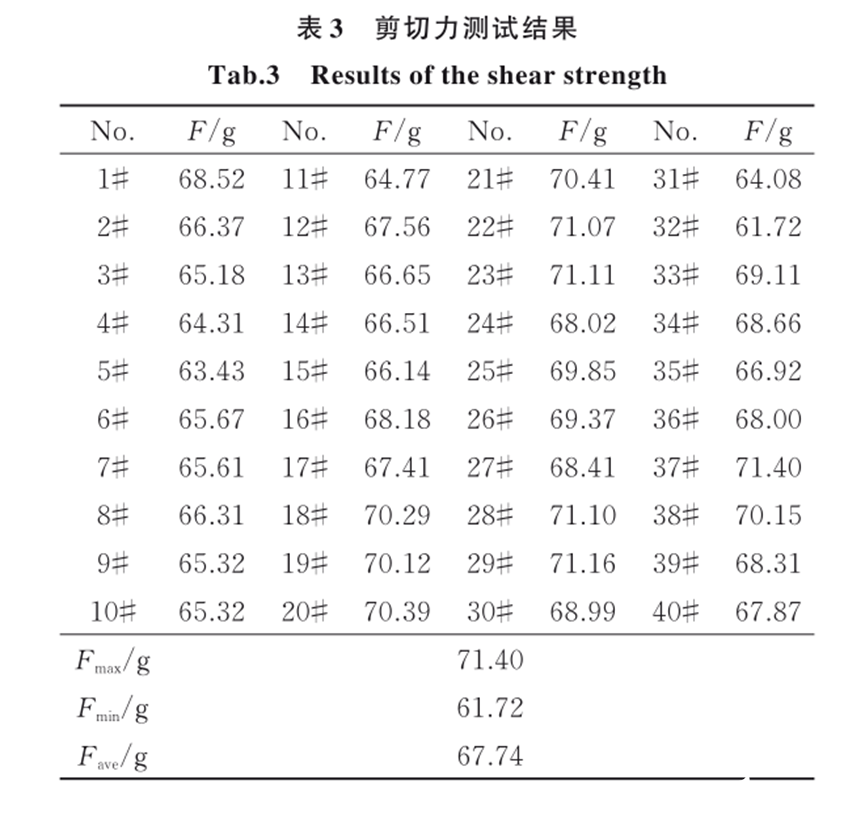

对于微凸点工艺可靠性而言,剪切强度是衡量封装质量的一个重要指标。为评判圆片内凸点的整体剪切强度,随机抽取 40只芯片,利用剪切测试仪对单个凸点的剪切力进行检验,剪切位置大致位于凸点自下而上 1/4处。实验依据标准条款为检验标准GJB548B,测试数据如表 3所示。测试结果表明,单个凸点剪切力的平均值为67.74 g,最大值为71.40 g,最小值为 61.72 g,整体数值相差不大。由此可见,底层金属 Cu 镀层质量相对良好,个体差异较小,这一点同电沉积Cu后的表观形貌观测结果相吻合。

2.5 键合界面分析

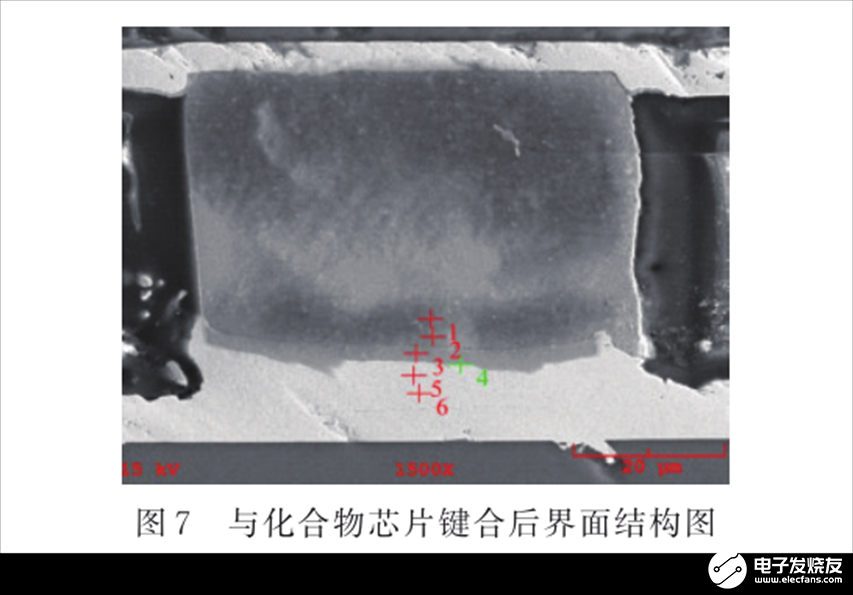

共晶键合的质量和可靠性很大程度上依赖界面金属化合物(IMC)的组成及微结构。因此,将加工有 Au/Sn凸点的 Si基芯片与化合物芯片(另一侧为 Au)进行键合,并对键合界面进行分析,键合界面如图 7 所示。由图可见,键合后可见明显的 Cu⁃Ni分层及 Ni⁃Au/Sn 化合物分层,前者是因为电沉积Cu后未及时进行 Ni层的淀积,导致 Cu层表面存在氧化。同时,不存在表层金属 Sn沿凸点边缘大量外溢的现象,表明 Sn 含量相对合适,但因制样问题界面较为粗糙,未见明显的 Au/Sn共晶组织。

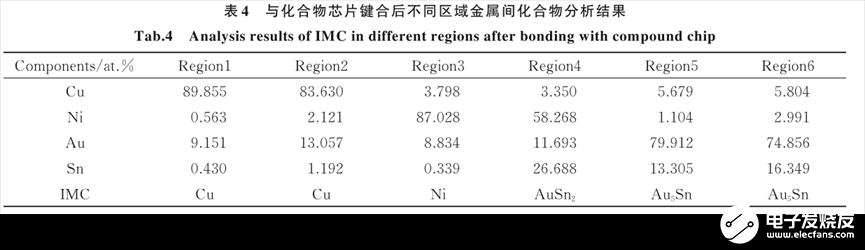

为更好地确定键合后界面金属的组成,采用SEM 对选定的 7 个区域的界面金属进行了成分分析,通过光谱确定界面共晶体的化学成分,从而判断化合物组成构成形式,数据结果见表 4。由表可知,区域 1、2均为电沉积所制备的 Cu层;区域 3为电沉积所制备的 Ni层;区域 4为 Ni与 Au/Sn化合物界面,若仅考虑 Au/Sn 共晶相,因扩散作用形成了ε相[6](AuSn 2 ),该相具有较大的脆性;区域 5、6 皆形成了ξ相(Au 5 Sn),厚度相对较厚,可有效保证键合强度。Au/Sn相图表明,富 Sn的 η(AuSn 4 )首先形成于217℃,ε相(AuSn 2 )形成于 252℃,δ相(AuSn)形成于281℃,而在278℃时,共晶组织随着δ和ξ的液相反应开始转变,随着温度的进一步升高,ξ相将继续生长,且晶相生长机制不再发生变化。因 Ni的导热性弱于Au,故在靠近 Ni层的区域 4 多形成 ε相。需要注意的是,区域 4处 γ相 AuSn 2 若与 Ni反应生成(Au,Ni,Sn)这一复杂的三相金属间化合物,其焊接效果将大大降低,这一点仍需后续进行实验论证。

2.6 推拉力测试

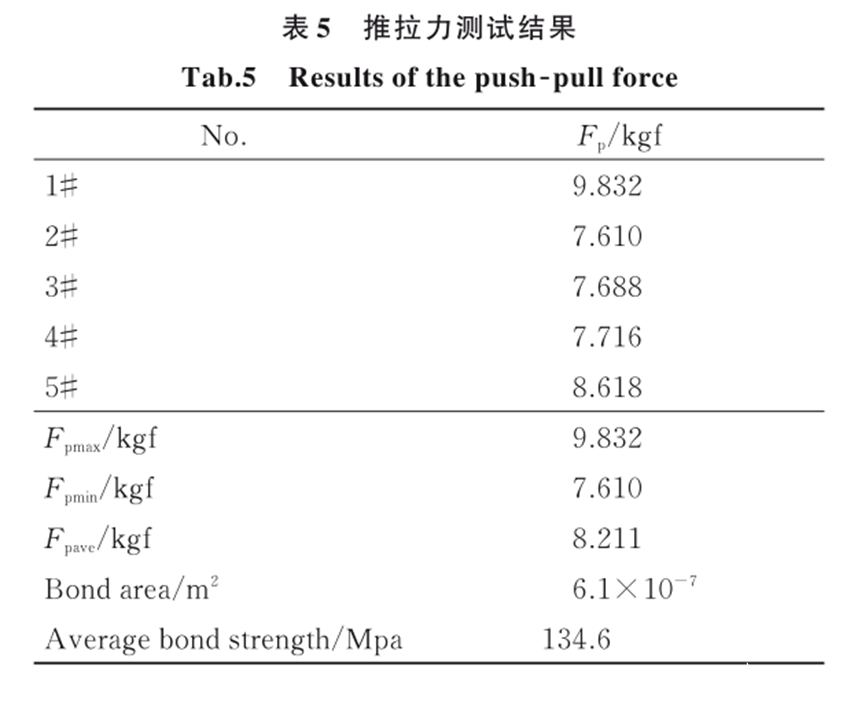

为更直观地反映键合质量,加工有 Au/Sn凸点的 Si基芯片在热回流后将其与化合物芯片(另一侧为 Au)进行键合,并对键合后的整个芯片进行推拉力测试,此处键合方式为 D2W,具体推拉力测试结果见表 5。结果显示,键合后的整个芯片推拉力均值为 8.211 kgf,最小值为 7.610 kgf,均在 7.5 kgf 以上,满足>5.0 kgf的使用要求。同时进一步检验其键合质量,Au/Sn单个凸点的直径约为 65 μm,化合物芯片与之对应的键合区域为边长约 80 μm 的正方形,故单个键合区域面积为 3.318×103 μm 2 ,整个 Die内共 183 个凸点,整个键合区域面积为 6.10×10-7m2 ,平均键合强度为 134.6 Mpa。

3 结论

利用电沉积法在 Si 基板上以 Cu 作支撑层、Ni作阻挡层淀积微米级别的 Au/Sn凸点,制得的多层金属凸点直径约 60 μm、高度约 54 μm,其高度可控、尺寸可调,Die 内凸点高度一致性≤2%,有效改善了高尺寸下金属凸点的均匀性,使得与异质芯片D2W 互连的可靠性提高。同时,通过前期对 Au/Sn比例的筛选,确定 Au/Sn 实际比例接近于 1/1 时效果相对较优,经回流后可形成表面圆滑的“蘑菇状”凸点,共晶组织明显,与化合物芯片键合后发现界面多为 Au 5 Sn 相。此外,剪切力和推拉力测试结果表明,最小剪切力为 61.72 g,整体数值相差不大,键合后推拉力达 7.5 kgf及以上,为实现不同体态芯片的异质异构集成打下了良好的基础。

审核编辑 黄宇

-

倒装芯片的特点和工艺流程2020-07-06 14387

-

纳米铁氧体的制备与表征方法研究2010-10-02 963

-

先进3D芯片堆叠的精细节距微凸点互连2012-05-04 4322

-

倒装芯片凸点制作方法2021-04-08 2293

-

BGA芯片封装凸点工艺:技术详解与未来趋势2024-11-28 4040

-

芯片互连技术深度解析:焊球、铜柱与微凸点的奥秘2025-02-20 4180

-

聊聊倒装芯片凸点(Bump)制作的发展史2025-08-12 7448

-

用于3D集成的精细节距Cu/Sn微凸点倒装芯片互连工艺研究2026-04-09 1875

全部0条评论

快来发表一下你的评论吧 !