PCB设计如何减少接地反弹?

PCB设计

描述

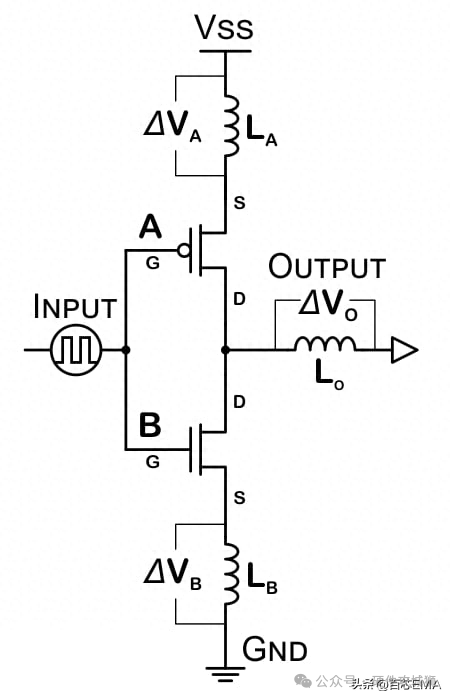

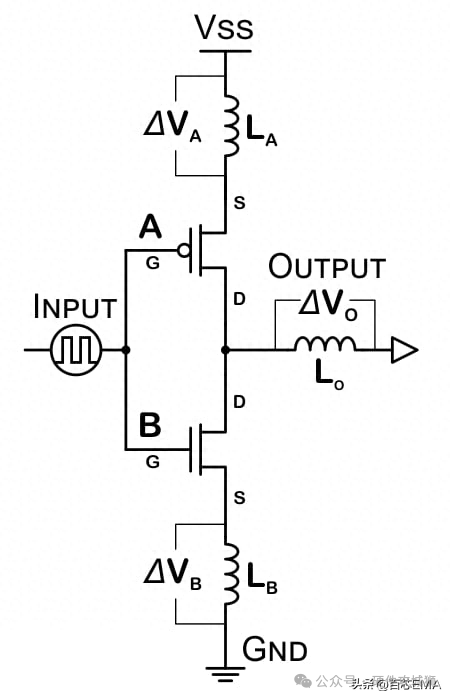

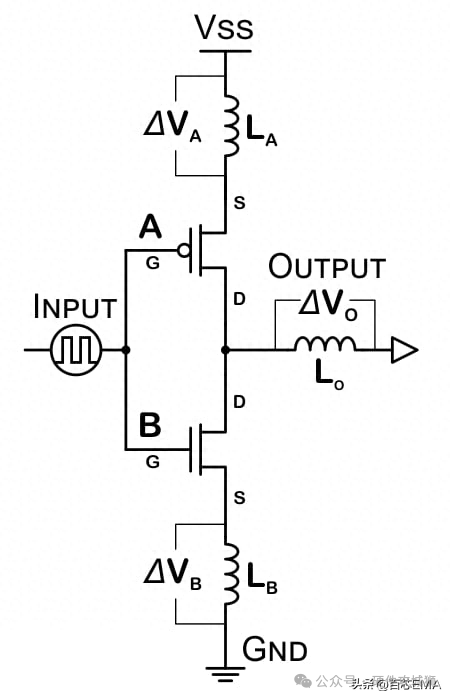

一、什么是接地反弹 地弹是一种噪声,当 PCB 接地和芯片封装接地处于不同电压时,晶体管开关器件会出现这种噪声。 为了更好地理解接地反弹,可以看下面的推挽电路,该电路可以提供逻辑低或者逻辑高输出。

推挽电路

该电路由 2 个 MOS 管组成:上方的 P 沟道 MOS管的源极连接到 Vss,漏极连接到输出引脚。下部 N 沟道 MOS 的漏极连接到输出引脚,源极接地。 这 2 种 MOS管类型对 MOS 管栅极电压具有相反的响应。MOS管的栅极处的输入逻辑低信号将导致P沟道MOS管将Vss连接到输出,并导致N沟道MOS管将输出与GND断开。 MOS管栅极处的输入逻辑高信号将导致P沟道MOS管将其Vss与输出断开,并导致N沟道MOS管将输出连接到GND。 将 IC 芯片上的焊盘连接到 IC 封装的引脚上是微小的键合线,这些必需品具有少量电感,由上面的简化电路建模。电路中当然也存在一定量的电阻和电容,这些电阻和电容没有建模,也不一定需要理解。

推挽电路 全桥开关的等效电路中显示了3个电感,电感符号代表封装电感(IC封装设计固有的电感),电路输出连接到一些元件。 想象一下输入在很长一段时间后保持在逻辑电平后遇到这个电路。这种状态会导致上部晶体管通过上部MOS管将电路的输出连接到Vss。经过适当长的时间后,LO和LA将存在稳定的磁场,并且ΔV O、ΔV A和ΔV B的电势差为0伏,迹线中将存储少量电荷。 一旦输入逻辑切换到低电平,上部 MOS管 就会断开 Vss 与输出的连接,下部栅极将触发下部 MOS管将电路的输出连接到 GND。 此时输入逻辑发生变化,结果在整个系统中移动。

二、接地反弹的原因

输出和接地之间的电位差异电流从输出通过下部MOS向下移动到接地。电感利用存储磁场中的能量在 ΔV O和 ΔV B之间建立电势差,试图抵抗磁场的变化。

即使是电气连接,输出和接地之间的电位差也不会立即处于0V。记住,输出之间处于Vss,而MOS管 B 的源极之间处于0V电位。当输出线放电时,先前的电位差将导致电流流动。

在电流开始从输出流向接地的同时,封装的电感特性在 ΔV B和 ΔV O之间产生电势差,以尝试维持先前建立的磁场。

电感 LB和 LO 改变 MOS管 源极和漏极电势。这是一个问题,因为 MOS管 栅极电压以芯片封装上的地为参考。当电路在栅极触发阈值附近振荡时,输入电压可能不再足以保持栅极打开或导致其多次打开。

当电路再次切换时,一组类似的情况将导致在 ΔVA 上建立电势,从而将 MOSFET A 的源极电压降低到触发阈值以下。

三、为什么接地反弹不好?

当输入改变状态时,输出和MOS管不再处于定义的状态,介于两者之间。结果可能是错误或双重切换。此外,IC芯片上共享相同 GND 和Vss连接的任何其他部门都将受到开关时间的影响。 但接地反弹的影响不仅限于IC芯片。正如ΔVB 迫使 MOS管 源极电势高于 0V 一样,它也迫使电路 GND 电势低于 0V。你看到的很多描述接地反弹的图像都显示了外部影响。

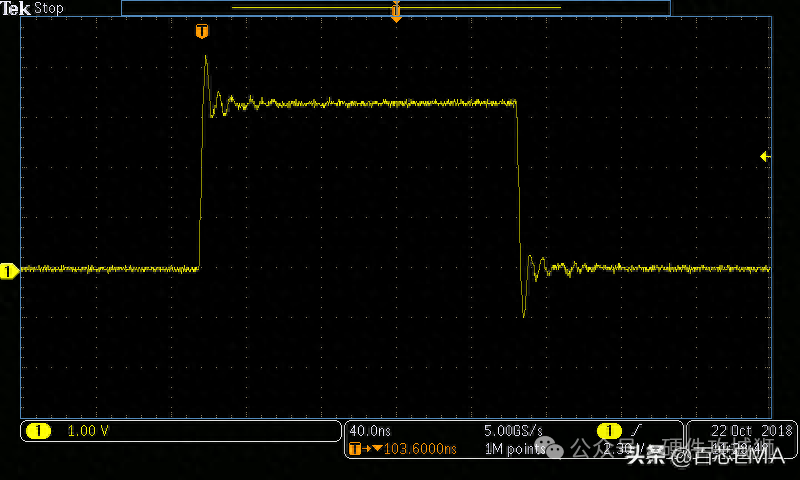

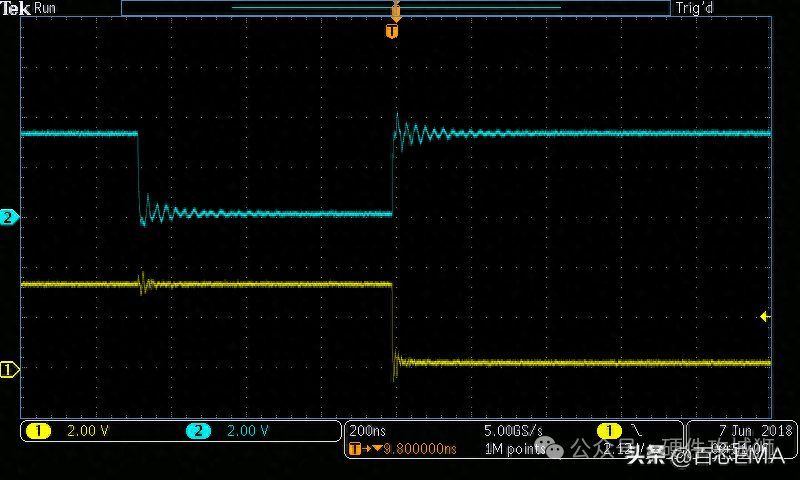

如果同时切换多个门,则效果会更加复杂,并可能完全破环电路。你可以在下面的示例中看到反弹。下图显示了连接并激活了显著GND和Vss反弹。 这里,开关期间在3.3V线路上产生约1V的噪声,该噪声在最终落入背景线路噪声之间继续在信号线路中明显谐振。

噪声不仅限于正在开关的门。开关门连接到IC电源引脚,而PCB通常共享公共电源和接地轨。意味着噪声可以通过芯片上的 Vss 和接地的直接电气连接到 PCB上走线的耦合轻松传递到电路中的其他位置。

在上图中,通道2(青色)显示无阻尼信号线中的接地和Vss反弹,该问题非常严重,以至于会传送到通道1上的另一条信号线(黄色线)

四、减少接地反弹的方法

1、使用去耦电容1来定位接地反弹

减少地弹的首选解决方案是在每个电源轨和地之间安装SMD去耦电容,并尽可能靠近IC。远处的去耦电容具有很长的走线,会增加电感,因此安装在远离IC的地方对自己没有任何好处。当IC芯片上的晶体管切换状态时,会改变芯片上晶体管和本地电源轨的电位。

去耦电容为IC提供临时、低阻抗、稳定的电位并限制反弹效应,防止其扩散到电路的其余部分。通过电容靠近IC,可以最大限度地减少PCB走线中的电感环路面积并减少干扰。

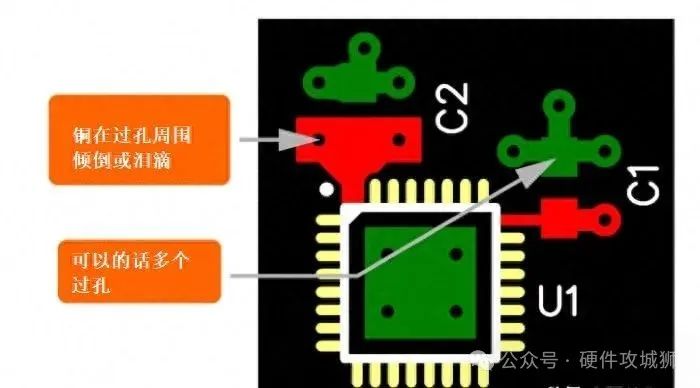

混合信号IC通常具有独立的模拟和数字电源引脚,你可以在每个电源输入引脚上安装去耦电容。电容应该位于IC和连接到PCB上相关电源层的多个过孔之间。

去耦电容应通过过孔连接到电源层 多个过孔是首选,但是由于PCB尺寸要求,通常是不可能的。可以的话,使用铜浇注或者泪滴来连接过孔,如果钻头稍微偏离中心,额外的铜有助于将过孔连接到走线。

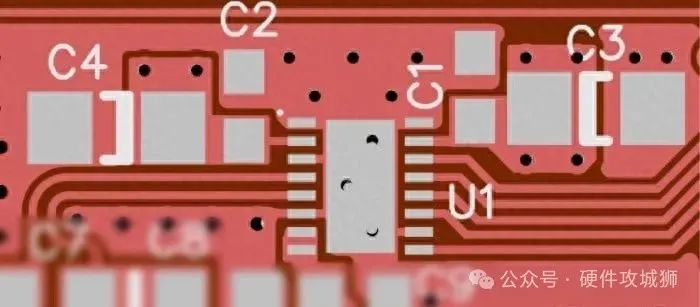

IC (U1) 和四个电容(C1、C2、C3、C4)的铜焊盘

C1 和C2 是用于高频干扰的去耦电容。根据数据表建议将 C3 和 C4 添加到电路中。由于其他平面的限制,过孔放置并不理想。

有时候,在物理上不可能将去耦电容放置在靠近IC的位置。但是,如果将其放置在远离IC的地方,则会产生电感环路,从而导致接地反弹问题更严重。

如果这样的话,可以将去耦电容放置在IC下方PCB的另一侧。实在不行,你可以使用相邻层上的铜在板内制造自己的电容,这样的电容被叫做嵌入式平面电容。由于PCB中由非常小的介电层隔开的平行铜浇注组成。这种类型电容的额外好处之一是唯一的成本是时间。

2、使用电阻限制电流

使用串联限流电流电阻来防止过量电流流入和流出IC。这不仅有助于降低功耗并防止设备过热,而且还能限制从输出线通过MOS管流向Vss和GND的电流,从而减少接地反弹。

3、使用布线来降低电感

如果可以的话,将返回路径保留在相邻走线和相邻层上,由于存在厚芯材料,电路板上第1层和第3层之间的距离通常是第1层和第2层之间距离的几倍。信号和返回路径之间任何不必要的分离都会增加该信号线的电感以及随后的地弹效应。

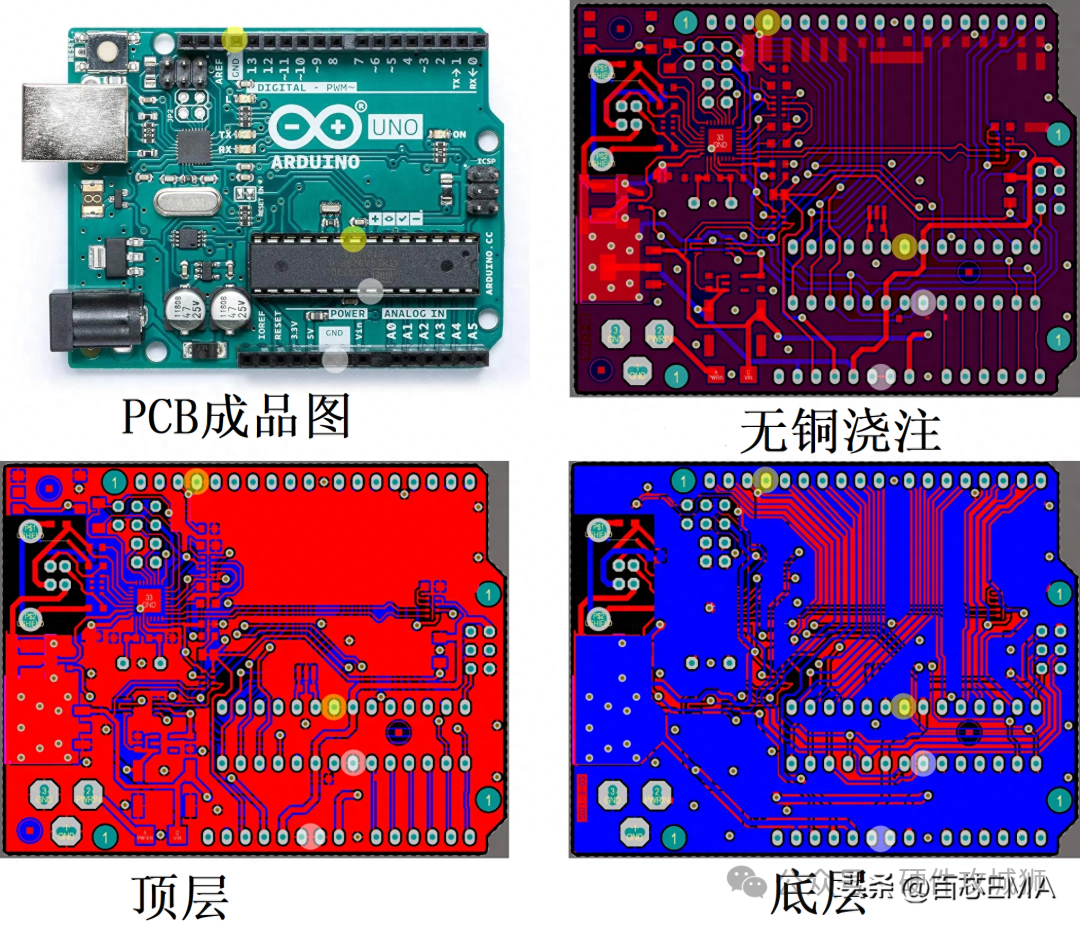

你可以看下图的PCB布局。

模拟和数字接地分别以白色和黄色突出显示

该板具有单独的模拟和数字接地返回引脚,PCB的布局抵消了将他们分开的影响,IC的数字接地引脚与接头排上的接地引脚之间没有清晰且直接的路径。

信号将通过IC的迂回路径到达接头引脚,并通过接地引脚返回迂回路径。

4、通过编程和设计考虑减少接地弹跳

随着开关数量的增加,地弹干扰也会增加,如果可以的话,用短延迟偏移开关门。

例如:你的设计可能以不同的时间间隔(1 秒、2 秒、3 秒等)闪烁各种LED,以指示设计的状态。当所有3个LED同时切换时,地弹效应对电路的影响最大。

在这个例子中,你可以通过稍微偏移LED来减轻地弹的影响,使它们不完全同步。在LED之间引入1毫秒的便宜对于用户来说时感觉不到的,但会将地面反弹效应降低约3倍。

5、其他PCB布局设计原则

在设计允许的情况下,尽可能使用焊盘内通孔。

减少信号返回路径距离。距离的缩短将减少寄生电容。为了实现这一点,最好将组件放置在其接地点的正上方

勿使用插座或绕线板

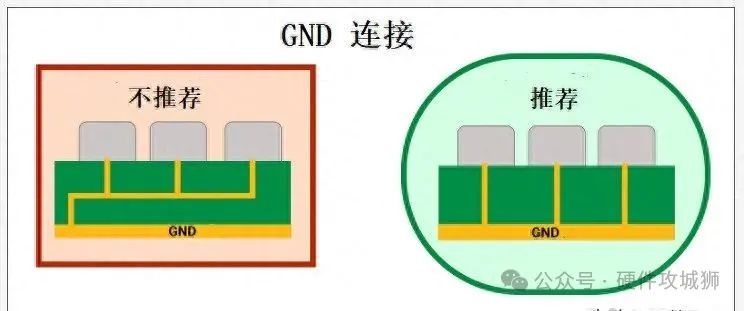

勿共用接地过孔或走线进行接地连接。建议使用单独的过孔和走线连接到接地层。

勿将电容直接连接到输出。 实施低压差分信号(LVDS) 作为 /0 标准,该标准提供高带宽和高抗噪性. 选择短引线封装以减少串联电感,还建议使用BGA。 使用坚固的接地层来减少 IR 损耗和电感,避免地面分割平面 如果设计允许,请尝试使用较低的开关元件

审核编辑:黄飞

-

pcb设计如何减少接地反弹问题?2023-09-21 969

-

接地问题分析(PCB设计)2012-08-05 3889

-

PCB设计如何绕等长?2021-03-06 1624

-

PCB设计考虑EMC的接地技巧2009-11-17 1597

-

pcb设计考虑emc的接地技巧2016-03-29 898

-

高频电路PCB设计中的接地问题2016-07-26 887

-

全面解析:PCB设计接地问题精要2016-12-15 1043

-

【大牛笔记】PCB设计接地攻略2017-11-27 1271

-

pcb设计当中emc的接地该怎样设计2019-10-25 4401

-

减少接地反弹的方法概述2019-09-15 6588

-

PCB设计如何做好接地设计2021-05-01 5888

-

PCB设计师关注要点 如何减少接地噪声2022-05-07 6457

-

PCB设计中如何减少ESD损害2023-07-11 2064

-

多层pcb设计如何过孔的原理2024-04-15 2543

-

PCB设计中单点接地与多点接地的区别与设计要点2025-10-10 2780

全部0条评论

快来发表一下你的评论吧 !