FPGA开源项目:Verilog常用可综合IP模块库

可编程逻辑

描述

Verilog常用可综合IP模块库

优秀的 Verilog/FPGA开源项目介绍(十九)- Verilog常用可综合IP模块库

想拥有自己的Verilog IP库吗?设计时一个快捷键就能集成到自己的设计,酷炫的设计你也可以拥有!

每个公司应该都会维护属于自己公司风格的IP库,作为个人学习或者持续使用的方式,这种方法很有用。今天肯定不是分享我司的IP库,而是一个开源库,每个人都可以使用、维护或者修改,当然作为学习(多人维护)也是不可多得的资料。把该库集成到自己常用的文本编辑器(SublimeVScodeVim等等)可以很快完成代码设计。

简介

这是verilog/systemverilog 可综合模块的集合。

所有代码在典型的 FPGA 和主流 FPGA 供应商中都具有高度可重用性。

可以出于任何目的对文件进行重新混合、转换和构建,甚至是商业用途。

但是必须提供创作者的姓名并与原始作品相同的许可。

工程链接

❝

https://github.com/pConst/basic_verilog

详细介绍

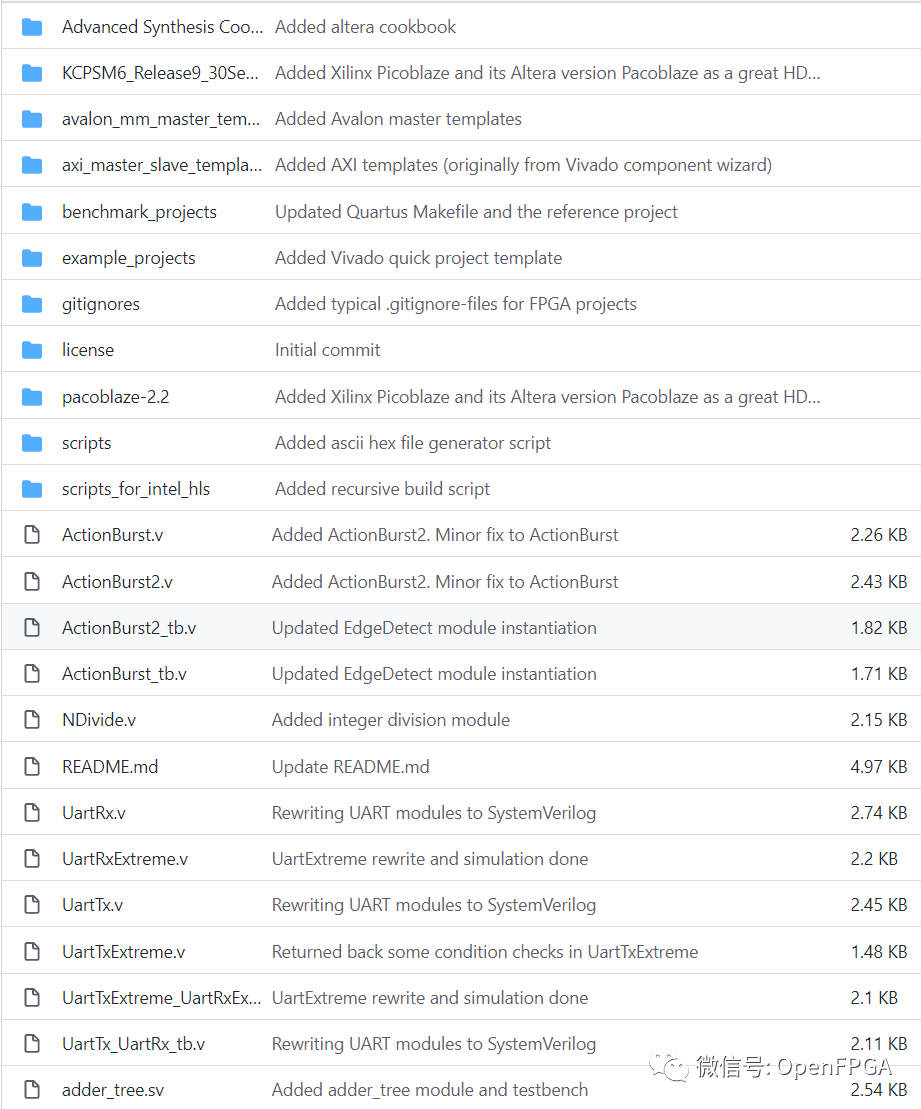

文件夹外的文件根据文件名很容易判断其用途,下面着重介绍文件夹内部文件:

| 目录 | 描述 |

|---|---|

| Advanced Synthesis Cookbook/ | Altera cookbook中的有用代码 |

| KCPSM6_Release9_30Sept14/ | Xilinx 的 Picoblaze 软处理器 |

| pacoblaze-2.2/ | 适用于 Altera 器件的 Picoblaze 版本 |

| example_projects/ | FPGA 项目示例 |

| benchmark_projects/ | 多种 FPGA 类型的编译时间基准 |

| scripts/ | 有用的 TCL 脚本 |

注1:cookbook:类似技巧大全的意思

这里还有一个TCL脚本文件,再简单介绍一下:

| 脚本 | 描述 |

|---|---|

| scripts/allow_undefined_ports.tcl | 允许为 Vivado IDE 生成带有未定义引脚的测试项目 |

| scripts/compile_quartus.tcl | Quartus IDE 中用于命令行项目编译的样板脚本 |

| scripts/convert_sof_to_jam.bat | Altera/Intel FPGA 配置文件转换器 |

| scripts/convert_sof_to_rbf.bat | 另一个 Altera/Intel FPGA 配置文件转换器 |

| scripts/iverilog_compile.tcl | 使用 iverilog 工具编译 Verilog 源代码并在 gtkwave 工具中运行模拟的完整脚本 |

| scripts/modelsim_compile.tclModelsim | 无项目模式编译脚本 |

| scripts/post_flow_quartus.tcl | 英特尔 Quartus IDE 的自定义报告或报告分析 |

| scripts/post_flow_vivado.tcl | Xilinx Vivado IDE 的自定义报告或报告分析 |

| scripts/program_all.bat | Altera/Intel FPGA 的命令行编程器示例 |

| scripts/project_version_auto_increment.tcl | Quartus IDE 的项目版本自动增量脚本 |

| scripts/quartus_system_console_init.tcl | 通过 JTAG-to-Avalon-MM 桥 IP 读/写 Avalon-MM 的初始化脚本 |

| scripts/set_project_directory.tcl | 更改当前目录以匹配 Vivado IDE 中的项目目录 |

| scripts/write_avalon_mm_from_file.tcl | 通过 JTAG-to-Avalon-MM 桥 IP 将二进制文件中的批量二进制数据写入 Avalon-MM |

注2:Avalon:ALTERA公司FPGA内部使用的总线,下图是典型Altera FPGA系统

其他模块说明

| 脚本 | 描述 |

|---|---|

| ActionBurst.v | 多通道一次性触发模块 |

| ActionBurst2.v | 可变步长的多通道一次性触发 |

| adder_tree.sv | 将多个值并行相加 |

| bin2gray.sv | 格雷码到二进制转换器 |

| bin2pos.sv | 将二进制编码值转换为one-hot代码 |

| clk_divider.sv | 宽参考时钟分频器 |

| debounce.v | 输入按钮的两周期去抖动 |

| delay.sv | 用于产生静态延迟或跨时钟域同步的有用模块 |

| dynamic_delay.sv | 任意输入信号的动态延迟 |

| edge_detect.sv | 组合边沿检测器,在每个信号边沿上提供一个滴答脉冲 |

| lifo.sv | 单时钟 LIFO 缓冲器(堆栈)实现 |

| NDivide.v | 原始整数除法器 |

| prbs_gen_chk.sv | PRBS 模式生成器或检查器 |

| pulse_gen.sv | 产生具有给定宽度和延迟的脉冲 |

| spi_master.sv | 通用spi主模块 |

| UartRx.v | 简单明了的 UART 接收器 |

| UARTTX.v | 简单明了的 UART 发送器 |

| uart_rx_shifter.sv | 类似 UART 的接收器移位器,用于 FPGA 内部或 FPGA 之间的简单同步消息传递 |

| uart_rx_shifter.sv | 类似 UART 的接收器移位器,用于 FPGA 内部或 FPGA 之间的简单同步消息传递 |

| UartRxExtreme.v | 极小的 UART 接收器实现 |

| UartTxExtreme.v | 极小的 UART 发送器实现 |

| ... | ... |

总结

今天只介绍了一个项目,这个项目可以给大家提供一个思路尤其对于没有工作或者刚入门不久的同行,自己在编写代码时要想着可继承性,这样在以后做类似项目时可以借用,并且长期维护一个代码对于这个模块的理解有很大帮助。

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

审核编辑:黄飞

-

FPGA优质开源模块-SRIO IP核的使用2023-12-12 4010

-

verilog HDL 可综合模型的结构2012-10-20 2758

-

Verilog可综合子集2013-04-01 2449

-

信盈达FPGA综合班2018-09-19 1873

-

Verilog HDL综合实用教程2009-07-20 823

-

可综合的Verilog语法和语义2012-05-21 537

-

如何设计常用模块的Verilog HDL?2018-10-16 1181

-

如何设计可综合的Verilog代码和应该遵循什么原则2019-04-20 5339

-

如何在Verilog设计中使用库模块2021-01-22 1092

-

如何使用Verilog HDL描述可综合电路?2021-04-04 5168

-

优秀的 Verilog/FPGA开源项目介绍(一)2021-10-11 11464

-

Verilog/FPGA开源项目介绍2021-11-17 4091

-

优秀的IC/FPGA开源项目:伪红外图像处理2023-06-09 3915

-

fpga ip核是什么 常用fpga芯片的型号2023-07-03 9912

-

使用IP核和开源库减少FPGA设计周期2025-01-15 1511

全部0条评论

快来发表一下你的评论吧 !