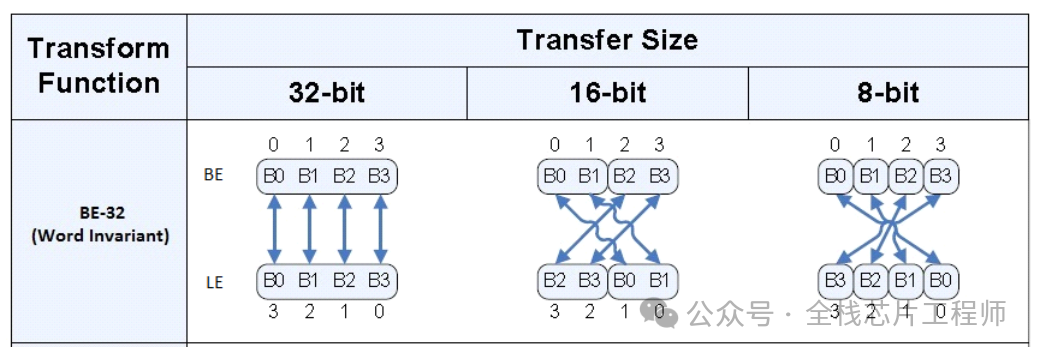

字传输不变的3种大小端处理方式

描述

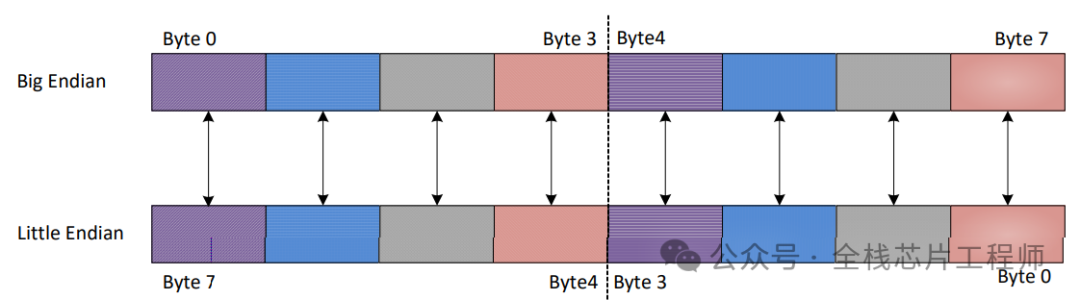

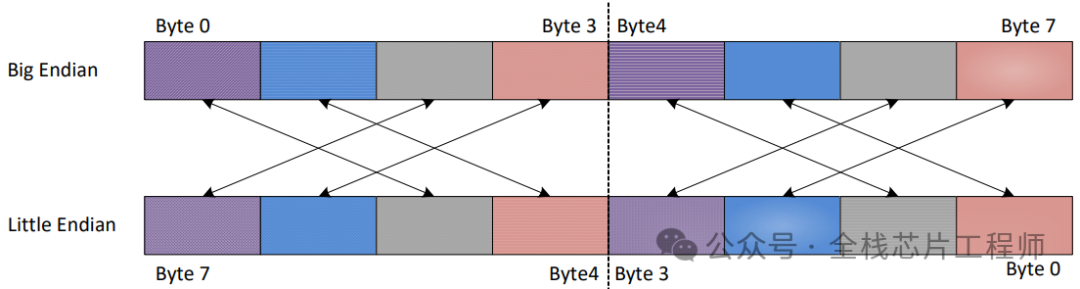

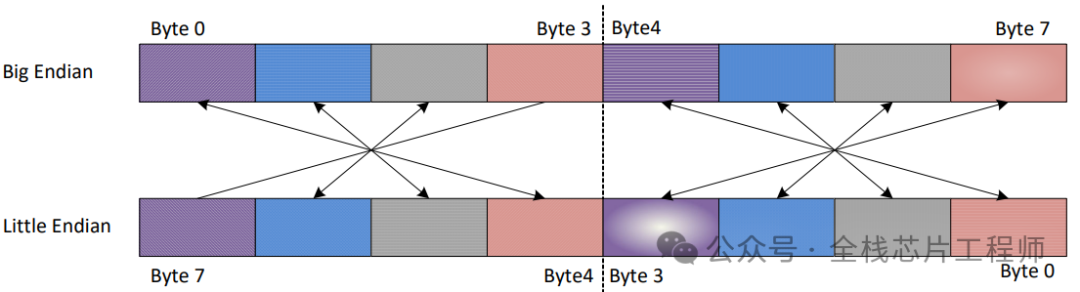

大端,最高字节存储在最低的内存地址,小端则是最低有效字节存储在最低的内存地址。在Verilog中实现大端(Big-Endian)和小端(Little-Endian)之间的转换通常涉及到对多字节数据的操作。

按照word传输不变的要求,一般我们可以分为三种:

第一种:word传输不变,Word access的处理。

第二种:word传输不变,half Word access的处理。

第三种:word传输不变,Byte access的处理。

以下是一个简单的Verilog代码示例,展示了如何在大端和小端之间进行转换。这个例子中,我们假设要转换的数据是一个32位的数字。

module endian_converter(

input wire clk, // 时钟信号

input wire [31:0] data_in, // 输入数据,假设为大端格式

input wire [2:0] mode, // 模式选择信号,2'b00为大转小,2'b01为小转大

output reg [31:0] data_out // 输出数据

);

// 根据模式选择信号进行字节序转换

always @(*) begin

case (mode)

2'b00: begin // 大端转小端

data_out[7:0] = data_in[31:24];

data_out[15:8] = data_in[23:16];

data_out[23:16] = data_in[15:8];

data_out[31:24] = data_in[7:0];

end

2'b01: begin // 小端转大端

data_out[7:0] = data_in[7:0];

data_out[15:8] = data_in[15:8];

data_out[23:16] = data_in[23:16];

data_out[31:24] = data_in[31:24];

end

default: data_out = 32'b0; // 无效模式,输出清零

endcase

end

endmodule

这个模块在每个时钟上升沿触发时执行转换。根据mode的值,数据会被重新排列。对于大端转小端(2'b00),最高有效字节(MSB)被移动到最低有效字节(LSB)的位置,而最低有效字节被移动到最高有效字节的位置。对于小端转大端(2'b01),数据保持不变,因为我们假设输入已经是按照预期的格式排列的。

审核编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

求助:请问这两种对电源处理方式的区别和它们的用法。2017-07-24 3651

-

PCB过孔阻焊的处理方式2019-12-31 9296

-

PCB线路板交叉布线的处理方式2020-01-03 4685

-

串口IDLE中断的处理方式是什么2021-12-08 1871

-

按键消抖都有哪些处理方式?2023-11-01 614

-

光盘销毁机的处理方式2009-12-31 4442

-

无铅PCB的设计方法和表面处理方式选择等介绍2017-09-27 1016

-

基于android采用异步处理方式开发移动护理程序的设计2017-10-26 720

-

介绍学习一种模拟信号的处理方式:对数处理2018-01-11 12453

-

【经验分享】系统常用 (电磁兼容)EMC处理方式2018-04-17 1273

-

阻抗匹配的四种处理方式2022-02-11 1453

-

PCB电镀中异常处理方式2022-08-11 819

-

AMT变速箱常见的故障及故障的处理方式2023-04-06 6611

-

浅析测力传感器的两种处理方式2021-12-20 1790

-

使用相序识别仪时,常见故障原因以及处理方式概述2023-12-19 2718

全部0条评论

快来发表一下你的评论吧 !