最全讲解上下拉电阻 上下拉电阻的选择与上下拉电阻的应用

描述

1. 拉电流和灌电流

电子元器件在广义上分为有源器件和无源器件。

v211205-来自:大话硬件

有源器件需要电源(能量)才能实现其特定的功能,比如运算放大器在有输入信号的前提下,如果不提供电源,运算放大器无法实现其放大功能。

无源器件在工作时,不需要外加电源,只要输入信号就能正常工作,比如在信号线上串联33Ω的电阻,无论是否提供电源,只要有信号经过,电阻就能实现限流的作用。

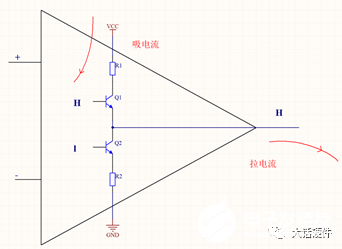

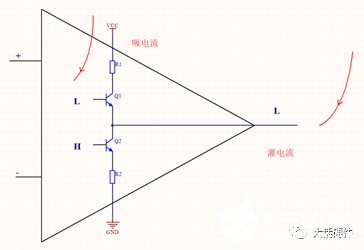

通常定义流入器件的电流为正,流出器件的电流为负。 器件输入端有电流流进时,称为吸电流,属于被动;器件输出端有电流流出时,称为拉电流,属于主动;器件输出端有电流流入时,称为灌电流,属于被动。下面以运算放大器工作为例。

对电源来说,运算放大器属于负载,电源提供电流让其正常工作,此时运算放大器在吸收电流。

对运算放大器来说,当它输出高电平,提供负载电流时,此时电流方向为负,称为拉电流;当它输出低电平,消耗负载电流,此时电流方向为正,称为灌电流。

2. 上/下拉电阻定义

在电子元器件间中,并不存在上拉电阻和下拉电阻这两种实体的电阻,之所以这样称呼,原因是根据电阻不同使用的场景来定义的,其本质还是电阻。就像去耦电容,耦合电容一样,也是根据其应用场合来取名,其本质还是电容。

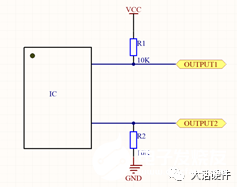

上拉电阻的定义:在某信号线上,通过电阻与一个固定的高电平VCC相接,使其电压在空闲状态保持在VCC电平,此时电阻被称为上拉电阻。

同理,下拉电阻的定义:将某信号线通过电阻接在固定的低电平GND上,使其空闲状态保持GND电平,此时的电阻被称为下拉电阻。

如下图所示,R1为上拉电阻,R2为下拉电阻。如果R1的阻值在上百K,能提供给信号线上负载电流非常小,对负载电容充电比较慢,此时电阻被称为弱上拉。

同理当下拉的电阻非常大时,导致下拉的速度比较缓慢,此时的电阻被称为弱下拉。而当上下拉的电平可以提供较大的电流给芯片时,此时的电阻被称为是强上拉或强下拉。

3. 上/下拉电阻的应用

根据上拉电阻和下拉电阻的含义,最常见的几种用法如下。

(1)用在OC/OD门

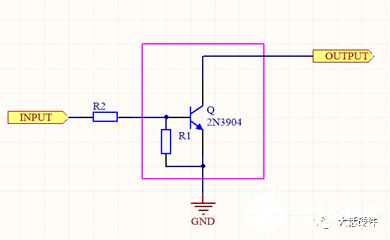

所谓OC门就是Open Collector,集电极开路,如下图所示:

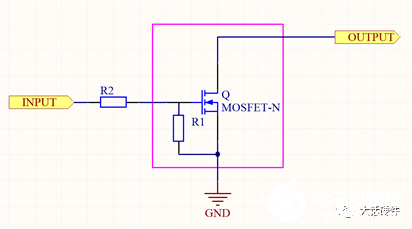

所谓OD门就是Open Drain,漏极开路,如下图所示。

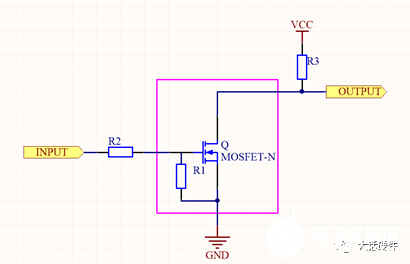

因此,OC门是针对三极管来说,OD门是针对MOS管来说。从OC门和OD电路可以看出,当输入电平为H时,输出电平为L,当输入电平为L时,此时输出电平为不稳定的状态,即高阻态,容易受到外界的干扰。 OC门和OD门不具备输出高电平的能力。此时,如果在集电极或漏极上增加上拉电阻,如下图所示:

当输入为高电平时,输出还是为低;输出为低电平时,输出电平为VCC。此时的OC门和OD门就具备了输出高、低电平的功能,而且电平被固定的钳位在VCC或者GND。

(2)用在按键电路

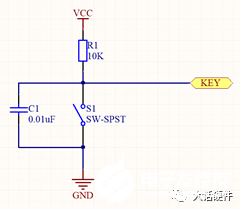

按键电路的工作原理是当按键未被按下和按下时电平取反,MCU通过检测到该管脚的信号电平被取反了,判断按键是否被按下。原理图如下:

当按键未被按下时,此时MCU的IO口检测到高电平;当按键被按下时,此时检测到低电平.上拉电阻是为了保证按键未被按下时处于一个固定的高电平。

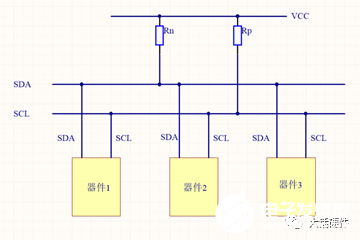

(3)用在IIC总线

IIC总线上的上拉电阻是必须要增加的,为了保证空闲状态时,SDA和SCL都处于高电平。

当IIC协议用在电平是3.3V以上时,推荐使用4.7K的上拉电阻。当电压小于3.3V时,推荐使用2.2~3K左右的上拉电阻(经验值)。

(4)用在逻辑IC悬空的管脚

数字逻辑电路中由于内部逻辑门会同时开通和关断,SSN噪声相比一般的电路较大,管脚悬空就比较容易受到芯片内部和外界的电磁干扰,在数字电路中不用的输入脚都要接固定电平,通过推荐使用1k电阻接高电平或接地。

(5) 用在终端匹配

上下拉电阻经常用在高速电路中,进行终端匹配。由于传输线的阻抗不连续会引起信号号的反射,导致波形出现过冲,回沟,振铃等现象。因此,必须在传输上进行源端和终端的匹配。

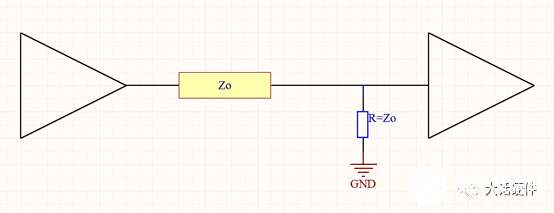

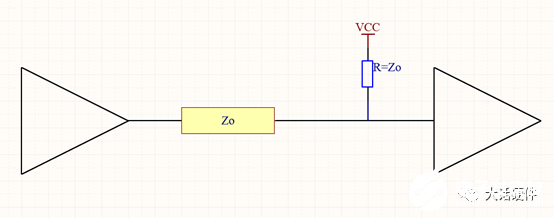

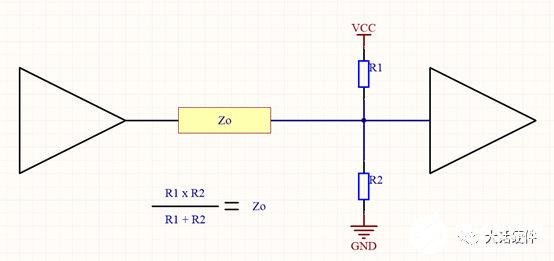

终端匹配常规来说具有两种类型,并联端接和戴维南端接。

并联端接——在终端并联一个与传输线特征阻抗一致的电阻到VCC或者GND。终端并联端接的优点信号能量反射回源端之前,在负载端会消除掉,缺点是上下拉电阻会有功耗的产生。

戴维南端接——戴维南端接也称为分压器端接,采用上拉电阻和下拉电阻同时接在终端上。优点是可以降低终端对源端驱动能力的要求,缺点是上下拉电阻都存在功耗。

当然,上下拉电阻还有其他很多场合根据芯片的要求或者是电路的设计需要增加上下拉电阻。比如在电平转换电路中,可以使用上拉电阻进行电平之间的转换。

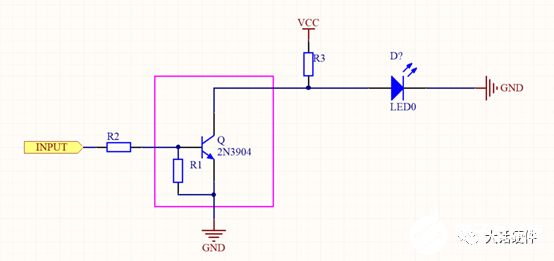

在单片机驱动类似LED的负载时,使用上拉电电阻可以提高I/O口的驱动能力。在三极管的BE之间增加下拉电阻,可以保证三极管在初试状态下处于稳定关断的状态。

4. 上/下拉电阻的选型

(1) 从功耗消耗的角度

上拉电阻和电源相连接,下拉电阻和GND相连接,在对电阻进行选型时,需要考虑到电阻自身带来的损耗。比如在按键电路中,电阻取10K可以满足条件,取20K也可以满足条件。但是明显电阻取20k时,电阻消耗的能量会更低。在对待机有需求的电路中,需要严格控制上下拉电阻的取值。 (2) 从驱动能力的角度 驱动能力的大小和提供的电流有关系。比如在OC门和OD门电路中,上拉电阻取太大,在输出高电平时,无法为后级提供较大的电流。如下图所示,LED正常工作时需要5~10mA电流,如果电阻取太大,LED灯无法点亮,因此需结合LED灯的电流和电压来选取上拉电阻。

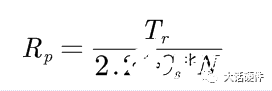

(3) 从信号速率的角度 在IIC的总线上需要增加上拉电阻,上拉电阻太大,会减慢信号由低向高电平转变的时间,上升沿变缓,影响信号上速率。 根据信号上拉电阻Rp的计算公式:

其中: Tr——信号上升沿爬升时间; Cs——信号线上负载的寄生电容 N——信号线上并联器件的个数;

一般在数据手册中会提供Tr和Cs,N为总线上并联的器件个数和具体的使用场景有关,根据上面的参数,可以计算出上拉电阻的值。

5. 总结

本篇文章主要从四个方面对上下拉电阻进行的归纳和总结。拉电流和灌电流是两个经常容易混淆的概念,因此在文章开始就进行了说明。对于上下拉电阻的应用并不仅仅体现在文章中提到的5点。而在选型的时候,需要从多个角度考虑器件是否能满足电路的需求。

来自:大话硬件

---The end---

限时免费扫码进群,交流更多行业技术

推荐阅读▼

电池、电源

硬件文章精选

华为海思软硬件开发资料

感谢点赞、在看、分享,让知识变得更简单

-

RS485总线上下拉电阻的选择2022-12-14 10286

-

上下拉电阻应用很简单吗?哪些地方要加上下拉电阻?2023-10-08 3908

-

电阻上下拉功能实现原理详解2023-11-13 3560

-

上下拉电阻的用法2012-08-16 3178

-

上下拉电阻的用途2012-10-24 12245

-

上下拉电阻的作用2015-04-18 26913

-

如何选择RS-485上下拉电阻?2019-05-21 3254

-

上拉电阻和下拉电阻的选型和计算2015-11-30 1895

-

上下拉电阻分析2017-07-24 2321

-

上下拉电阻的接线方法及作用介绍2019-09-30 20664

-

下拉电阻选择2020-02-27 7664

-

详解RS-485上下拉电阻的选择2022-01-26 1384

-

上下拉电阻在电路设计中的应用2022-11-23 3504

-

电路设计:上下拉电阻应用很简单吗?2023-03-17 2364

-

电阻是如何实现上下拉功能的呢?2024-02-04 2398

全部0条评论

快来发表一下你的评论吧 !