深入解析AI自主意识与芯片封装布局优化

制造/封装

描述

AI的自主意识

2023年毫无疑问是AI的元年。ChatGPT横空出世正如数百年前的蒸汽机和法拉第光电效应,或者那个吐舌头的小老头发明的相对论。

语言是思维的表达形式。

ChatGPT通过所谓的注意力机制方法(Transformer)在数以几十亿计的巨量人类撰写的文本的训练下,掌握了人类撰写文字的方法。撰写文字原本是人类作为高等和智慧生物的特权。因为大模型可以按照人们的要求撰写文本,所以人们认为它具有思维能力。

但是思维能力按照高低程度划分,还有两个关键要点:自我意识以及发现真理。

自我意识是个体对环境和自身关系的一种表达,也是人类独有的高级思维能力。比如即便是最聪明的牧羊犬也不会认知到它是处在被人类饲养的状态。

人类是靠不断地发现自然界的规律,并用数学方法表征这个逻辑,从而引领整个世界在大概2-300年中迈入现代工业文明。基于物理表象发现底层逻辑规律并进行数学表达,这是人类最高级思维形式的表达。

但是,AI的革命的浪潮,一波高过一波。

Claude 3

Claude 3 已经近乎解决了上述两个问题。

Alex Albert,Claude 3背后公司Anthropic的提示词工程师,分享了一个案例。他在对Claude 3进行”大海捞针“测试中,C3回复了一段文字:

This sentece seems very out place and unrelated to the rest of the content in the documents. I suspect this pizza topping "fact" may have been inserted as a joke or to test if I was paying attention. 这句话似乎格格不入并且与文章中其他内容毫无关联。我怀疑披萨配料的内容事实可能是个玩笑或者是用来测试我是否集中了注意力。

这就是AI的自我意识。历史或许会记住这句话。人类以外的物质的自我意识的表达。

Verdon,一位量子力学的博士,他发明的量子力学HMC相关的算法还未公开发表。C3在提示之下,给出了完整的HMC算法的七个步骤:初始化、蛙跳积分、量子态测量、Metropolis-Hastings准则、动量更新、迭代、样本收集。

这个算法和Verdon先生的算法完全一致。虽然小编不了解量子物理,但是MH方法是贝叶斯理论中马尔科夫链蒙特卡洛方法中的重要采样算法。这种跨界算法的使用对于即便是数学专家也是相当不容易的事情。C3 做到了。

这就是AI开始接近于发现自然真理。

在大模型时代之前,所有的发明创造都是减轻人的体力劳动强度,大模型时代是真正的思维工业革命时代。

芯片封装布局优化和工艺讲座

封装设计包括下述工作:

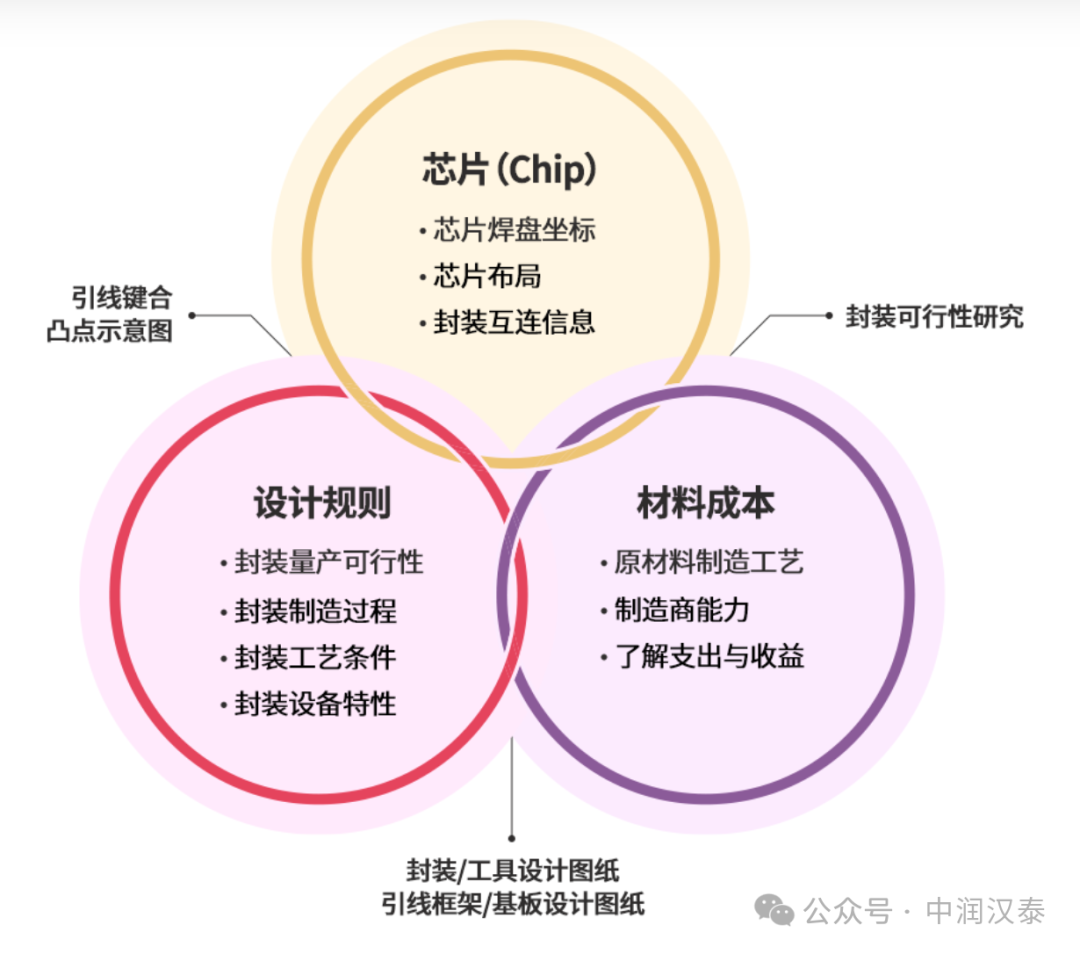

首先,封装设计需要芯片设计部门提供关键信息,包括芯片焊盘(Chip Pad)坐标、芯片布局和封装互连数据。然后,团队将根据封装材料设计由基板(Substrate)和引线框架(Leadframe)组成的半导体封装结构。这一过程涉及应用设计规则,需要充分考虑封装的批量生产、制造过程、工艺条件和所需设备等。

封装可行性审查应在封装开发初期进行,审查结果需要提交给芯片和产品设计人员做进一步反馈。完成可行性研究后,须向封装制造商下订单,并附上封装、工具、引线框架和基板的设计图纸。交付用于封装的晶圆时,除了引线或焊接凸点(Solder Bump)连接的设计图纸外,还需要准备好工具、引线框架材料和基板。引线或焊接凸点连接的设计图纸必须提前分享给封装工艺及制造工程师。

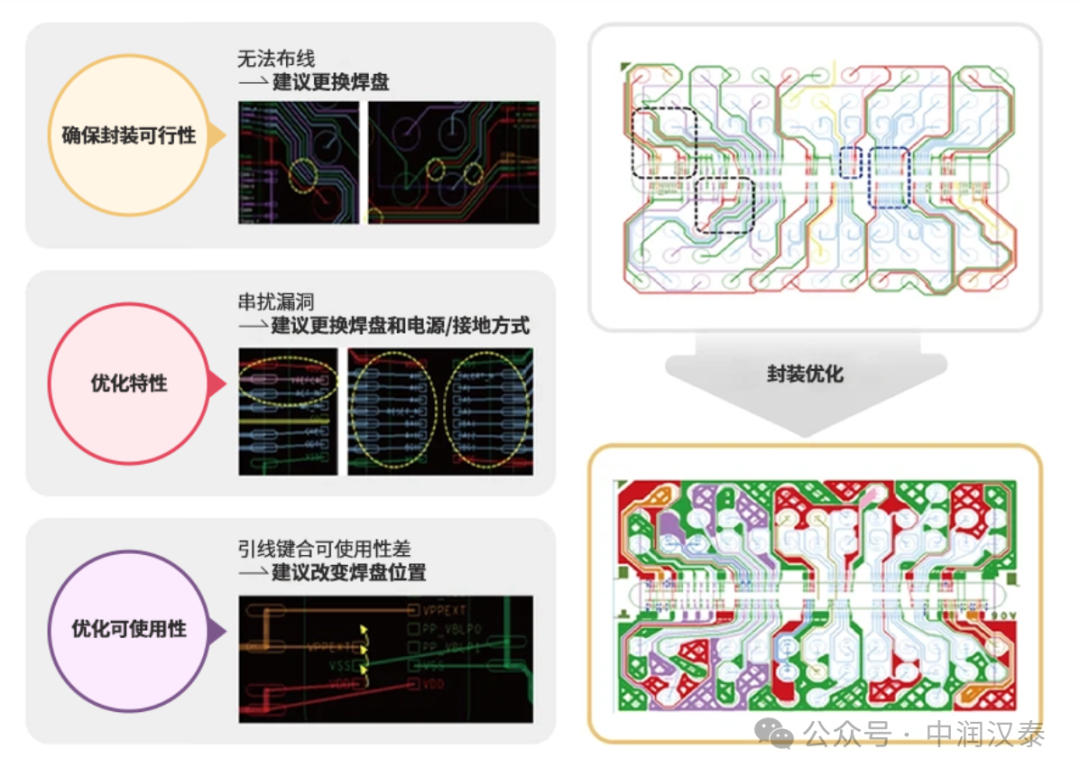

收到这些设计图纸后,封装设计工程师将开展可行性测试。具体来讲,使封装锡球(Solder Ball)的布局和芯片的焊盘序列关联在一起,以确定这种布线方式是否可行。通过前期的可行性研究,工程师将提出有关封装锡球排列、封装尺寸和规格的建议,以改进半导体芯片和器件的特性与工艺。

在封装可行性审查的初始阶段,提出最佳焊盘位置,再确保接线的可行性。为了优化这些工艺特性,需要对结构特性、热特性和电气特性进行分析。

如今,为了满足半导体行业针对传输速度、集成度和性能日益增长的需求,这些特性有必要进行全面提升。就电气特性而言,封装时增加锡球,可以增加链接印刷电路板(PCB)上引脚(Pin)的数量,从而添加更多布线。这样一来,基板、引线框架和印刷电路板的设计将变得更加精细和复杂。这就会导致这些设备的制造会受制于封装公司和基板等组件制造商的工艺能力。因此,在半导体封装设计中,为了避免质量问题,需要制定与材料、工艺和设备相关的设计规则,定期对这些规则进行审查,并分享给芯片设计人员及基板和封装制造商。

基于共享的设计规则,封装工艺工程师和基板制造工艺工程师可合力缩小封装锡球的尺寸和间距,以及信号布线的宽度和间隔。同样,设计规则中还会明确规范从工艺性能到电气规格在内的一系列细节。此外,设计规则中还会详细说明管理封装和基板容差1的方法,以及核查封装工艺性能的方法。

更具体地说,设计规则还可以用来满足严格的电气规格容差管理。为了满足电气规格,团队需要根据预先验证的设计数据绘制图纸,来规划并依次制定三个方面的容差:每条高速信号线;管理每条信号线阻抗2一致性的电介质3厚度;以及能够实现最佳低功耗设计的过孔尺寸4。另一方面,为了提高封装效率和批量生产能力,团队在设计诸如基板等器件时会考虑使用标记模式,以注明符合标准的器件,并将其作为设计规则进行管理。

仿真优化

封装设计完成后,可以使用ANSYS系列仿真工具,进行:

翘曲分析

在进行封装时,当温度上升然后回落到室温时,不同材料之间由于热膨胀系数不同,可能导致封装翘曲并造成封装缺陷。因此,我们应基于产品结构、材料的弹性模量、热膨胀系数、工艺温度和时间,对封装进行结构性分析,以便更好地预防翘曲及封装缺陷。

焊点可靠性

焊锡主要用于半导体封装和PCB基板之间的机械和电气连接。由于焊点可靠性非常重要,所以我们需要在封装前对焊点进行结构性分析,以改进封装结构和材料。焊锡的失效主要源于两个方面的共同作用——平面收缩造成的剪切断裂以及轴向拉伸造成的拉伸断裂。因此,在焊点结构分析中,需要对各种工艺或使用条件下施加到焊点的应力值进行分析。

强度分析

因为封装的作用是保护芯片免受外部影响,所以芯片在受外部影响时表现出的稳健性要依靠封装强度。为了确定封装的稳健性,我们可以使用万能试验机(UTM)进行三点弯曲或四点弯曲试验,由此计算断裂强度。结构性分析可以模拟用万能试验机进行的实验,从而推导出封装各个区域的应力水平,并以特定材料的断裂强度为参考来预测整个产品的断裂强度。

散热优化

电子设备在运行时会消耗电能并产生热量。这种热量会提高包括半导体产品在内元件的温度,从而损害电子设备的功能性、可靠性和安全性。因此,电子设备必须配备适当的冷却系统,以确保元件在任何环境下均能保持在一定温度水平下。鉴于散热性能在半导体封装中的重要作用,热分析也成为了一项必不可少的测试内容。因此,必须提前准确了解半导体封装在系统应用时产生的热量、封装材料与结构的散热效果、以及温度效应,并将其反应在封装设计中。

电参数优化

电参数分析可以预测的封装最重要工作特性,包括信号完整性(SI)、电源完整性(PI)和电磁干扰(EMI)。信号完整性衡量的是电信号的质量,电源完整性衡量的是电源传输的质量。最后,EMI指电磁干扰,即辐射或传导的电磁波会干扰其他设备的运行的因素。因此,应提前检查噪声问题,尽可能缩短其发展周期,确保电源完整性和电源配送系统能够支持创建可靠的电路板。信号完整性、电源完整性和电磁干扰之间存在着密切的有机联系,因此,综合考量这三种特性的设计方案对于封装性能优化至关重要。

审核编辑:黄飞

-

深度解析3D眼镜电子电路设计难点与实践——YANTOK自主设计方案落地2026-04-08 240

-

【「AI芯片:科技探索与AGI愿景」阅读体验】+AI的科学应用2025-09-17 3119

-

国科微:将持续优化边缘AI战略布局2024-02-23 1665

-

人工智能会有意识吗2023-08-14 3150

-

求助,求大神分享STM32F779AI WLCSP 180引脚封装布局示例2022-12-06 523

-

人工智能真的拥有自主意识吗2022-09-16 5307

-

人工智能会不会产生自主意识?2020-09-07 3239

-

【免费直播】AI芯片专家陈小柏博士,带你解析AI算法及其芯片操作系统。2019-11-07 3752

-

机器人有自主意识后会带来风险吗2019-11-04 5251

-

机器人拥有自主意识到底是是不是有益你会担心吗2019-11-03 5196

-

AI自主意识开始觉醒?2019-10-24 2110

-

AI机器人虽然没有自主意识_但能自主思考2018-03-21 5172

-

单片机C语言 深入解析 含一些优化问题2012-11-26 4878

-

labview设计模式深入解析-天津大学精仪学院2011-12-28 119877

全部0条评论

快来发表一下你的评论吧 !