FPGA的时钟电路结构原理

可编程逻辑

描述

FPGA(现场可编程门阵列)的时钟布局,是其设计中至关重要的一部分。时钟信号通常用于同步逻辑电路中的各个模块,确保它们在正确的时间进行操作,以避免时序问题和数据错位。

FPGA 的时钟原理基本概念:

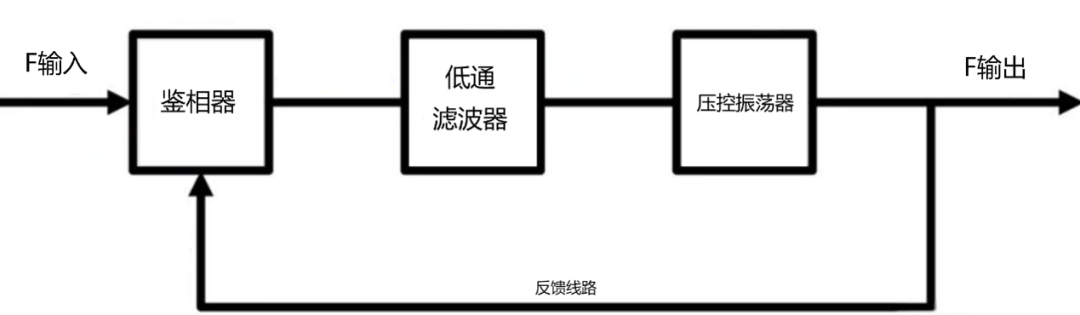

☋ 时钟资源:FPGA 中包含一些全局时钟资源。以AMD公司近年的主流FPGA为例,这些时钟资源由CMT(时钟管理器)产生,包括DCM、PLL和MMCM等。其中DCM在旧的器件中应用,目前已被淘汰;PLL为模拟锁相环,大家较为熟悉,可以用之进行分频、倍频及作相位调节;

图1 锁相环(PLL)的基本电路结构图

MMCM在PLL的功能基础之上,提供更为强大的高阶功能:如动态相位调节、时钟扩频功能及时钟分配动态变化等。

☋ 时钟分配与布线:FPGA 中通常有多个时钟资源,时钟信号需要正确分配到逻辑电路中。时钟信号的布线质量对设计的性能和功耗都有很大影响。

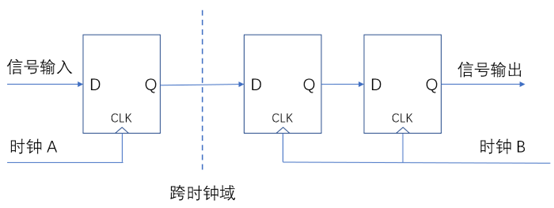

☋ 时钟域交叉:当设计中存在多个时钟域时,需要正确处理不同时钟域之间的数据传输,以防止时序违规和异步时钟域之间的不稳定性问题

图2 经过多级寄存器的跨时钟域数据处理方式

☋ 时钟缓冲与时钟延迟:在 FPGA 中,时钟缓冲和时钟延迟对时钟信号的传播和同步至关重要。需要注意时钟缓冲的插入和时钟延迟对设计的影响。在需要进行跨时钟域数据传输时,可能需要使用时钟域转换器来实现时钟域之间的数据同步。时钟域转换器通常包括异步 FIFO 缓冲器、双口 RAM 等。

☋ 时序约束:通过时序约束来告诉综合工具和布局布线工具时钟的频率和时序要求,以确保时序要求得到满足。尤其对于每个时钟域,都需要明确指定相应的时序约束,包括时钟频率、时钟起始相位、时钟传播延迟等,以确保时序要求得到满足。通常包括:

◆时钟频率约束:指定电路中时钟信号的最大频率,以确保电路在给定时钟频率下能够正常工作。

◆时序路径约束:确定电路中各个信号的传输路径和时序关系。时序路径约束通常包括输入到输出的传输延迟、时钟到达时间等信息,以确保信号在特定时钟周期内能够到达目标节点。

◆时钟域约束:确定电路中使用的各个时钟信号的逻辑域,并且定义各个时钟域之间的时序关系。

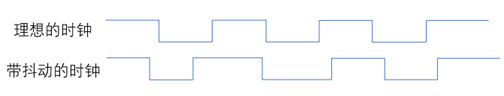

☋ 时钟偏移和抖动:时钟信号可能存在偏移和抖动,这可能导致时序不稳定或违反时序约束。

图3 理想的时钟和带抖动的时钟对比图

解决 FPGA 中的时钟问题需要深入理解 FPGA 架构和时钟原理,并结合设计工具的使用技巧和实践经验。正确的时钟设计能够有效提高 FPGA 设计的性能、可靠性和稳定性。

了解以上的时钟基本概念之后,我们可以对用户实际设计中的时钟使用情况作进一步的分析:

时钟使用情况进一步分析

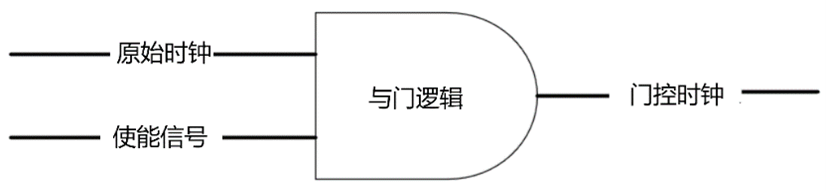

☊ 门控时钟:此类时钟出现的目的是为了降低芯片的功耗,因此在ASIC芯片中经常应用。可分为高有效、低有效、XOR门结构、MUX结构控制等多种形式。

图4 一个简单的门控时钟原理示意图

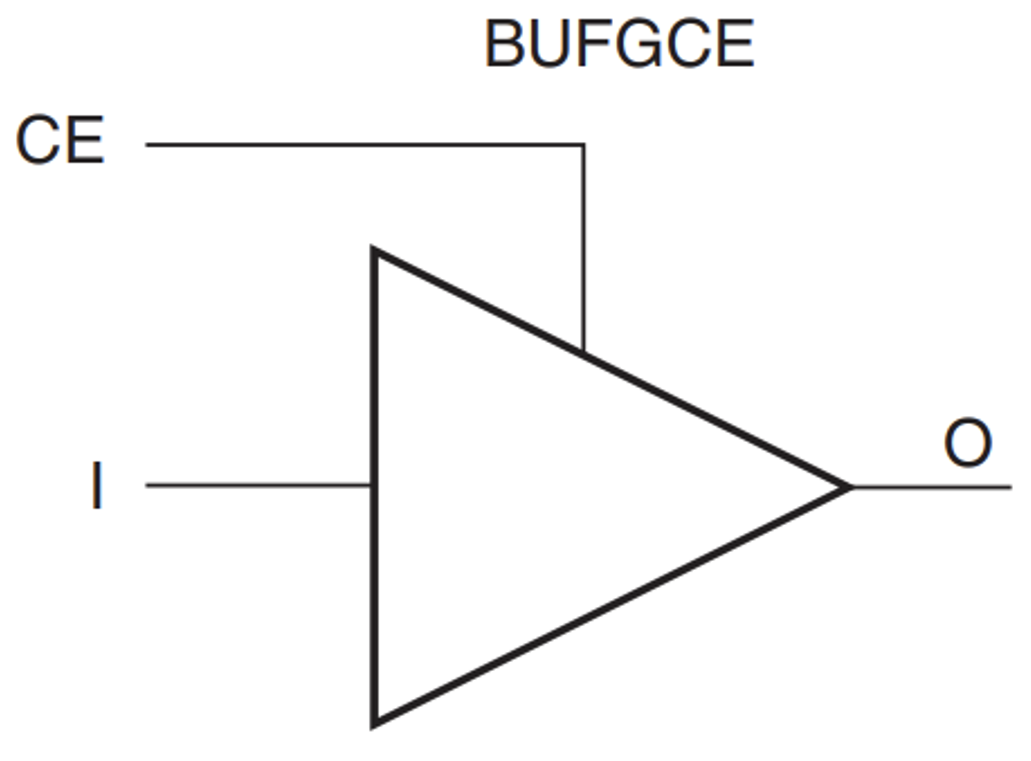

由图可见,门控时钟实际上是输入到触发器时钟端的时钟,来自组合逻辑;那么,问题在于组合逻辑在布局布线之后肯定会产生毛刺,而如果采用这种有毛刺的信号来作为时钟使用的话,将会出现功能上的错误,同时还容易增加延时,引起时钟漂移,降低可测性;我们的改进方式是:用组合逻辑驱动CE端口,而不去改动clk端口;原厂的元件库提供了一种更为方便的方式:通过引入时钟缓冲器,既可以达到门控的效果,也避免了组合逻辑带来的时序风险。

图5 BUFGCE时钟缓冲器

☊ 同步时钟架构:也可以称为“单时钟方式”。这种时钟的工作方式往往出现在类emulator的硬件系统中,其主要特点是统一使用一个单时钟(root clock)输入,随后再由该时钟分出很多衍生时钟作为各模块的使用。

这种时钟的结构好处是:对于非常复杂的时钟树结构,往往硬件系统本身能够提供的物理时钟源数量十分有限,且同步精度难以保证。那么采用这样的单时钟系统,不仅能够从源头上,保证所有时钟的同步性,同时,不需要对大量时钟作很多复杂的约束条件;最后,在调试过程当中,需要对时钟进行停止或启动的操作时,显得十分方便。

缺点是,在这种模式下,由于采样率的限制及时钟到达时间的延迟,信号保持时间(Hold time)的条件往往难以满足;所以,整个设计的频率不会跑得很快。

☊ 异步时钟架构:也可理解为“多时钟模式”。这种架构,一般在原型验证系统上用的较多,即:硬件系统本身提供很多路物理时钟(通过晶振或时钟发生芯片产生);通过增加定制化的时钟约束,用户的设计,可以较“单时钟方式”跑的更快一些。

这样的好处:在硬件系统需要连接软件上位机作软硬件联合调试时,有着较大的性能优势并缩短整个系统运行的时间。缺点是由于其时钟的不可停止性,那么在功能debug调试上存在一定的限制,比方说看到的信号的位置不精准等等。

基于以上各种情况的优化:

芯启源公司最早开展MimicPro产品的时钟架构设计时,就考虑到了上述这些问题的利弊之处。通过潜心开发自有专利的时钟工作方式,在结构上,能够较为完整地保留住设计的原始时钟架构。

相较于传统仿真加速产品的“单时钟方式”,MimicPro系统的工作频率可以快达数倍,性能更佳。与此同时,也能够提供非常丰富的Debug调试功能;这点相对于普通的原型验证产品来说,无疑又多出了一把在功能验证过程中的“除错利器”。经过多年的磨砺,产品日趋成熟和稳定;并且在多个头部客户处落地。我们相信,助力于复杂大芯片设计和验证,MimicPro系列产品将继续成为稳定、良好的测试平台,加速客户的产品早日面市。

审核编辑:黄飞

-

Xilinx 7系列FPGA的时钟结构解析2023-08-31 4670

-

Xilinx FPGA时钟资源概述2023-07-24 1603

-

FPGA时钟系统的移植2022-11-23 1358

-

一文详解Xilin的FPGA时钟结构2022-07-03 5098

-

(08)FPGA时钟概念2021-12-29 630

-

FPGA的设计中的时钟使能电路2020-11-10 6482

-

由FPGA构成的电路结构与性能分析2019-12-26 2450

-

一种基于FPGA的时钟跟踪环路的设计与实现2017-11-30 928

-

赛灵思FPGA全局时钟网络结构详解2013-11-28 14490

-

基于FPGA的时钟设计2011-09-21 4263

-

基于FPGA的时钟跟踪环路的设计2010-11-19 600

-

FPGA时钟分配网络设计技术2010-08-06 681

全部0条评论

快来发表一下你的评论吧 !