一文读懂MOSFET开关损耗介绍

描述

MOSFET的操作可以分为两种基本模式:线性模式和开关模式。在线性模式下,晶体管的栅源电压足以使电流通过通道,但通道电阻相对较高。通道上的电压和通过通道的电流都很大,导致晶体管内的功耗很高。

在开关模式下,栅源电压要么低到足以阻止电流流动,要么高到足以使FET进入“完全增强”状态,此时通道电阻大大降低。在这种状态下,晶体管像一个闭合开关:即使有大电流通过通道,功耗也会低或中等。

随着开关模式操作接近理想状态,功耗变得可以忽略不计。开关要么完全不活跃,零电流因此零损耗,要么完全活跃,最小电阻因此最小损耗。由于其高效性,开关模式在许多应用中被使用——数字CMOS电路、电源和D类放大器都是很好的例子。

然而,实际的MOSFET开关涉及设计者在选择元件和布置电路板时需要考虑的损耗。在本文中,我们将讨论三种非预期的功耗:导通损耗、开关损耗、栅极电荷损耗。

导通损耗:

导通损耗是指电流通过MOSFET通道的非零电阻时消耗的功率。完全增强的MOSFET的漏源电阻表示为RDS(on)。

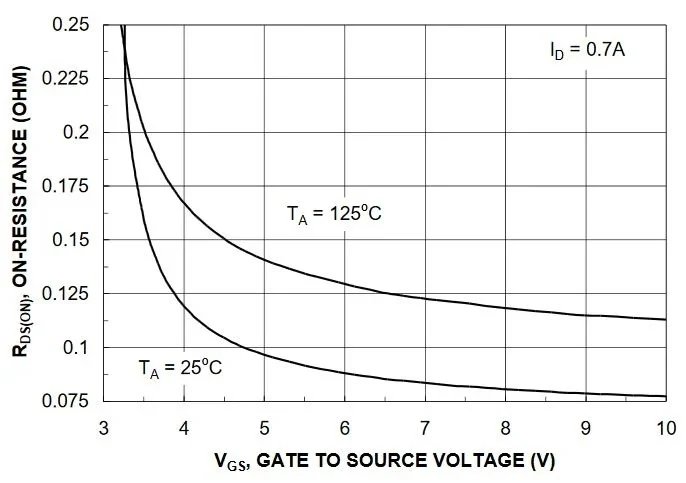

图1

图1

图1显示了随着栅源电压增加通道电阻如何减小。完全增强状态对应于曲线的低斜率部分。

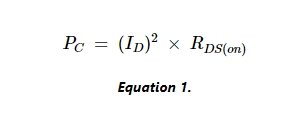

瞬时导通损耗(PC)可以使用电功率的标准公式之一计算:

其中ID是FET的漏源电流。

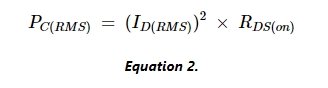

我们还可以使用RMS电流而不是瞬时电流来计算时间平均导通损耗:

由于我们假设通过MOSFET的电流量由应用需求控制,减少导通损耗的方法是降低RDS(on)。这首先通过仔细选择元件来实现——一些现代FET,包括碳化硅和氮化镓,提供极低的RDS(on)。

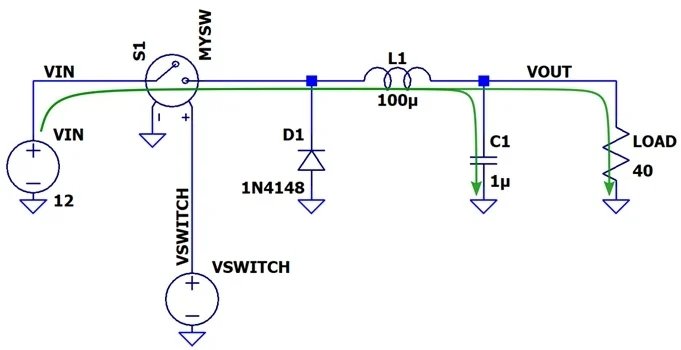

图2

图2

除此之外,还应确保操作条件和周围电路有助于FET达到尽可能低的通道电阻。当需要大电流时,甚至几欧姆的小数部分都可能很重要,例如图2中的降压转换器。

开关损耗:

在简化的开关模式操作模型中,MOSFET要么完全导通,要么完全关断。然而,更现实的模型必须承认两种状态之间的过渡不是瞬时的。相反,每次开关时,FET都会短暂地在高功耗线性模式下工作。这导致了第二种损耗,称为开关损耗。

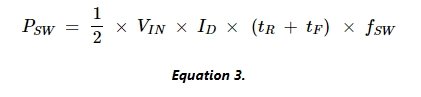

计算开关损耗并不简单,因为导通和关断状态之间的过渡是一个高度动态的过程,在此期间通道电阻会连续变化。ROHM Semiconductor在其应用笔记中提出了公式(3):

该公式表明开关损耗(PSW)取决于以下所有因素:

用于驱动FET的开关电流的电压(VIN)。

FET的漏电流(ID)。

开关波形的上升和下降时间(tR和tF)。

开关频率(fSW)。

栅极电荷损耗:

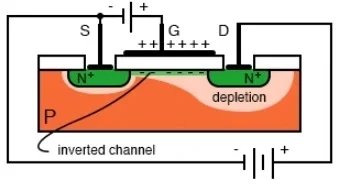

所有MOSFET都有一层绝缘层,可以防止电流通过栅极端口流动——这是它们与其他类型的场效应晶体管的区别之一。然而,严格来说,这种绝缘层只阻挡稳态电流。

图3

图3

如图3所示,MOSFET的绝缘栅极是一个电容结构;因此,直到栅极电容完全充电或放电之前,瞬态电流都会在栅极驱动电路中流动。

这构成了开关模式MOSFET的又一个耗散损耗源。打开和关闭FET需要改变栅极电压,当瞬态电流流过寄生电阻时,会发生功耗。

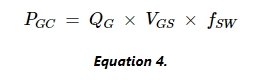

栅极电荷损耗(PGC)的公式如下:

其中:

QG是FET所需的总栅极电荷量

VGS是栅源电压

fSW是开关频率。

公式(4)引导我们得出一个重要的观察结果。需要更高栅极电荷的MOSFET会降低效率,因此设计者面临权衡:更大的栅极面积有助于降低RDS(on),从而减少导通损耗,但更大的栅极面积也增加了QG,从而增加了栅极电荷损耗。

总结

基于MOSFET的开关电路通常比依赖于晶体管线性操作模式的电路实现了更高的效率。然而,开关损耗确实存在。估算这些损耗的能力可以帮助你优化设计,避免潜在的严重热故障。

-

PFC MOSFET的开关损耗测试方案2022-10-19 2940

-

MOSFET开关损耗和主导参数2025-02-26 584

-

一文带你读懂MOSFET开关损耗计算!!(免积分)2025-03-06 798

-

功率MOSFET的开关损耗:开通损耗2017-02-24 6963

-

功率MOSFET的开关损耗:关断损耗2017-03-06 7346

-

全SiC功率模块的开关损耗2018-11-27 4784

-

【干货】MOSFET开关损耗分析与计算2021-01-30 5496

-

如何更加深入理解MOSFET开关损耗?2021-04-07 3484

-

集成高侧MOSFET中的开关损耗分析2022-11-16 788

-

理解功率MOSFET的开关损耗2009-10-25 3680

-

MOSFET开关损耗分析2016-01-04 997

-

功率MOSFET的开关损耗分析2021-04-16 1589

-

DC/DC评估篇损耗探讨-同步整流降压转换器的开关损耗2023-02-23 2114

-

使用SiC MOSFET时如何尽量降低电磁干扰和开关损耗2023-11-23 2478

-

影响MOSFET开关损耗的因素2024-09-14 2787

全部0条评论

快来发表一下你的评论吧 !