资料下载

mpc5510单片机家庭数据表

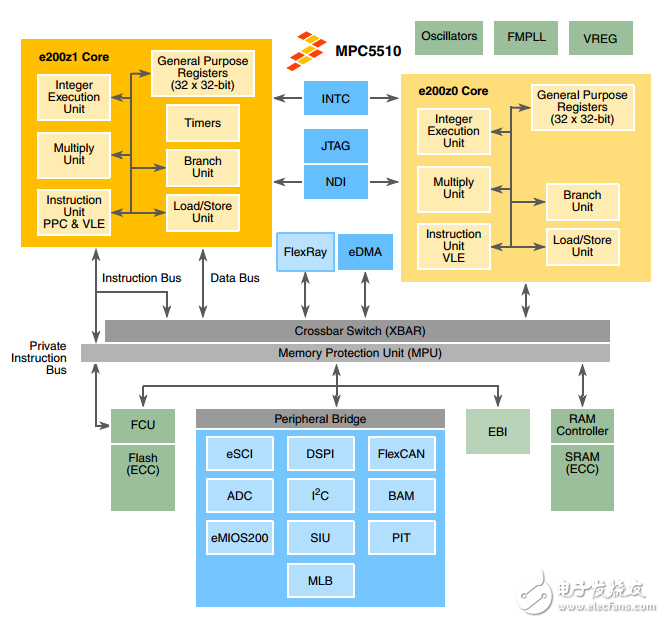

MPC5510 Family Features • Single issue, 32-bit CPU core complex (e200z1) – Compliant with the Power Architecture™ embedded category – Includes an instruction set enhancement allowing variable length encoding (VLE) for code size footprint reduction. With the optional encoding of mixed 16-bit and 32-bit instructions, it is possible to achieve significant code size footprint reduction. • Up to 1.5-Mbyte on-chip flash with flash control unit (FCU) • Up to 80 Kbytes on-chip SRAM • Memory protection unit (MPU) with up to sixteen region descriptors and 32-byte region granularity • Interrupt controller (INTC) capable of handling selectable-priority interrupt sources • Frequency modulated Phase-locked loop (FMPLL) • Crossbar switch architecture for concurrent access to peripherals, flash, or RAM from multiple bus masters • 16-channel enhanced direct memory access controller (eDMA) • Boot assist module (BAM) supports internal flash programming via a serial link (CAN or SCI) • Timer supports input/output channels providing a range of 16-bit input capture, output compare, and pulse width modulation functions (eMIOS200) • Up to 40-channel 12-bit analog-to-digital converter (ADC) • Up to four serial peripheral interface (DSPI) modules • Media Local Bus (MLB) emulation logic (works with two DSPIs, the e200z0, the eDMA, and system RAM to create a 3-pin or 5-pin 256Fs MLB protocol) • Up to eight serial communication interface (eSCI) modules • Up to six enhanced full CAN (FlexCAN) modules with configurable buffers • One inter IC communication interface (I2 C) module

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章