资料下载

MPC555产品简介

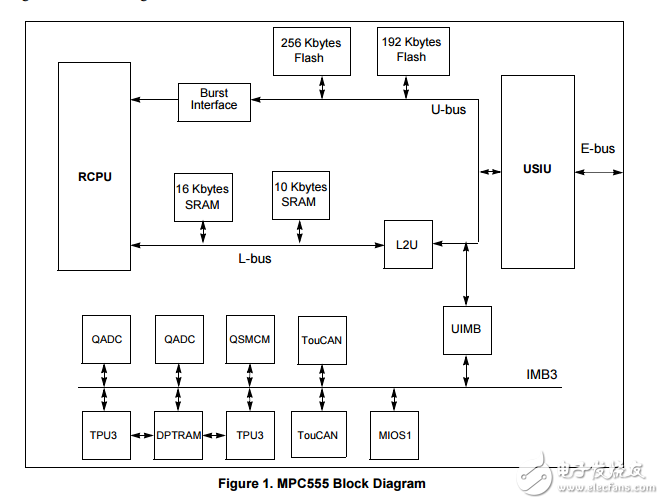

This document provides an overview of the MPC555 microcontroller, including a block diagram showing the major modular components and sections that list the major features. The MPC555 member of the Freescale MPC500 RISC Microcontroller family.

The MPC555 device offers the following features: • PowerPC™ core with floating-point unit • 26 Kbytes fast RAM and 6 Kbytes TPU microcode RAM • 448 Kbytes Flash EEPROM with 5-V programming • 5-V I/O system • Serial system: queued serial multi-channel module (QSMCM), dual CAN 2.0B controller modules (TouCANTM) • 50-channel timer system: dual time processor units (TPU3), modular I/O system (MIOS1) • 32 analog inputs: dual queued analog-to-digital converters (QADC64) • Submicron HCMOS (CDR1) technology • 272-pin plastic ball grid array (PBGA) packaging • 40-MHz operation, -40 °C to 125 °C with dual supply (3.3 V, 5 V) (-55 °C to 125 °C for the suffix A device) • 32-bit architecture (PowerPC ISA architecture compliant) • Core performance measured at 52.7-Kbyte Dhrystones (v2.1) @ 40 MHz • Fully static, low power operation • Integrated double-precision floating-point unit • Precise exception model

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章