唯样代理 适用于48V电池断开开关的80V双门极MOSFET及其应用仿真

电子说

描述

现代车辆电气系统的结构变得越来越复杂。这是由于负载数量的增加,从铅酸电池转变为锂离子或其他类型电池,以及对失效可操作等功能安全措施的需求。

1. 断开开关当今面临的挑战

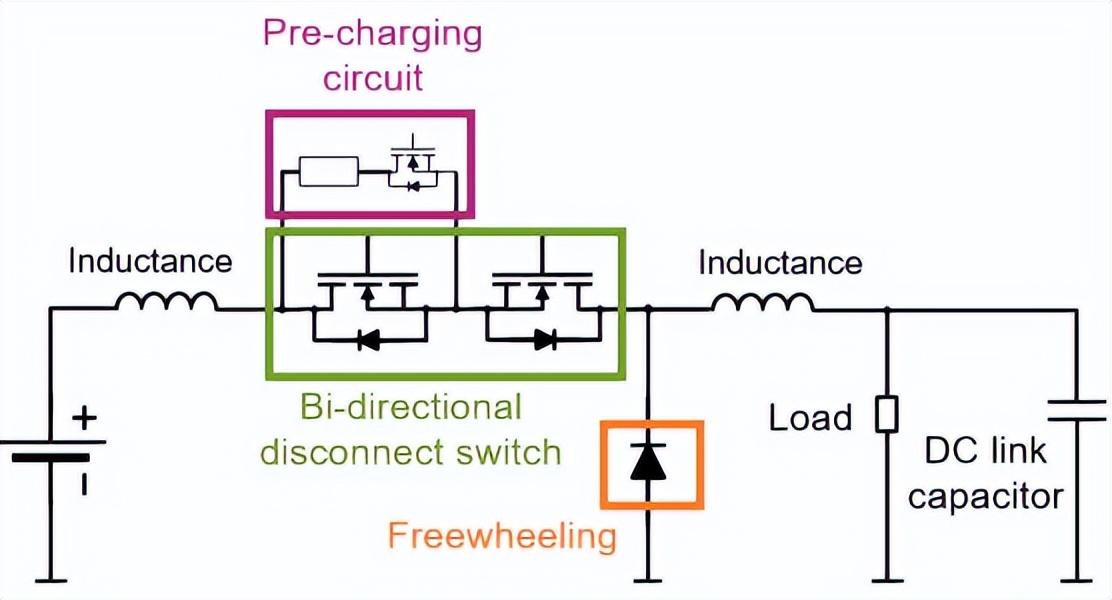

现代车辆电气系统的结构变得越来越复杂。这是由于负载数量的增加,从铅酸电池转变为锂离子或其他类型电池,以及对失效可操作等功能安全措施的需求。这些因素使得电池和负载隔离开关的使用也在增加,MOSFET成为了首选的大负载开关。为了实现稳态操作的主开关所需的通态电阻,通常会并联多个MOSFET。在许多情况下,主开关是双向的,可以阻止电池的充放电方向的电流。图一给出了电池断开开关的简化电路示意图。这种需要在两个方向上阻止电流是由于在故障事件(如过电压或由于短路造成的过电流)发生时所采取的保护措施。这对于离板连接尤其重要,比如连接其他控制单元与断开开关的线束。这些线束有很大的电感,必须在过电流关断后加以考虑。线束的电感储存相当大的能量,这些能量必须通过断开开关MOSFET或其他保护电路(如续流二极管)来耗散。

图1 带续流二极管和预充电路的典型双向电池断开开关

1.1

电容充电和冲击电流限制

在断开开关应用中,经常需要给靠近负载侧的大电容充电。然而,常规的MOSFET是不适合限制流进大电容的冲击电流的,这是因为安全工作区和转移特性的限制,比如跨导。

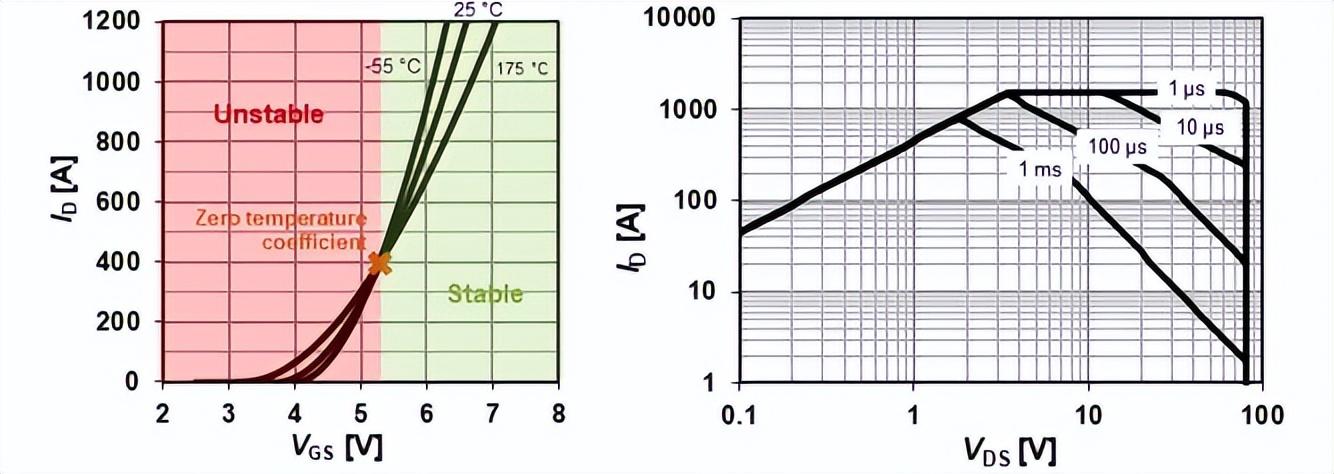

因为漏极电流对门极电压的依赖性,即跨导,非常陡峭,控制MOSFET的冲击电流会变得非常有挑战性。此外,温度系数通常也会对SOA产生影响。因此,限制电流通常变成不可能的任务。MOSFET有2个工作区域,表现在转移特性上的热稳定和热不稳定区域,如图2所示。高正温度系数导致的热不均匀分布或者热失控,工作在热不稳定区域会导致严重的性能衰退。另一方面,即使工作在热稳定区域,芯片的热分布也是均匀的,大电流也会引起高的自发热。由于优化RDS(on)的MOSFET具有高ZTC的特点,几乎不可能令其可靠的工作在线性模式,这使得其不适合许多应用场合。

图2 标准OptiMOSTM 5 沟槽 MOSFET安全工作区和转移特性

因此,典型的充电概念是通过使用昂贵的大功率电阻和一个小功率MOSFET组成独立的预充路径来限制电流,如图1所示。另一种方案是,带软启功能的DCDC变换器也可以用来给直流侧电容充电,花费可能更多。

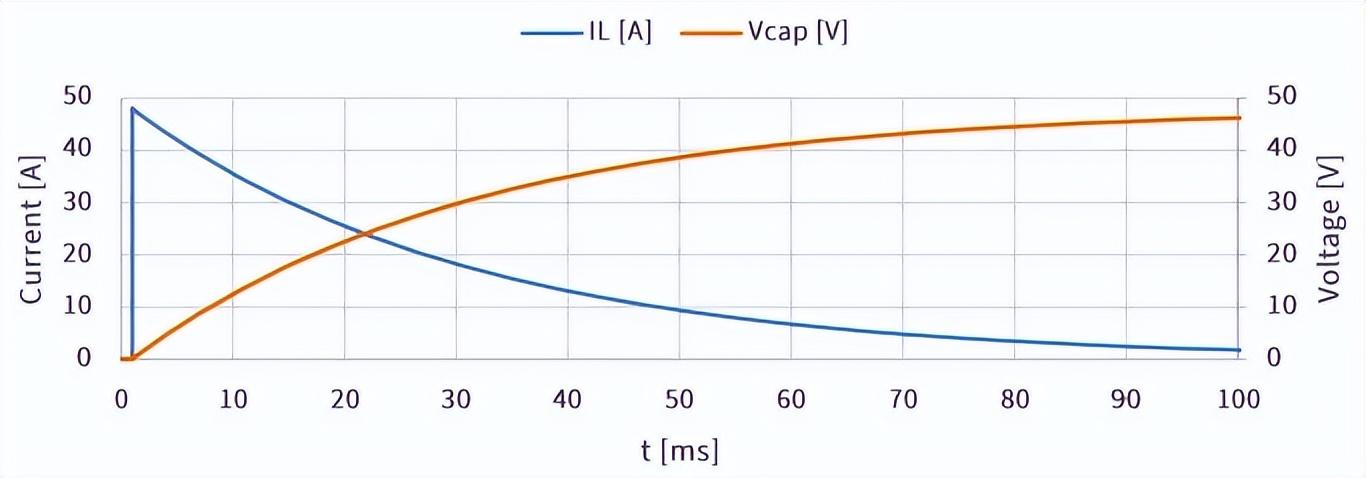

图3是功率电阻预充电路的示例充电波形。在这个例子中,1ohm的电阻用来给33mF的电容充电。曲线的形状是渐进的接近目标电容电压48V。充电过程在整个期间逐渐缓慢,这就是大家熟知的RC时间常数的行为。电阻上的损耗随电流剧烈地衰减。因此,电阻功率和自发热的单独控制不大可能最大化实现电容的充电速度。

图3 带预充电路的0至48V电容充电(1ohm, 33mF)

1.2

短路鲁棒性(雪崩击穿和主动电压钳位)

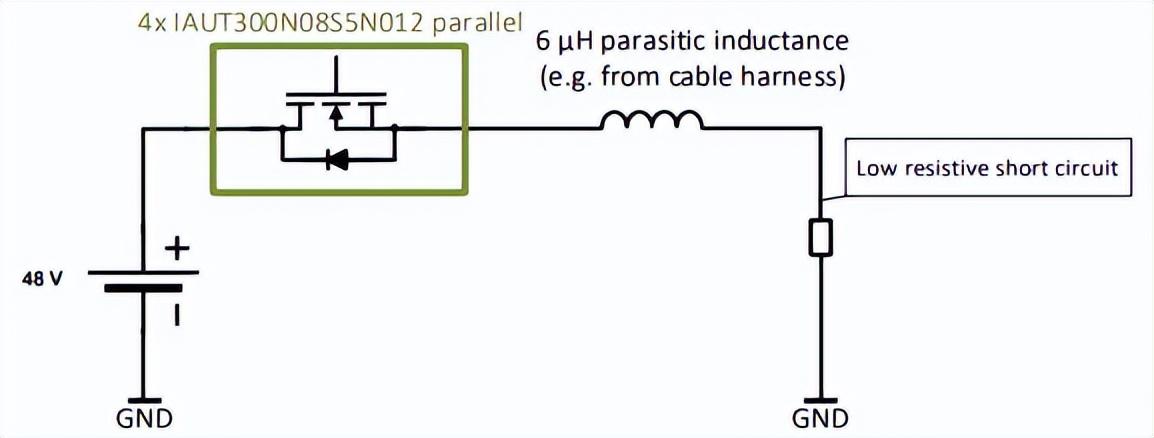

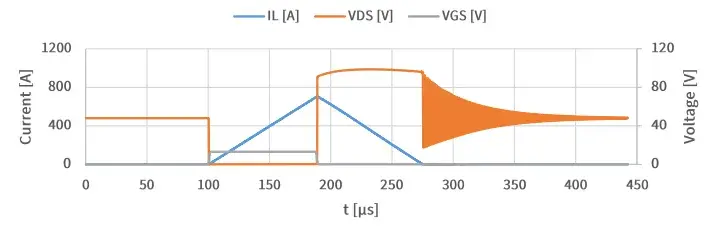

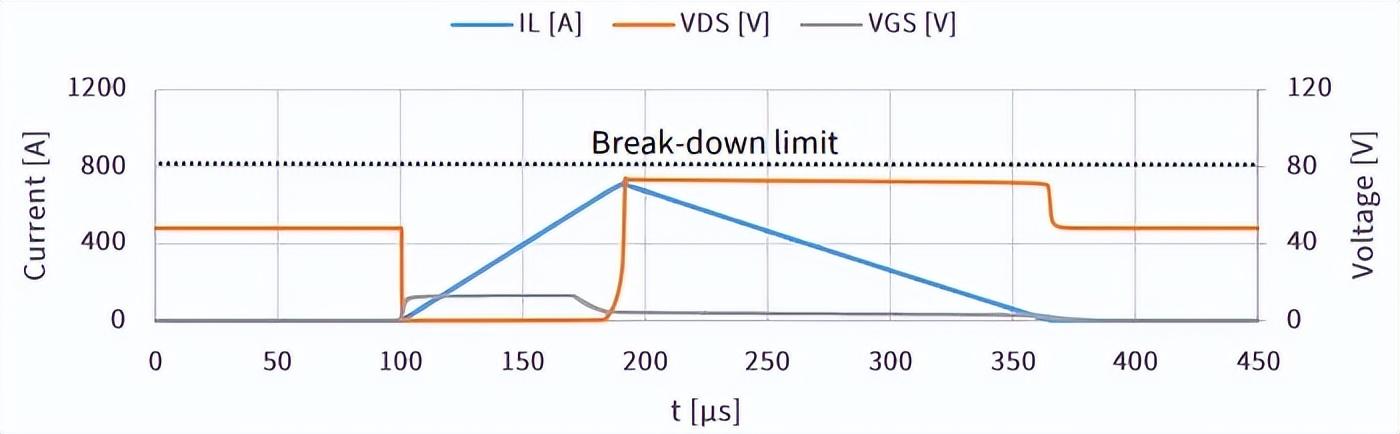

断开开关的一个显著挑战是保证短路时电路的鲁棒性。当检测到短路或者过流故障,MOSFET就会被关断以保护系统和MOSFET,避免失效。然而,存储在线缆电感中的能量依旧需要被消耗。如果没有额外的对抗措施,这些能量就会通过断开开关MOSFET的雪崩击穿来消耗。700A短路关断电流下的雪崩击穿仿真简化电路和仿真波形如图4、图5所示。为了避免栓锁效应引起的损坏和过热,需要使用雪崩电流和雪崩能量额定值大的MOSFET。如果超过MOSFET的电流或者能量额定值,额外的保护措施是必要的。

因为寿命周期内热载流子注入效应的影响,雪崩击穿一个需要面临的共同挑战是限制其暴露的时间。雪崩时,器件内部产生的强电场加速自由载流子会影响离子区。然而一些热载流子可能会注入到门极氧化物,从而导致参数漂移,限制器件寿命,进而限制雪崩击穿暴露的时间和雪崩击穿发生的次数。

图4 考虑寄生参数的简化48V断开开关短路方案

图5 短路关断后雪崩击穿仿真示例

有源钳位的使用使得这些能量可以用不同的方式被消耗。这需要器件工作在线性区而不是雪崩击穿,通过限制漏源极电压低于击穿电压,但高于电池电压来实现。在钳位期间,需要维持小的门极电压水平以保持沟道打开的状态,从而导通电流并限制漏源电压。

图6给出了有源钳位的仿真示意。可是让MOSFET工作在热不稳定区域会导致严重的问题。而且,让具有陡峭转移特性的器件并联工作在线性模式几乎是不可能的。因为制程导致的门极门槛电压的偏差,可能会让并联工作的MOSFET中的一颗承担几乎所有的电流。

图6 短路关断后有源钳位仿真示例

2. 双门极MOSFET介绍

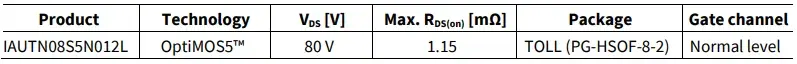

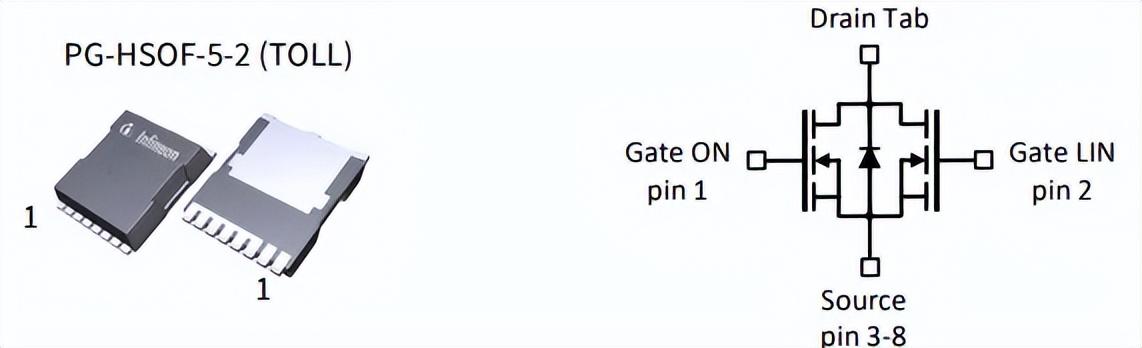

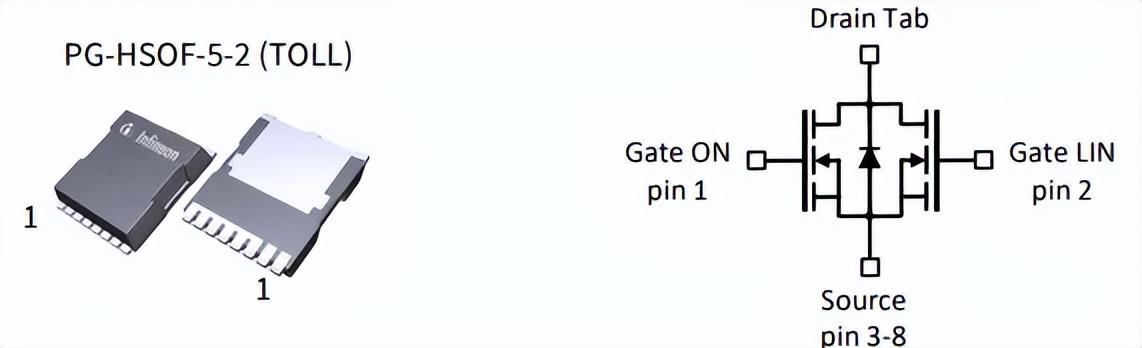

IAUTN08S5N012L双门极MOSFET就是以优化电容充电和短路的概念来设计的。这个创新的方式通过取消单独的预充电路实现降本。而且,该设计加强了系统的短路鲁棒性,为可靠且高效的性能应用需求提供了理想的选择。表2、图7分别给出了产品特性概览,封装和等效电气符号。

表2

图7 双门极MOSFET TOLL封装及其等效电路符号

2.1

2个MOSFET以双门极结构的方式长在同一封装

双门极MOSFET由2个并联交错的晶体管长在同一硅芯片组成,具有共同的漏极和源极,但是通过指定的引脚实现独立的门极。一个门极代表ONFET,稳态工作时实现低导通电阻;另一门极代表LINFET,提供优异的SOA和线性工作性能。这使得其适用于充电电容冲击电流的控制以及短路关断后的有源钳位。2个MOSFET共享一个芯片的好处在于可以互相利用硅的冷却区域或者热容。相比采用统一技术的单个标准MOSFET,当2个MOSFET都开通时,导通电阻只是略微提高。

2.2

LINFET强化SOA和跨导

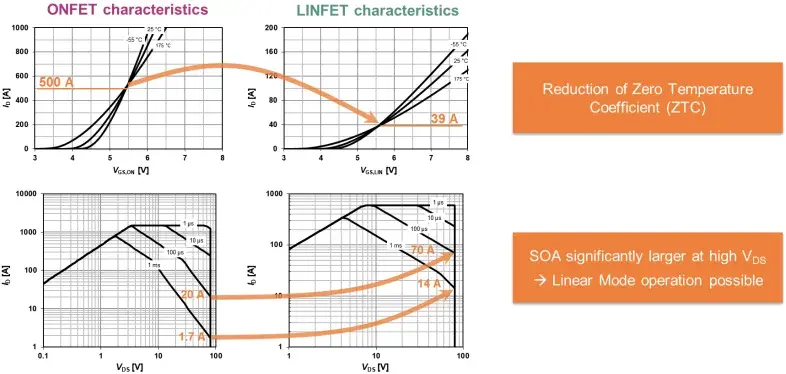

LINFET特意在工程上显著强化SOA性能,实现远超标准的沟槽工艺的MOSFET,可以媲美planar工艺的MOSFET。通过降低ZTC以及利用ONFET的芯片面积,使得LINFET具有优越的线性工作性能。图8以图形的形式展示了LINFET SOA性能的提升。比如,当器件处于高漏源电压和1ms的脉冲时间,相比ONFET,SOA电流提高了8倍。

图8 LINFET和ONFET性能比较——ZTC和SOA

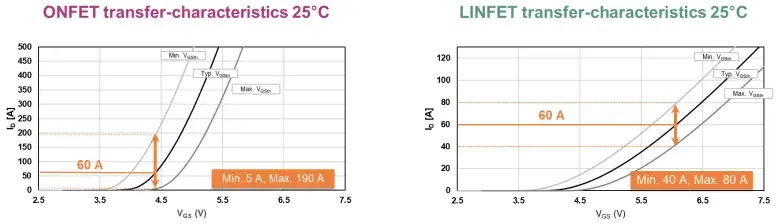

低跨导,即漏极电流对门极电压的变化率低,是LINFET的第2个关键优势。这带来了2个好处:一是实现基于外部门极电压容差的更加准确的电流控制,二是减小了门极电压偏差对电流的影响。此外,多个MOSFET由一个门极电压控制时,LINFET可以提高线性模式下的电流均流效果。图9展示了ONFET和LINFET的对比。出于简便,只考虑最小和最大门极门槛偏差对漏极电流的影响(忽略跨导工艺偏差)。以60A典型电流为例,对比最大和最小电流。可以发现,ONFET的电流范围是5A到90A,LINFET的电流范围是40A到80A。这就清晰的展示了低跨导的优势:打开了新的目标应用,比如短路钳位或者电容充电。低跨导帮助实现准确的控制冲击电流以及线性工作模式下多并联MOSFET的电流均流。

图9 ONFET和LINFET性能对比——跨导和电流容差

3. 如何利用双门极MOSFET解决

断开开关的应用挑战

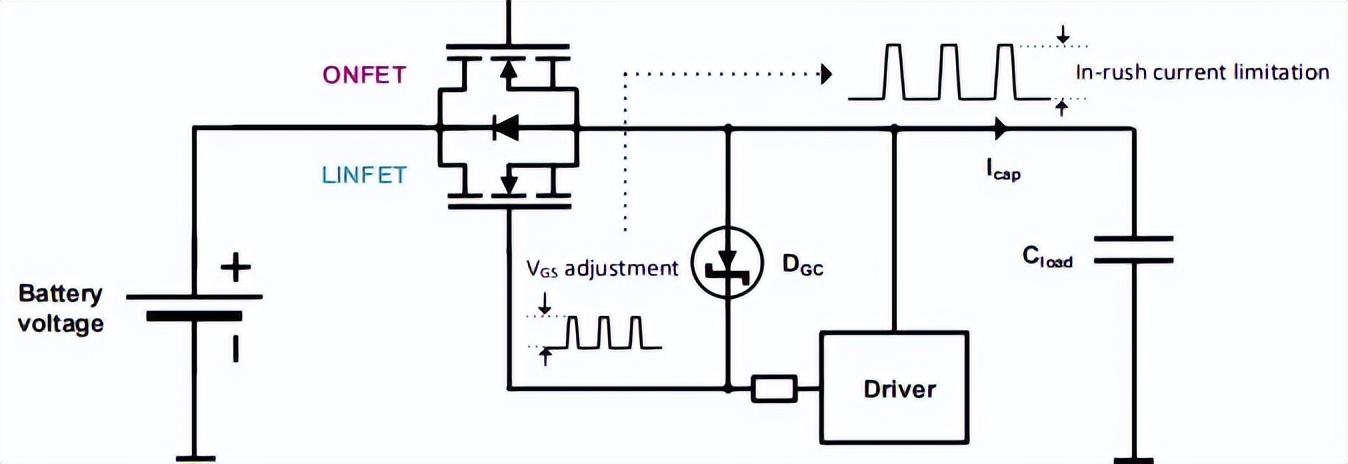

双门极MOSFET中的LINFET,因为提高的SOA和低跨导特性使其成为电容充电中限制冲击电流优秀候选方案。

3.1

固定门极电压限制电流

利用LINFET限制冲击电流的一个简单的方式是调节门极电压。目标电流限制取决于器件的转移和输出特性。然而这种方式依旧给因为工艺偏差和其他产品特性引起的变化留下空间。因此,评估考虑这些因素,找到好的充电速度和自发热的折中点显得尤为重要。

为了减小这种效应,规格书中规定了门极电压在5.6V到6.2V之间以及漏源电压在6V到48V之间等多种条件下的最大和最小电流限制精度。推荐5.6V的门极工作电压主要因为:一是5.6V非常接近器件的ZTC点,意味着电流独立于温度;二是5.6V的稳压管可以用来限制门极电压,而且其温度系数也很小。图10展示了带稳压管简化断开开关电路。稳压管的电压容差带来的电流变化可以基于规格书里LINFET的跨导来确定。比如门极电压为5.6V时,跨导dID/dVgs,LIN大约为50S。稳压管偏差+/-110mV会带来额外的大约+/-5.5A的电流偏差。

图10 带稳压管的门极电压控制实现冲击电流限制

3.2

脉冲式充电控制自发热

另一个需要考虑关键点是自发热。在大多数情况下,电容是非常大的,只是限制门极电压来开通LINFET是不足以有效的控制器件自发热。此外,因为每辆车启动时都需要进行电容充电,寿命的衰减也是重要的探索因素。自发热取决于如下3种因素:Zthja,ID以及VDS 。为了限制自发热和器件寿命的衰减,我们推荐考虑如下指导原则:

- 在高于或者接近ZTC点工作(Vgs,LIN >5V)以防工作在热不稳定区域

- 每一次脉冲充电引起的温升 ΔTj<60K

- 结温Tj <175oC

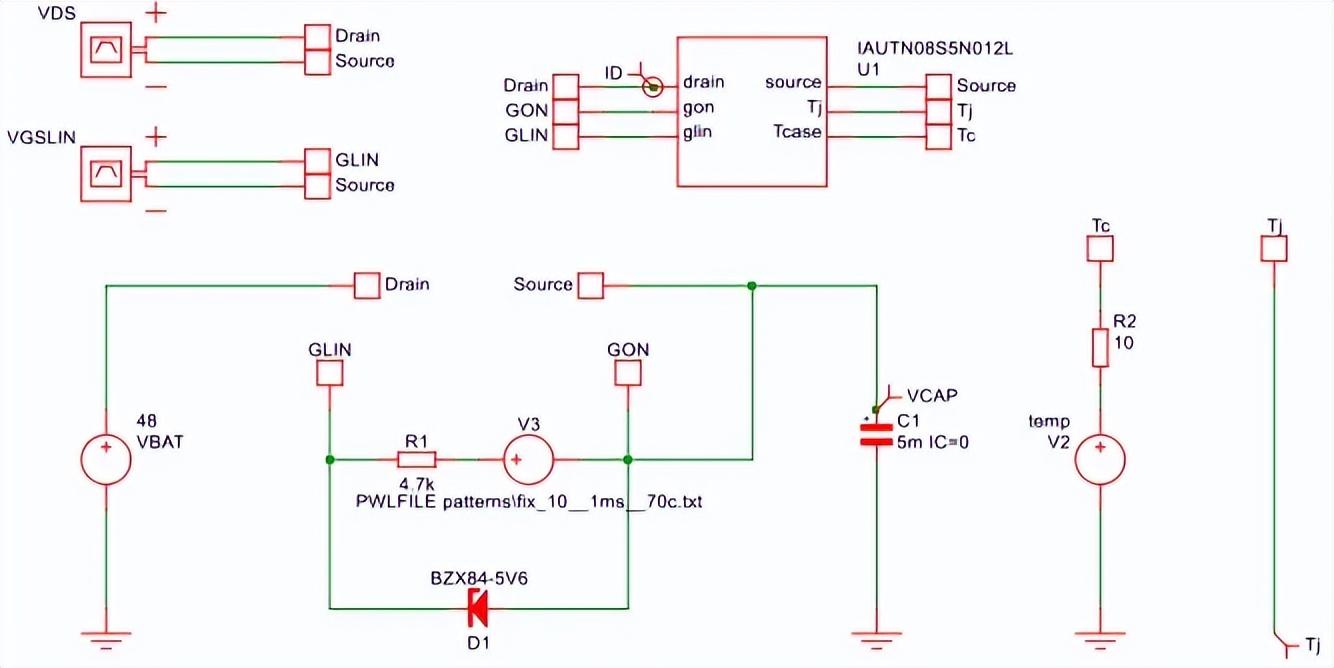

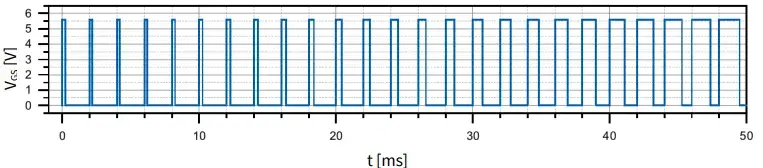

可以使用spice仿真来评估脉冲式电容充电时的自发热。如下图11和12给出了双门极MOSFET的简化仿真示例。如下的仿真例子里,5.6V的稳压管和4.7kohm的串联电阻被用来限制门极电压和电流。

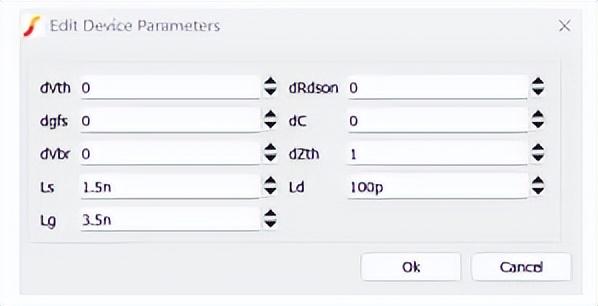

Spice模型参数设置(对接下来所有的仿真例子有效)

仿真条件:

- Ta=85C,VBAT=48V

- C1=5mF(负载电容)

- 脉冲宽度(固定):100us

- 周期:1ms

- 循环次数:70次

在保证每个充电脉冲的温升ΔTj <60K并且结温Tj保持在175oC以下时,典型的充电时间大约是60ms。

图11 双门极MOSFET充电电路仿真

@ 5mF, 48V(固定脉冲宽度)

图12 双门极MOSFET充电电路仿真波形

@ 5mF, 48V(固定脉冲宽度)

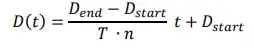

3.3

脉宽调节式电容充电

如上一节所讨论的,在电容充电器件,漏源电压、功率损耗随电容电压升高而减小。这种现象提供了充电过程中增加脉宽的机会,使我们能够最大化地利用每个周期的温升并且缩短总的充电时间。取决于充电时间、功率或者漏源电压,增加脉宽的方式有许多种,比如线性式,抛物线式、其他函数形式。如下2个例子给出的占空比函数D(t)表明了用固定充电模式的调节方式。

示例条件:

- n=25次(脉冲数量)

- T=2ms(周期)

- Dstart=10%(起始占空比)

- Dend=80%(结束占空比)

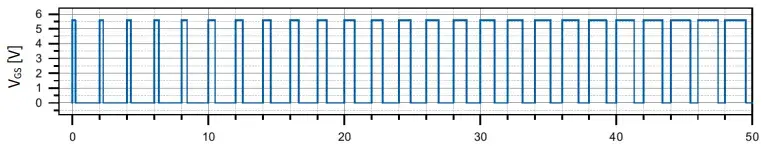

示例1:基于占空比函数D(t)的脉宽线性增加

图13 脉宽线性增加

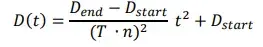

示例2:基于占空比函数D(t)的脉宽抛物线式增加

图14 脉宽抛物线式增加

3.4

降低开关速度减少板端网络电感耦合

如前述,在断开开关应用中,线束电感不仅对短路工况有严重的影响,而且也会影响电容充电的过程。在每个电容充电的电流脉冲期间,电流高上升和下降斜率dID/dt 会在线路电感上产生压降。可接受的dID/dt和电压耦合取决于系统的需要。欠压会导致连接到受影响端IC器件异常关断。同样的,过压也会使器件过电气应力出现损坏。因此,我们建议通过使用合适的RC参数以降低门极电压和漏极电流将dID/dt限制在合理的范围。这种方式简单高效。图15-图17 给出了仿真示例。

仿真条件:

- Ta=85C,VBAT=48V

- C1=5mF(负载电容)

- 脉冲宽度(固定):100us

- 周期:1ms

- 循环次数:70次

- 寄生电感L1:1uH

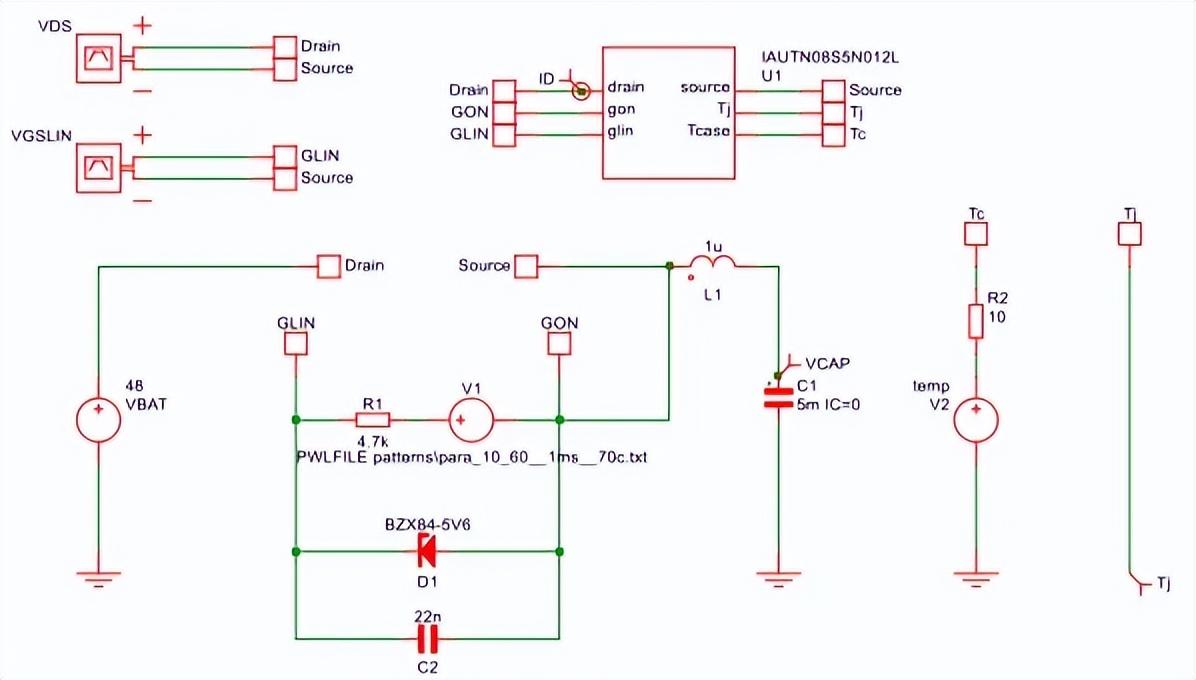

- 降低门极电压斜率开关电容C2 : 22nF

图15、图16分别是不加开关电容(虚线)和带开关电容的仿真波形。

图15 考虑电感耦合效应的双门极MOSFET仿真电路

@ 5Mf, 48V(抛物线式脉冲宽度调节)

图16 考虑1uH电感的双门极MOSFET仿真波形

@ 5mF, 48V(抛物线式脉冲宽度调节)

虚线代表不加开关电容C2

审核编辑 黄宇

-

英飞凌双栅极MOSFET 80V 48V开关板:技术解析与应用前景2025-12-19 97

-

NVBLS1D2N08X:一款高性能80V N沟道功率MOSFET的深度解析2025-11-24 244

-

80V耐压SL3048降压恒压 48V降12V/1A恒压电源芯片2025-05-30 1292

-

适用于48V电池断开开关的80V双门极MOSFET及其应用仿真详解2024-08-30 1876

-

降压恒压芯片 48V 60V 80V转3.3V 5V 惠海H6601直接替代5864、2459和14662024-02-20 4834

-

80V降压芯片、48V降压3.3V-5V电源芯片2023-08-04 3105

-

双电池系统中的互连汽车48V和12V电源轨2022-11-02 1292

-

Nexperia 适用于 36V 电池系统的特定应用 MOSFET2022-10-28 2502

-

48V转5V和转3.3V的电源芯片与LDO稳压IC方案介绍2020-11-12 3014

-

48V转5V,48V转3.3V,48V转3V的LDO和3A降压芯片2020-10-20 1954

-

80V耐压DC/DC转换器IC的定位与市场2018-12-05 2277

-

汽车48V电源或将成现实?2018-10-31 3115

-

ADI 6大产品解决方案,铺就48V/12V双电池汽车系统演进路线2018-10-30 2392

-

适用于48V汽车电池的汽车的参考设计TIDA-01344技术资料下载2018-07-13 1884

全部0条评论

快来发表一下你的评论吧 !