资料下载

×

高速缓冲存储器的分类及概述

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-10-17

15.3 高速缓冲存储器Cache

当第一代RISC微处理器刚出现时,标准存储器元件的速度比当时微处理器的速度快。很快,半导体工艺技术的进展被用来提高微处理器的速度。标准DRAM部件虽然也快了一些,但其发展的主要精力则放在提高存储容量上。

1980年,典型DRAM部件的容量为4KB。1981年和1982年开发出了16KB芯片。这些部件的随机访问速率为3MHz或4MHz,局部访问(页模式)时速率大约快1倍。当时的微处理器每秒需要访问存储器2M次。

到2000年,DRAM部件每片的容量到达256Mbit,随机访问速率在30MHz左右。微处理器每秒需要访问存储器几百兆次。如果处理器速率远高于存储器,那么只能借助Cache才能满足其全部性能。

Cache存储器是一个容量小但存取速度非常快的存储器,它保存最近用到的存储器数据拷贝。对于程序员来说,Cache是透明的。它自动决定保存哪些数据、覆盖哪些数据。现在Cache通常与处理器在同一芯片上实现。Cache能够发挥作用是因为程序具有局部性特性。所谓局部性就是指,在任何特定的时间,微处理器趋于对相同区域的数据(如堆栈)多次执行相同的指令(如循环)。

Cache经常与写缓存器(write buffer)一起使用。写缓存器是一个非常小的先进先出(FIFO)存储器,位于处理器核与主存之间。使用写缓存的目的是,将处理器核和Cache从较慢的主存写操作中解脱出来。当CPU向主存储器做写入操作时,它先将数据写入到写缓存区中,由于写缓存器的速度很高,这种写入操作的速度也将很高。写缓存区在CPU空闲时,以较低的速度将数据写入到主存储器中相应的位置。

通过引入Cache和写缓存区,存储系统的性能得到了很大的提高,但同时也带来了一些问题。比如,由于数据将存在于系统中的不同的物理位置,可能造成数据的不一致性;由于写缓存区的优化作用,可能有些写操作的执行顺序不是用户期望的顺序,从而造成操作错误。

15.3.1 Cache的分类

Cache有多种构造方法。在最高层次,微处理器可以采用下面两种组织中的一组。

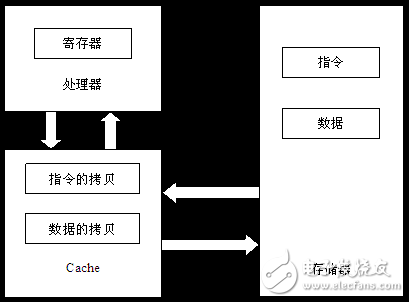

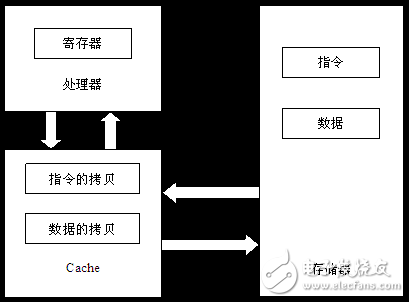

(1)统一Cache。指令和数据用同一个Cache。结构如图15.8所示。

图15.8 统一的指令Cache和数据Cache

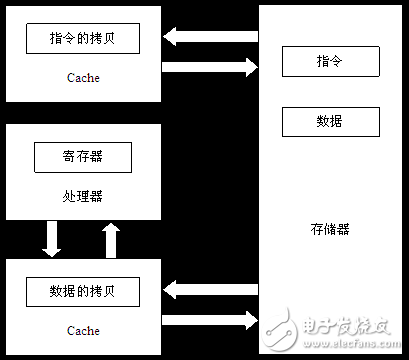

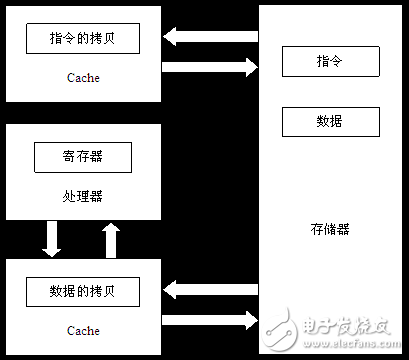

(2)指令和数据分开的Cache。有时这种组织方式也被称为改进的哈佛结构。

图15.9显示了这种组织方式。

这两种组织方式各有优缺点。统一Cache能够根据当前程序的需要自动调整指令在Cache存储器的比例,比固定划分的有更好的性能。另一方面,分开的Cache使Load/Store指令能够单周期执行。

15.3.2 Cache性能的衡量

只有当所需要的Cache存储器内容已经在Cache时,微处理器才能以高时钟速率工作。因此,系统的总体性能就可以用存储器访问中命中Cache的比例来衡量。当要访问的内容在Cache时称为命中(hit),而要访问的内容不在Cache时称为未命中(miss)。在给定时间间隔内,Cache命中的次数与总的存储器请求次数的比值被称为命中率。

图15.9 指令Cache和数据分开的Cache

命中率用下面的公式进行计算:

命中率=(Cache命中次数÷存储器请求次数)×100%

未命中率与命中率形式相似,即在给定时间间隔内,Cache未命中的总次数除以总的存储器请求次数所得的百分比。未命中率与命中率之和等于100。

目前设计良好的处理器,Cache的未命中率只有百分之几。未命中率依赖多个Cache参数,包括Cache大小和组织。

15.3.3 Cache工作原理

Cache的基本存储单元为Cache行(Cache line)。存储系统把Cache和主存储器都划分为相同大小的行。Cache与主存储器交换数据是以行为基本单位进行的。每一个Cache行都对应于主存中的一个存储块(memory block)。

Cache行的大小通常是2L字节。通常情况下是16字节(4个字)和32字节(8个字)。如果Cache行的大小为2L字节,那么对主存的访问通常是2L字节对齐的。所以对于一个虚拟地址来说,它的bit[31∶L]位,是Cache行的一个标识。当CPU发出的虚拟地址的bit[31∶L]和Cache中的某行bit[31∶L]相同,那么Cache中包含CPU要访问的数据,即成为一次Cache命中。

为了加快Cache访问的速度,又将多个Cache行划分成一个Cache组(Cache Set)。Cache组中包含的Cache行的个数通常也为2的N次方的倍数。为了方便起见,取N=S。这样,一个Cache组中就包含2S个Cache行。这时,虚拟地址中的bit[L+S-1∶L]为Cache组的标识。虚拟地址中余下的位bit[31∶L+S]成为一个Cache标(Cache-tag)。它标识了Cache行中的内容和主存间的对应关系。

当第一代RISC微处理器刚出现时,标准存储器元件的速度比当时微处理器的速度快。很快,半导体工艺技术的进展被用来提高微处理器的速度。标准DRAM部件虽然也快了一些,但其发展的主要精力则放在提高存储容量上。

1980年,典型DRAM部件的容量为4KB。1981年和1982年开发出了16KB芯片。这些部件的随机访问速率为3MHz或4MHz,局部访问(页模式)时速率大约快1倍。当时的微处理器每秒需要访问存储器2M次。

到2000年,DRAM部件每片的容量到达256Mbit,随机访问速率在30MHz左右。微处理器每秒需要访问存储器几百兆次。如果处理器速率远高于存储器,那么只能借助Cache才能满足其全部性能。

Cache存储器是一个容量小但存取速度非常快的存储器,它保存最近用到的存储器数据拷贝。对于程序员来说,Cache是透明的。它自动决定保存哪些数据、覆盖哪些数据。现在Cache通常与处理器在同一芯片上实现。Cache能够发挥作用是因为程序具有局部性特性。所谓局部性就是指,在任何特定的时间,微处理器趋于对相同区域的数据(如堆栈)多次执行相同的指令(如循环)。

Cache经常与写缓存器(write buffer)一起使用。写缓存器是一个非常小的先进先出(FIFO)存储器,位于处理器核与主存之间。使用写缓存的目的是,将处理器核和Cache从较慢的主存写操作中解脱出来。当CPU向主存储器做写入操作时,它先将数据写入到写缓存区中,由于写缓存器的速度很高,这种写入操作的速度也将很高。写缓存区在CPU空闲时,以较低的速度将数据写入到主存储器中相应的位置。

通过引入Cache和写缓存区,存储系统的性能得到了很大的提高,但同时也带来了一些问题。比如,由于数据将存在于系统中的不同的物理位置,可能造成数据的不一致性;由于写缓存区的优化作用,可能有些写操作的执行顺序不是用户期望的顺序,从而造成操作错误。

15.3.1 Cache的分类

Cache有多种构造方法。在最高层次,微处理器可以采用下面两种组织中的一组。

(1)统一Cache。指令和数据用同一个Cache。结构如图15.8所示。

图15.8 统一的指令Cache和数据Cache

(2)指令和数据分开的Cache。有时这种组织方式也被称为改进的哈佛结构。

图15.9显示了这种组织方式。

这两种组织方式各有优缺点。统一Cache能够根据当前程序的需要自动调整指令在Cache存储器的比例,比固定划分的有更好的性能。另一方面,分开的Cache使Load/Store指令能够单周期执行。

15.3.2 Cache性能的衡量

只有当所需要的Cache存储器内容已经在Cache时,微处理器才能以高时钟速率工作。因此,系统的总体性能就可以用存储器访问中命中Cache的比例来衡量。当要访问的内容在Cache时称为命中(hit),而要访问的内容不在Cache时称为未命中(miss)。在给定时间间隔内,Cache命中的次数与总的存储器请求次数的比值被称为命中率。

图15.9 指令Cache和数据分开的Cache

命中率用下面的公式进行计算:

命中率=(Cache命中次数÷存储器请求次数)×100%

未命中率与命中率形式相似,即在给定时间间隔内,Cache未命中的总次数除以总的存储器请求次数所得的百分比。未命中率与命中率之和等于100。

目前设计良好的处理器,Cache的未命中率只有百分之几。未命中率依赖多个Cache参数,包括Cache大小和组织。

15.3.3 Cache工作原理

Cache的基本存储单元为Cache行(Cache line)。存储系统把Cache和主存储器都划分为相同大小的行。Cache与主存储器交换数据是以行为基本单位进行的。每一个Cache行都对应于主存中的一个存储块(memory block)。

Cache行的大小通常是2L字节。通常情况下是16字节(4个字)和32字节(8个字)。如果Cache行的大小为2L字节,那么对主存的访问通常是2L字节对齐的。所以对于一个虚拟地址来说,它的bit[31∶L]位,是Cache行的一个标识。当CPU发出的虚拟地址的bit[31∶L]和Cache中的某行bit[31∶L]相同,那么Cache中包含CPU要访问的数据,即成为一次Cache命中。

为了加快Cache访问的速度,又将多个Cache行划分成一个Cache组(Cache Set)。Cache组中包含的Cache行的个数通常也为2的N次方的倍数。为了方便起见,取N=S。这样,一个Cache组中就包含2S个Cache行。这时,虚拟地址中的bit[L+S-1∶L]为Cache组的标识。虚拟地址中余下的位bit[31∶L+S]成为一个Cache标(Cache-tag)。它标识了Cache行中的内容和主存间的对应关系。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章