资料下载

总线的多DSP交叉调试器的设计与实现

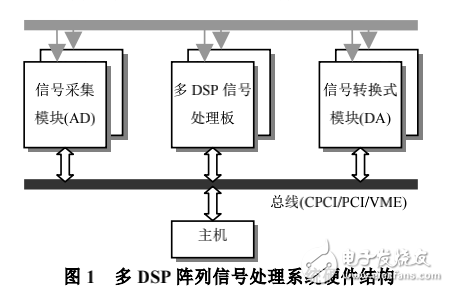

近年来随着 DSP 处理器技术的进步,越来越多的系统开

始倾向于采用多 DSP 并行处理的方式来构建系统的信号处理

模块。采用多 DSP 并行处理技术使系统具有很好的伸缩性和

灵活性[1]。由多处理器组成的阵列信号处理系统,使通信、

雷达、声纳进入数字化飞速发展的时代。

软件调试是多 DSP 系统开发过程中的重要一环,软件开

发周期和软件质量很大程度上依赖于开发人员所使用调试器

的性能及调试工具的完备程度[2]。因此,多 DSP 调试器的研

究对于多 DSP 系统的开发起着至关重要的作用。

通常,硬件仿真器是对 DSP 软件进行调试的主要工具。

目前大多数的 DSP 和其相应的硬件仿真器都使用 JTAG(Joint

Test Action Group)调试接口,即标准测试访问接口与边界扫

描结构。与 x86 等通用处理器系统中软件调试器得到广泛使

用的情况不同,用于 DSP 调试的软件调试器很稀少,这是因

为 DSP 处理器资源有限,交叉调试常用的 GDB 等调试器一

般无法在 DSP 上工作。虽然硬件仿真器不占用 DSP 的片内

资源,对 DSP 程序运行干扰很小,并且能够获取底层的硬件

信息,但是硬件仿真器也有许多缺点:

(1)JTAG 仿真器同时支持的 DSP 数量有限,调试多 DSP

并行的系统比较困难。JTAG 调试时将多个 DSP 串联成一个

JTAG 链,链上的 DSP 数量有限。

(2)调试的实时性不强。受 JTAG 硬件接口的限制,调试

速度比较慢。JTAG 接口采用串行方式传输数据,速率一般只

有每秒几十千位,当 JTAG 链上的设备较多时,通信带宽由

链上的 DSP 共享,通信速率严重下降。

(3)硬件仿真器成本较高。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章