资料下载

×

结合FPGA与DSPBuilder的VGA接口系统设计

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-10-25

VGA显像原理

显示器通过光栅扫描的方式,电子束在显示屏幕上有规律地从左到右、从上到下扫描。在扫描过程中,受行同步信号控制,逐点往右扫,完成一行扫描的时间倒数为行频;同时又在行同步脉冲期内回到屏幕的左端,从上往下形成一帧,在垂直方向上受场同步信号控制,完成一帧的时间倒数为场频。图像的显示过程即为在电子束扫描过程中,将地址与图像的像素依次对应,每一个被寻址的像素只获得其自身的控制信息,而与周围的像素不发生干扰,从而可以显示稳定的图像。

VGA接口是显示卡上输出模拟信号的接口,也叫D-Sub接口。这种接口上面共有15个针孔,分成3排,每排5个,通过模拟VGA接口显示图像的工作原理,将计算机内部以数字方式生成的显示图像信息,通过显卡中的ADC转变为R、G、B三基色信号和行、场同步信号,通过电缆传输到显示设备中。

VGA时序

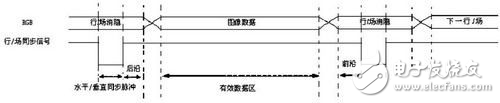

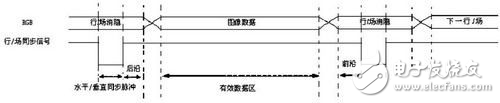

VGA的时序包括水平时序和垂直时序,且两者都包含的时序参数有:水平(垂直)同步脉冲、水平(垂直)同步脉冲结束到有效显示数据区开始之间的宽度(后沿)、有效显示区宽度、有效数据显示区结束到水平(垂直)同步脉冲宽度开始之间的宽度(前沿)。水平有效显示区宽度与垂直有效显示区宽度逻辑与的区域为可视区域,其他区域为消隐区。

一行或一场的时序信息如图1所示。

图1行/场时序图

根据目前的显示器性能参数,以LG505E为例,其最大分辨率已可达到@60Hz“》1024×768@60Hz,水平扫描频率30kHz”54kHz,垂直扫描频率50Hz“120Hz,带宽75MHz。

基于DSPBuilder的VGA接口设计方法

本设计需要完成的功能包括产生VGA时序以及基于VGA接口的信号显示。设计符合VGA接口标准的接口系统,在该系统下可显示一维矢量信号与二维图像信号,并体现系统的可集成性,将该接口集成到SOPC系统中。

系统时钟确定

根据系统时钟计算公式:

时钟频率=(行像素数+行消隐点数)×(一场行数+消隐行数)×刷新率。

对于标准的VGA接口时序@60Hz”》640×480@60Hz而言,时钟频率为800×525×60=25.175MHz。

在本设计中我们采用@60Hz“》1024×768@60Hz的XGA显示方式,因此系统的时钟频率PixelClk=1344×806×60=64.99MHz。

状态机设计

由VGA时序可设计有限状态机来完成时序信号,以本设计@60Hz”》1024×768@60Hz为例,对于行同步信号设计四个状态,即行同步脉冲信号区(horsync)、后沿区(backporch)、数据区(video)以及前沿区(frontporch)。用计数器hcnt的值来区分各阶段信号,最大记数值为1344。场同步信号也设计成如上四个状态,当完成一行的扫描后场计数器vcnt开始计数,因此一场可以有多行。

VGADAC芯片及相应信号的生成

一般的VGADAC芯片需要输入相应的驱动信号才能工作,包括时钟信号、同步信号、有效显示区信号等。系统所用DAC芯片为FMS3818,其信号包括时钟与数据信号(RGB)输入、控制信号输入(sync与blankn)以及RGB信号DA输出。行同步与场同步信号与经VGADAC产生的RGB数据信号一并输出到VGA接口,驱动CRT显示。在本设计中时钟信号65MHz、同步信号为horsync与versync相与产生,有效显示区信号为行与场的有效数据区信号相与产生。

一维矢量信号显示方式

在二维的空间中显示一维矢量信号,常规显示方法可以是将一维信号从左至右显示,如图2(a)所示,就如在普通的示波器上观察到的一样。这样,在VGA显示时,一行扫过多个采样点,需把要显示的采样点位置计算出来,当行信号扫过时,把采样点的值赋给像素点,就完成了信号的显示。而对于连续的一维信号,因为行频比场频高,图2(b)的显示方法更加合理。为此,将一维信号的时间轴映射到垂直方向上,幅值映射到水平方向上,当行扫描信号扫过一行时,映射一维信号的一个采样点,即一行信号对应一个像素,当完成一行信号后接着回扫,开始扫下一行。一般情况下,场频确定后,就可以根据一维信号的频率确定出一场可以显示的周期数,当完成一场信号后,在屏幕上就显示一帧图像。

显示器通过光栅扫描的方式,电子束在显示屏幕上有规律地从左到右、从上到下扫描。在扫描过程中,受行同步信号控制,逐点往右扫,完成一行扫描的时间倒数为行频;同时又在行同步脉冲期内回到屏幕的左端,从上往下形成一帧,在垂直方向上受场同步信号控制,完成一帧的时间倒数为场频。图像的显示过程即为在电子束扫描过程中,将地址与图像的像素依次对应,每一个被寻址的像素只获得其自身的控制信息,而与周围的像素不发生干扰,从而可以显示稳定的图像。

VGA接口是显示卡上输出模拟信号的接口,也叫D-Sub接口。这种接口上面共有15个针孔,分成3排,每排5个,通过模拟VGA接口显示图像的工作原理,将计算机内部以数字方式生成的显示图像信息,通过显卡中的ADC转变为R、G、B三基色信号和行、场同步信号,通过电缆传输到显示设备中。

VGA时序

VGA的时序包括水平时序和垂直时序,且两者都包含的时序参数有:水平(垂直)同步脉冲、水平(垂直)同步脉冲结束到有效显示数据区开始之间的宽度(后沿)、有效显示区宽度、有效数据显示区结束到水平(垂直)同步脉冲宽度开始之间的宽度(前沿)。水平有效显示区宽度与垂直有效显示区宽度逻辑与的区域为可视区域,其他区域为消隐区。

一行或一场的时序信息如图1所示。

图1行/场时序图

根据目前的显示器性能参数,以LG505E为例,其最大分辨率已可达到@60Hz“》1024×768@60Hz,水平扫描频率30kHz”54kHz,垂直扫描频率50Hz“120Hz,带宽75MHz。

基于DSPBuilder的VGA接口设计方法

本设计需要完成的功能包括产生VGA时序以及基于VGA接口的信号显示。设计符合VGA接口标准的接口系统,在该系统下可显示一维矢量信号与二维图像信号,并体现系统的可集成性,将该接口集成到SOPC系统中。

系统时钟确定

根据系统时钟计算公式:

时钟频率=(行像素数+行消隐点数)×(一场行数+消隐行数)×刷新率。

对于标准的VGA接口时序@60Hz”》640×480@60Hz而言,时钟频率为800×525×60=25.175MHz。

在本设计中我们采用@60Hz“》1024×768@60Hz的XGA显示方式,因此系统的时钟频率PixelClk=1344×806×60=64.99MHz。

状态机设计

由VGA时序可设计有限状态机来完成时序信号,以本设计@60Hz”》1024×768@60Hz为例,对于行同步信号设计四个状态,即行同步脉冲信号区(horsync)、后沿区(backporch)、数据区(video)以及前沿区(frontporch)。用计数器hcnt的值来区分各阶段信号,最大记数值为1344。场同步信号也设计成如上四个状态,当完成一行的扫描后场计数器vcnt开始计数,因此一场可以有多行。

VGADAC芯片及相应信号的生成

一般的VGADAC芯片需要输入相应的驱动信号才能工作,包括时钟信号、同步信号、有效显示区信号等。系统所用DAC芯片为FMS3818,其信号包括时钟与数据信号(RGB)输入、控制信号输入(sync与blankn)以及RGB信号DA输出。行同步与场同步信号与经VGADAC产生的RGB数据信号一并输出到VGA接口,驱动CRT显示。在本设计中时钟信号65MHz、同步信号为horsync与versync相与产生,有效显示区信号为行与场的有效数据区信号相与产生。

一维矢量信号显示方式

在二维的空间中显示一维矢量信号,常规显示方法可以是将一维信号从左至右显示,如图2(a)所示,就如在普通的示波器上观察到的一样。这样,在VGA显示时,一行扫过多个采样点,需把要显示的采样点位置计算出来,当行信号扫过时,把采样点的值赋给像素点,就完成了信号的显示。而对于连续的一维信号,因为行频比场频高,图2(b)的显示方法更加合理。为此,将一维信号的时间轴映射到垂直方向上,幅值映射到水平方向上,当行扫描信号扫过一行时,映射一维信号的一个采样点,即一行信号对应一个像素,当完成一行信号后接着回扫,开始扫下一行。一般情况下,场频确定后,就可以根据一维信号的频率确定出一场可以显示的周期数,当完成一场信号后,在屏幕上就显示一帧图像。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章