资料下载

高速pcb设计指南(史上最全设计资料)

此高速pcb设计指南可以说是史上最全设计资料,详细讲解了各项规则和技巧,值得细读。

如今,许多系统设计中最重要的因素就是速度问题。66MHz到200MHz处理器是很普通的;233-266MHz的处理器也变得轻易就可得到。对于高速度的要求主要来自: a) 要求系统在令用户感到舒适的、很短时间内就能完成复杂的任务。 b) 元件供应商有能力提供高度速的设备。

对a举例:即使产生最基本的计算机动画,也需要先计算大量的数据。目前,传播延迟4.5ns的可编程pld设备已经出现,像mach这样的传播延迟5ns的复杂plds也已经存在。尽管它们看起来已经很快了,但是,使发展有潜力的并不是这些传播延迟绝对值,而是传播延迟可能达到的边缘极值(edge rate)。将来会出现更快的设备,它们将具备更快的边缘极值。

设计高速系统并不仅仅需要高速元件,更需要天才和仔细的设计方案。设备模拟方面的重要性与数字方面是一样的。在高速系统中,噪声问题是一个最基本的考虑。高频会产生辐射进而产生干扰。边缘极值的速度可以产生振铃,反射以及串扰。如果不加抑制的话,这些噪声会严重损害系统的性能。

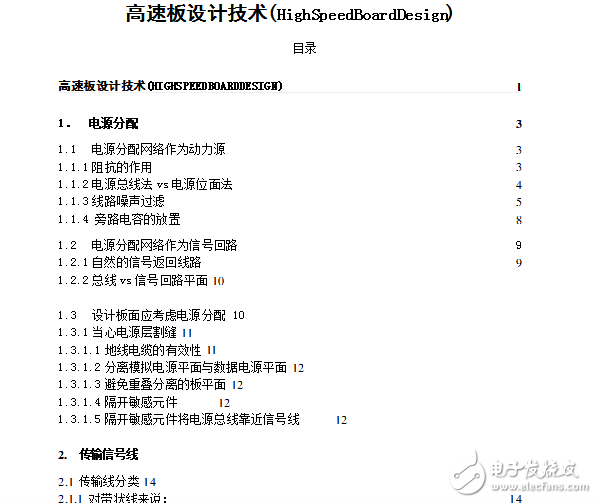

本文讲述了使用pcb-板设计高速系统的一般原则,包括:

电源分配系统及其对boardinghouse产生的影响

传输线极其相关设计准则

串扰(crosstalk)极其消除

电磁干扰

高速电路设计技术阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,并且得到最大功率输出的一种工作状态。高速PCB布线时,为了防止信号的反射,要求线路的阻抗为50Ω。这是个大约的数字,一般规定同轴电缆基带50Ω,频带75Ω,对绞线则为100Ω,只是取整数而已,为了匹配方便。 根据具体的电路分析采用并行AC端接,使用电阻和电容网络作为端接阻抗,端接电阻R要小于等于传输线阻抗Z0,电容C必须大于100pF,推荐使用0.1UF的多层陶瓷电容。电容有阻低频、通高频的作用,因此电阻R不是驱动源的直流负载,故这种端接方式无任何直流功耗。

串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生不期望的电压噪声干扰。耦合分为容性耦合和感性耦合,过大的串扰可能引起电路的误触发,导致系统无法正常工作。根据串扰的一些特性,可以归纳出几种减小串扰的方法:

1、加大线间距,减小平行长度,必要时采用jog 方式布线。

2、高速信号线在满足条件的情况下,加入端接匹配可以减小或消除反射,从而减小串扰。

3、对于微带传输线和带状传输线,将走线高度限制在高于地线平面范围要求以内,可以显著减小串扰。

4、在布线空间允许的条件下,在串扰较严重的两条线之间插入一条地线,可以起到隔离的作用,从而减小串扰。传统的PCB设计由于缺乏高速分析和仿真指导,信号的质量无法得到保证,而且大部分问题必须等到制版测试后才能发现。这大大降低了设计的效率,提高了成本,在激烈的市场竞争下显然是不利的。于是针对高速PCB设计,业界人士提出了一种新的设计思路,成为“自上而下”的设计方法,经过多方面的方针分析和优化,避免了绝大部分可能产生的问题,节省了大量的时间,确保满足工程预算,产生高质量的印制板,避免繁琐而高耗的测试检错等。利用差分线传输数字信号就是高速数字电路中控制破坏信号完整性因素的一项有效措施。在印制电路板(PCB抄板)上的差分线,等效于工作在准TEM模的差分的微波集成传输线对。其中,位于PCB顶层或底层的差分线等效于耦合微带线,位于多层PCB内层的差分线,等效于宽边耦合带状线。数字信号在差分线上传输时是奇模传输方式,即正负两路信号的相位差是180,而噪声以共模的方式在一对差分线上耦合出现,在接受器中正负两路的电压或电流相减,从而可以获得信号消除共模噪声。而差分线对的低压幅或电流驱动输出实现了高速集成低功耗的要求.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章