资料下载

×

设计灵活、高性能的嵌入式系统解析

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-11-07

您的下一个嵌入式系统设计项目需要的是什么:是可以让您轻松地定制设计的灵活的系统元件,还是额外的性能空间,以便您在设计周期中加入更多的功能?为什么要让自己承受过度的开发压力,并且只能舍此取彼呢?软处理和IP定制能够为同时确保灵活性和高性能提供了最佳的解决方案,将定制设计的概念和协处理带来的性能加速结合起来。

分立处理器只能提供固定的外设选择,并且一些性能受到时钟频率的限制。在嵌入式FPGA所提供的平台上,您可以创建一个具有大量定制处理器核、灵活的外设、甚至协处理减负引擎的系统。现在,您能设计出一个不折不扣的定制处理系统——不仅满足最具挑战性的项目要求,而且能够冲破性能极限,与此同时,通过使用FPGA硬件实现加速的软件指令最大限度地提高系统的性能。随着FPGA架构的加速,从前的限制便不复存在。

灵活性

除了在Xilinx® VirtexTM平台的FPGA中所提供的高性能PowerPCTM硬件处理核和使用汇编语言编程的占位空间更小的PicoBlazeTM微控制器外,Xilinx公司还提供一种可定制的通用32位RISC处理器。由于可以使用Virtex或SpartanTM系列产品中的任意一款在逻辑门外对其进行构建,因此MicroBlazeTM软件处理器的使用十分灵活,并且您能够通过定制处理IP外设来满足您的特定要求。

使用可定制核和IP,您只需创建所需的系统元件而不浪费任何芯片资源。当您使用像FPGA这样的可编程器件构建一个处理系统时,就不会在分立器件中浪费任何未使用的资源,也不会出现当需要的外设数量超过所提供的数量时(例如您的设计需要3个UART,而分立器件只能提供1个或2个),设计无法继续进行的情况。此外,您不会受限于初始的架构设想;相反,您能不停地进行大的修改并且能够调整系统架构来适应新的需求特性或不断变化的标准。

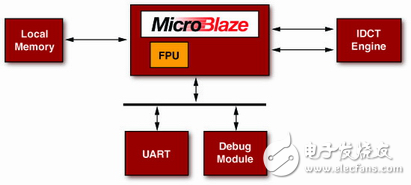

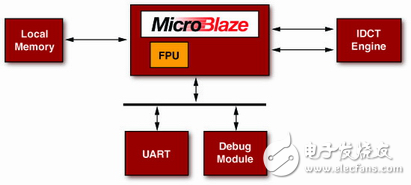

图1 - 简化的MicroBlaze框图

在“2006年嵌入式系统大会”的论文汇编中有一个FIR滤波器的设计示例,其中,MicroBlaze系统包含一个可选的符合IEEE 754标准的内部浮点单元(FPU),从而大大提高了该处理器核上仅可由软件执行的操作的性能。通过加入可选的MicroBlaze元件,可以迅速地提高应用程序的性能。

这些可选内部元件的另外一个优势就是它们得到MicroBlaze C编译器的全面支持,因此不必改变源代码。在这个FIR滤波器设计示例中,由于调用外部C代码库的浮点函数的操作被使用新的FPU的指令自动取代,因此加入FPU和对设计的重复编译意味着直接的性能提升。

与软件重新编码方法相比,使用专用硬件处理单元,能够将完成特定任务所需的时钟周期数减少几个数量级,从而提高处理器的性能。图1的简化图显示了一个带有内部FPU IP核、本地存储器核和像UART或JTAG调试端口这样的可选外设的MicroBlaze处理系统。由于系统是可定制的,我们可以方便地实现Xilinx处理器IP产品目录中所包含的多个UART或其他的IP外设核,其中包括DMA控制器、IIC、CAN或DDR存储器接口等。

该IP产品目录提供了门类齐全的其他处理IP(桥、仲裁器、中断控制器、GPIO、定时器和存储器控制器等),以及适用于每个IP核的可定制选项(例如波特率和奇偶校验位),以对元件的特性、性能和尺寸/成本进行优化。此外,您还能设置与处理核相关的时钟频率、调试模式、本地存储器容量、高速缓存和其它选项。仅仅增加一个FPU核,我们就能创建一个可将前文所提到的FIR的实现从8,500,000个CPU周期优化至177,000个CPU周期的MicroBlaze系统,这样,在不改变C代码源文件的情况下即可将性能提高48倍。

在第二个示例中,我们将构建另外一个设计模块,实现一个面向MP3解码器的IDCT引擎,这一设计可使应用模块的速度加快一个数量级。

您可以使用图2中所示的开发工具,方便地创建上文提到的两个处理器平台。这个集成式软件/硬件开发工具包括一块直接支持PowerPC和MicroBlaze处理器设计的Virtex-4参考板。开发工具还包括所有的编译器和所需的FPGA设计工具,以及IP目录和用作预校准的参考设计。

再加上JTAG探测器和系统电缆,此开发工具能够让您在开始编辑和调试自己的设计变更之前,轻松构建和运行一个工作系统。不同器件和板卡的开发工具,可从Xilinx公司及其分销商以及第三方嵌入式系统合作伙伴那里得到。

分立处理器只能提供固定的外设选择,并且一些性能受到时钟频率的限制。在嵌入式FPGA所提供的平台上,您可以创建一个具有大量定制处理器核、灵活的外设、甚至协处理减负引擎的系统。现在,您能设计出一个不折不扣的定制处理系统——不仅满足最具挑战性的项目要求,而且能够冲破性能极限,与此同时,通过使用FPGA硬件实现加速的软件指令最大限度地提高系统的性能。随着FPGA架构的加速,从前的限制便不复存在。

灵活性

除了在Xilinx® VirtexTM平台的FPGA中所提供的高性能PowerPCTM硬件处理核和使用汇编语言编程的占位空间更小的PicoBlazeTM微控制器外,Xilinx公司还提供一种可定制的通用32位RISC处理器。由于可以使用Virtex或SpartanTM系列产品中的任意一款在逻辑门外对其进行构建,因此MicroBlazeTM软件处理器的使用十分灵活,并且您能够通过定制处理IP外设来满足您的特定要求。

使用可定制核和IP,您只需创建所需的系统元件而不浪费任何芯片资源。当您使用像FPGA这样的可编程器件构建一个处理系统时,就不会在分立器件中浪费任何未使用的资源,也不会出现当需要的外设数量超过所提供的数量时(例如您的设计需要3个UART,而分立器件只能提供1个或2个),设计无法继续进行的情况。此外,您不会受限于初始的架构设想;相反,您能不停地进行大的修改并且能够调整系统架构来适应新的需求特性或不断变化的标准。

图1 - 简化的MicroBlaze框图

在“2006年嵌入式系统大会”的论文汇编中有一个FIR滤波器的设计示例,其中,MicroBlaze系统包含一个可选的符合IEEE 754标准的内部浮点单元(FPU),从而大大提高了该处理器核上仅可由软件执行的操作的性能。通过加入可选的MicroBlaze元件,可以迅速地提高应用程序的性能。

这些可选内部元件的另外一个优势就是它们得到MicroBlaze C编译器的全面支持,因此不必改变源代码。在这个FIR滤波器设计示例中,由于调用外部C代码库的浮点函数的操作被使用新的FPU的指令自动取代,因此加入FPU和对设计的重复编译意味着直接的性能提升。

与软件重新编码方法相比,使用专用硬件处理单元,能够将完成特定任务所需的时钟周期数减少几个数量级,从而提高处理器的性能。图1的简化图显示了一个带有内部FPU IP核、本地存储器核和像UART或JTAG调试端口这样的可选外设的MicroBlaze处理系统。由于系统是可定制的,我们可以方便地实现Xilinx处理器IP产品目录中所包含的多个UART或其他的IP外设核,其中包括DMA控制器、IIC、CAN或DDR存储器接口等。

该IP产品目录提供了门类齐全的其他处理IP(桥、仲裁器、中断控制器、GPIO、定时器和存储器控制器等),以及适用于每个IP核的可定制选项(例如波特率和奇偶校验位),以对元件的特性、性能和尺寸/成本进行优化。此外,您还能设置与处理核相关的时钟频率、调试模式、本地存储器容量、高速缓存和其它选项。仅仅增加一个FPU核,我们就能创建一个可将前文所提到的FIR的实现从8,500,000个CPU周期优化至177,000个CPU周期的MicroBlaze系统,这样,在不改变C代码源文件的情况下即可将性能提高48倍。

在第二个示例中,我们将构建另外一个设计模块,实现一个面向MP3解码器的IDCT引擎,这一设计可使应用模块的速度加快一个数量级。

您可以使用图2中所示的开发工具,方便地创建上文提到的两个处理器平台。这个集成式软件/硬件开发工具包括一块直接支持PowerPC和MicroBlaze处理器设计的Virtex-4参考板。开发工具还包括所有的编译器和所需的FPGA设计工具,以及IP目录和用作预校准的参考设计。

再加上JTAG探测器和系统电缆,此开发工具能够让您在开始编辑和调试自己的设计变更之前,轻松构建和运行一个工作系统。不同器件和板卡的开发工具,可从Xilinx公司及其分销商以及第三方嵌入式系统合作伙伴那里得到。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章