什么是锁相环_锁相环的作用及工作原理

模拟技术

描述

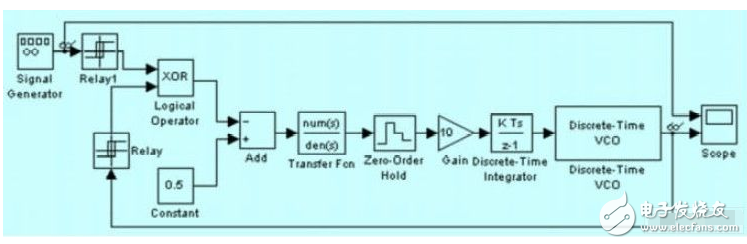

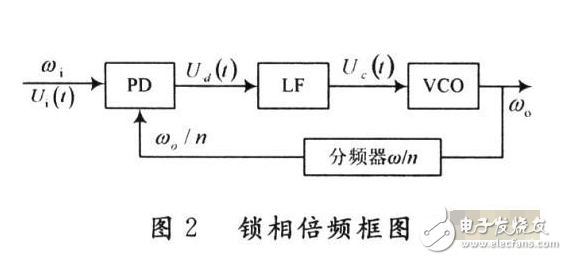

锁相环 (phase locked loop),顾名思义,就是锁定相位的环路。学过自动控制原理的人都知道,这是一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。是无线电发射中使频率较为稳定的一种方法,主要有VCO(压控振荡器)和PLL IC (锁相环集成电路),压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与PLL IC所产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则PLL IC的电压输出端的电压发生变化,去控制VCO,直到相位差恢复,达到锁相的目的。能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。

什么是锁相环

锁相环是指一种电路或者模块,它用于在通信的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。或者说,对于接收到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。由于锁定情形下(即完成捕捉后),该仿制的时钟信号相对于接收到的信号中的时钟信号具有一定的相差,所以很形象地称其为锁相器。

锁相环由鉴相器、环路滤波器和压控振荡器组成。鉴相器用来鉴别输入信号Ui与输出信号Uo之间的相位差,并输出误差电压Ud。Ud 中的噪声和干扰成分被低通性质的环路滤波器滤除,形成压控振荡器(VCO)的控制电压Uc。Uc作用于压控振荡器的结果是把它的输出振荡频率fo拉向环路输入信号频率fi ,当二者相等时,环路被锁定 ,称为入锁。维持锁定的直流控制电压由鉴相器提供,因此鉴相器的两个输入信号间留有一定的相位差。

PLL:phase Locked Loop 相同步回路,锁相回路,用来统一整合时脉讯号,使内存能正确的存取资料。

直接数字频率合成(DDS—Digital Direct Frequency Synthesis)技术是一种新的频率合成方法,是频率合成技术的一次革命,JOSEPH TIERNEY等3人于1971年提出了直接数字频率合成的思想,但由于受当时微电子技术和数字信号处理技术的限制,DDS技术没有受到足够重视,随着电子工程领域的实际需要以及数字集成电路和微电子技术的发展,DDS技术日益显露出它的优越性。

DDS是一种全数字化的频率合成器,由相位累加器、波形ROM、D/A转换器和低通滤波器构成。时钟频率给定后,输出信号的频率取决于频率控制器,频率分辨率取决于累加器位数,相位分辨率取决于ROM的地址线位数,幅度量化噪声取决于ROM的数据位字长和D/A转换器位数。

DDS有如下优点:

⑴ 频率分辨率高,输出频点多,可达N个频点(N为相位累加器位数);

⑵频率切换速度快,可达us量级;

⑶ 频率切换时相位连续;

⑷ 可以输出宽带正交信号;

⑸ 输出相位噪声低,对参考频率源的相位噪声有改善作用;

⑹可以产生任意波形;

⑺ 全数字化实现,便于集成,体积小,重量轻,因此八十年代以来各国都在研制和发展各自的DDS产品,如美国QUALCOMM公司的Q2334,Q2220;STANFORD公司的STEL-1175,STEL-1180;AD公司的AD7008,AD9850,AD9854等。这些DDS芯片的时钟频率从几十兆赫兹到几百兆赫兹不等,芯片从一般功能到集成有D/A转换器和正交调制器。

PLL:Phase Locked Logic 相同步逻辑

锁相环的用途是在收、发通信双方建立载波同步或位同步。因为它的工作过程是一个自动频率(相位)调整的闭合环路,所以叫环。锁相环分模拟锁相环和数字锁相环两种。

锁相环的作用

锁相环是为了得到频率相同的信号。

基带信号用高频载波发射后以后,在接受端需要乘以与载波同频率同相位的信号来解调。

由于发射端器件产生频率误差,即使知道载波频率为900MHz,接收端也不能直接用900MHz来解调。需要得到确切的载波频率就要用锁相环来产生同频率的信号。

这是模拟信号中的应用。

对于数字信号,有些传输方式是没有同步时钟的,需要从数据中恢复时钟,也会用到锁相环。

你说到消除频率误差用导线,应该实说模拟信号中的应用。问题是,直接用接收到的信号是无法自己给自己解调的。需要的是产生载频的正弦信号。误差也是针对载频来说的

锁相环的工作原理

压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与PLL IC所产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则PLL IC的电压输出端的电压发生变化,去控制VCO,直到相位差恢复!达到锁频的目的!能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。

模拟锁相环工作原理

模拟锁相环主要由相位参考提取电路、压控振荡器、相位比较器、控制电路等组成。压控振荡器输出的是与需要频率很接近的等幅信号,把它和由相位参考提取电路从信号中提取的参考信号同时送入相位比较器,用比较形成的误差通过控制电路使压控振荡器的频率向减小误差绝对值的方向连续变化,实现锁相,从而达到同步。

数字锁相环工作原理

数字锁相环主要由相位参考提取电路、晶体振荡器、分频器、相位比较器、脉冲补抹门等组成。分频器输出的信号频率与所需频率十分接近,把它和从信号中提取的相位参考信号同时送入相位比较器,比较结果示出本地频率高了时就通过补抹门抹掉一个输入分频器的脉冲,相当于本地振荡频率降低;相反,若示出本地频率低了时就在分频器输入端的两个输入脉冲间插入一个脉冲,相当于本地振荡频率上升,从而达到同步。

-

模拟锁相环应用实验2009-03-22 1065

-

锁相环原理2007-08-21 5204

-

锁相环电路2009-09-25 7248

-

锁相环(PLL),锁相环(PLL)是什么意思2010-03-23 6149

-

数字锁相环(DPLL),数字锁相环(DPLL)是什么?2010-03-23 5792

-

锁相环2011-10-26 17162

-

锁相环的基本组成及工作原理2020-11-03 15549

-

锁相环(PLL)的工作原理及应用2022-03-29 13943

-

锁相环的基本组成和工作原理2022-05-10 8058

-

模拟锁相环和数字锁相环区别2023-02-15 5319

-

关于锁相环(PLL)的工作原理2023-04-28 7433

-

什么是锁相环 锁相环的组成 锁相环选型原则有哪些呢?2023-08-01 5590

-

pll锁相环的作用 pll锁相环的三种配置模式2023-10-13 3684

-

锁相环的基本原理和主要作用2024-05-24 3852

全部0条评论

快来发表一下你的评论吧 !