资料下载

×

便携式设备中的电源效率解析

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-11-15

摘要

电源效率对于便携式设备以及模拟 IC 的噪声抗扰度来说都非常重要。本文主要介绍电压参考电路,其不仅支持极低的工作静态电流(低于 250nA),而且还符合标准 CMOS 工艺。这种电路针对各种应用进行了优化设计,适合便携式电子设备、汽车、医疗设备,以及高电源抑制比 (PSRR) 和开关噪声抗扰度都非常重要的片上系统 (SoC) 实施。

上述电压参考在低频率下支持 90dB。输出电压变化的标准偏差是 0.5%,在 –40°C 至 125°C 温度范围内的温度系数为 15ppm/°C。这些特性可在 1.6V 至 5.5V 的电源电压范围内实现。可实施各种用于为电压参考实现输入噪声抗扰度的方法。

介绍

几乎每款模拟电路都需要高精度高稳定参考电压或电流源。不过,在选择片上系统 (SoC) 技术时,参考电压模块不应成为限制因素。也就是说这类系统所选用的技术工艺对于参考电压源来说并不一定总是最理想的。因此,其设计应该更稳健,才能适应各种技术工艺的变化。

电池通常可作为 SoC 的电源。这就更需要提高工作在大电源电压范围内的电压参考源的线性稳压性能。要延长电池使用寿命,就需要低静态电源电流。同时,还需要在宽泛频率下实现高电源抑制比 (PSRR),以抑制来自高速数字电路、降压转换器或片上其它开关电路的噪声。本文主要介绍具有高 PSRR 的超低静态电流带隙电压参考。

基本带隙电压参考结构

改善 PSRR 的主题思想是在低压降稳压器 (LDO) 后面布置一个带隙电压源。现有线性稳压器拓扑在静态电流、DC 负载稳压、瞬态响应、去耦电容以及硅芯片面积要求方面存在很大差异。由于我们的目标是在没有外部电容器的情况下,在同一芯片上提供全面集成型 LDO,因而典型 LDO 结构并不适合。

这些结构与超低静态电源电流相矛盾。为了缓解这一矛盾,您可为 LDO 使用与参考源相同的带隙。不宜采用标准 LDO 结构的原因在于它需要输出电容器来实现稳定工作。最佳选项是带一个增益级的结构,其无需输出电容器便可实现稳定。

低压降稳压器

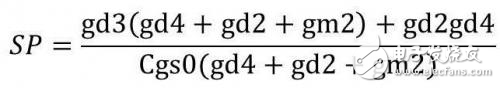

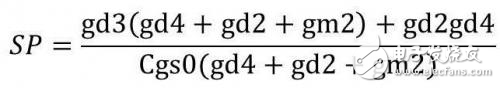

图 1 是该设计[1]中所使用 LDO 的内核及其简化原理图。图 1[2] 中的 M0 和 M4 代表翻转电压跟随器 (FVF),其可实施无逆向功能及相关极点的单级稳压。静态电流由晶体管 M1 和 M3 确定。晶体管 M2 可作为共栅放大器。

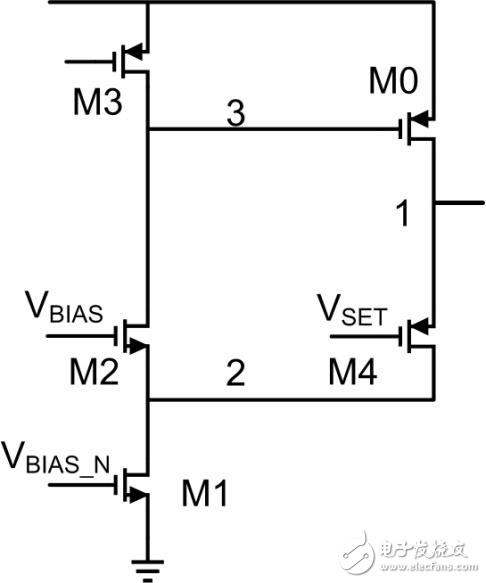

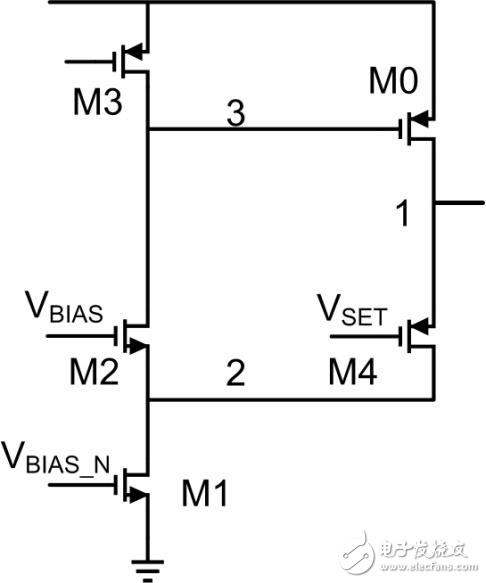

LDO 的开环增益由第一个级联级(即晶体管 M 2和 M3)决定。可作为负载的 M4 PMOS 跟随器存在低阻抗源,因此 FET M0 的输出增益接近 1。在图 2 中的小型信号等效电路的帮助下,对所推荐的 LDO 结构进行稳定性分析,结果显示只有一个极点(公式 1):

可作为补偿电容器的 M0 栅源电容器可创建 LDO 的主极点。因此无需去耦片外电容器,便可使 LDO[3] 稳定。

图 1.具有翻转电压跟随器、无输出电容器的 LDO

电源效率对于便携式设备以及模拟 IC 的噪声抗扰度来说都非常重要。本文主要介绍电压参考电路,其不仅支持极低的工作静态电流(低于 250nA),而且还符合标准 CMOS 工艺。这种电路针对各种应用进行了优化设计,适合便携式电子设备、汽车、医疗设备,以及高电源抑制比 (PSRR) 和开关噪声抗扰度都非常重要的片上系统 (SoC) 实施。

上述电压参考在低频率下支持 90dB。输出电压变化的标准偏差是 0.5%,在 –40°C 至 125°C 温度范围内的温度系数为 15ppm/°C。这些特性可在 1.6V 至 5.5V 的电源电压范围内实现。可实施各种用于为电压参考实现输入噪声抗扰度的方法。

介绍

几乎每款模拟电路都需要高精度高稳定参考电压或电流源。不过,在选择片上系统 (SoC) 技术时,参考电压模块不应成为限制因素。也就是说这类系统所选用的技术工艺对于参考电压源来说并不一定总是最理想的。因此,其设计应该更稳健,才能适应各种技术工艺的变化。

电池通常可作为 SoC 的电源。这就更需要提高工作在大电源电压范围内的电压参考源的线性稳压性能。要延长电池使用寿命,就需要低静态电源电流。同时,还需要在宽泛频率下实现高电源抑制比 (PSRR),以抑制来自高速数字电路、降压转换器或片上其它开关电路的噪声。本文主要介绍具有高 PSRR 的超低静态电流带隙电压参考。

基本带隙电压参考结构

改善 PSRR 的主题思想是在低压降稳压器 (LDO) 后面布置一个带隙电压源。现有线性稳压器拓扑在静态电流、DC 负载稳压、瞬态响应、去耦电容以及硅芯片面积要求方面存在很大差异。由于我们的目标是在没有外部电容器的情况下,在同一芯片上提供全面集成型 LDO,因而典型 LDO 结构并不适合。

这些结构与超低静态电源电流相矛盾。为了缓解这一矛盾,您可为 LDO 使用与参考源相同的带隙。不宜采用标准 LDO 结构的原因在于它需要输出电容器来实现稳定工作。最佳选项是带一个增益级的结构,其无需输出电容器便可实现稳定。

低压降稳压器

图 1 是该设计[1]中所使用 LDO 的内核及其简化原理图。图 1[2] 中的 M0 和 M4 代表翻转电压跟随器 (FVF),其可实施无逆向功能及相关极点的单级稳压。静态电流由晶体管 M1 和 M3 确定。晶体管 M2 可作为共栅放大器。

LDO 的开环增益由第一个级联级(即晶体管 M 2和 M3)决定。可作为负载的 M4 PMOS 跟随器存在低阻抗源,因此 FET M0 的输出增益接近 1。在图 2 中的小型信号等效电路的帮助下,对所推荐的 LDO 结构进行稳定性分析,结果显示只有一个极点(公式 1):

可作为补偿电容器的 M0 栅源电容器可创建 LDO 的主极点。因此无需去耦片外电容器,便可使 LDO[3] 稳定。

图 1.具有翻转电压跟随器、无输出电容器的 LDO

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章