资料下载

×

一种面向三维众核微处理器的新型NoC拓扑结构

消耗积分:3 |

格式:rar |

大小:0.92 MB |

2017-11-27

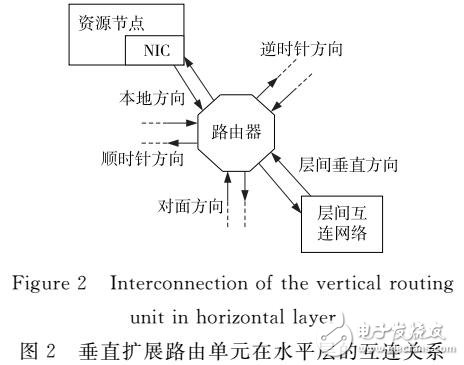

三维微处理器具有集成度高、全局互连线短及连接部件多的优势,但是传统的三维拓扑结构在大规模系统中无法充分利用垂直方向上低延时高带宽的特性,很难满足大规模众核微处理器低直径、高带宽、高扩展性的需求。针对三维NoC网络直径大、可扩展性要求高以及路由端口多的问题,提出了一种基于多级垂直域的三维拓扑结构 V-Spidergon,其在水平层上采用Spidergon结构,在垂直方向上采用多级垂直域扩展结构,域内及域间均实现全互连。实验数据表明,在8层、1 6层和32层堆叠下,V-Spidergon结构的延时较3DMesh分别降低15. 1%、28. 5%和55. 7%,较NoC-Bus分别降低11. 5%、32.7%和77.6%;在15%和100%负载率注入情形下,V-Spidergon的平均延时表现出与水平层数增加不相关的特性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章