资料下载

×

基于FPGA的DDS信号发生器设计方案解析

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-12-04

将虚拟仪器技术同FPGA技术结合,设计了一个频率可控的DDS任意波形信号发生器。在阐述直接数字频率合成技术的工作原理、电路构成的基础上,分别介绍了上位机虚拟仪器监控面板的功能和结构,以及实现DDS功能的下位机FPGA器件各模块化电路的作用。经过设计和电路测试,输出波形达到了技术要求,工作稳定可靠。

信号发生器是一种常用的信号源,广泛应用于通信、测量、科研等现代电子技术领域。信号发生器的核心技术是频率合成技术,主要方法有:直接模拟频率合成、锁相环频率合成(PLL)、直接数字合成技术(DDS)。DDS是开环系统,无反馈环节,输出响应速度快,频率稳定度高。因此直接数字频率合成技术是目前频率合成的主要技术之一。文中的主要内容是采用FPGA结合虚拟仪器技术,进行DDS信号发生器的开发。

1 DDS工作原理

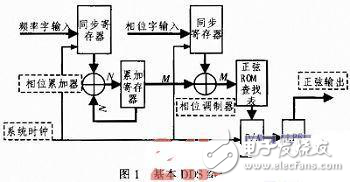

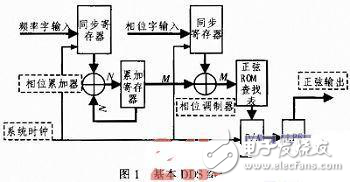

图1是DDS基本结构框图。以正弦波信号发生器为例,利用DDS技术可以根据要求产生不同频率的正弦波。

DDS电路主要由相位累加器、相位调制器、正弦ROM查找表、DAC和低通滤波器构成。其中,相位累加器是整个DDS的核心,完成相位累加的功能。下面对相位累加器的输入即相位增量进行分析。

对于正弦信号发生器,它的输出可以用下式来描述:Sout=Asinωt=Asin(2πfoutt) (1)

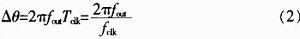

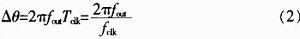

其中Sout是指该信号发生器的输出信号波形,fout指输出信号对应的频率。正弦信号的相位:θ=2πfoutt.在一个clk周期Tclk,相位θ的变化量为:

为了用数字化逻辑实现电路,必须对△θ进行数字量化,把2π切割成2N份,由此每个clk周期的相位增量△θ用量化值B△θ来表述:

其中θk-1指前一个clk周期的相位值。

由上面的推导可以看出,只要对相位的量化值进行简单的累加运算,就可以得到正弦信号的当前相位值,而用于累加的相位增量量化值B△θ(也叫频率控制字)决定了信号的输出频率fout,并呈现简单的线性关系。直接数字合成器DDS就是根据上述原理而设计的数字控制频率合成器。

信号发生器是一种常用的信号源,广泛应用于通信、测量、科研等现代电子技术领域。信号发生器的核心技术是频率合成技术,主要方法有:直接模拟频率合成、锁相环频率合成(PLL)、直接数字合成技术(DDS)。DDS是开环系统,无反馈环节,输出响应速度快,频率稳定度高。因此直接数字频率合成技术是目前频率合成的主要技术之一。文中的主要内容是采用FPGA结合虚拟仪器技术,进行DDS信号发生器的开发。

1 DDS工作原理

图1是DDS基本结构框图。以正弦波信号发生器为例,利用DDS技术可以根据要求产生不同频率的正弦波。

DDS电路主要由相位累加器、相位调制器、正弦ROM查找表、DAC和低通滤波器构成。其中,相位累加器是整个DDS的核心,完成相位累加的功能。下面对相位累加器的输入即相位增量进行分析。

对于正弦信号发生器,它的输出可以用下式来描述:Sout=Asinωt=Asin(2πfoutt) (1)

其中Sout是指该信号发生器的输出信号波形,fout指输出信号对应的频率。正弦信号的相位:θ=2πfoutt.在一个clk周期Tclk,相位θ的变化量为:

为了用数字化逻辑实现电路,必须对△θ进行数字量化,把2π切割成2N份,由此每个clk周期的相位增量△θ用量化值B△θ来表述:

其中θk-1指前一个clk周期的相位值。

由上面的推导可以看出,只要对相位的量化值进行简单的累加运算,就可以得到正弦信号的当前相位值,而用于累加的相位增量量化值B△θ(也叫频率控制字)决定了信号的输出频率fout,并呈现简单的线性关系。直接数字合成器DDS就是根据上述原理而设计的数字控制频率合成器。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(1)

发评论

-

雨雪加晴天

2018-04-23

0 回复 举报学习一下的说 收起回复

雨雪加晴天

2018-04-23

0 回复 举报学习一下的说 收起回复

- 相关下载

- 相关文章