浅谈英特尔在先进封装领域的探索

描述

以下文章来源于芯系半导体,作者向阳青年

随着工艺节点的进步,英特尔也在不断推进下一代封装技术的发展。对高性能硅需求与工艺节点开发相结合,创造了一种新的方案,即处理器不再是单片硅,而是依赖于多个较小(且可能优化过)的芯粒或芯片,通过一种有利于性能、功耗和最终产品的方式封装在一起。

单个大型芯片已不再是明智的商业决策——它们可能因为缺陷而太难制造,或者制造它们的技术未针对芯片上的任何一个特定功能进行优化。然而,将处理器分成独立的硅片会在这些片之间传输数据时产生额外的障碍——如果数据必须从硅片过渡到其他介质(如封装或中介层),那么就需要考虑功耗和延迟的成本。权衡的结果是,为特定目的优化的硅芯片,例如用逻辑工艺制造的逻辑芯片,用内存工艺制造的内存芯片,而且较小的芯片在分档时通常比较大的芯片具有更好的电压/频率特性。但支撑这一切的是芯片的组装方式,这就需要封装技术。

英特尔的两大主要专业封装技术是EMIB和Foveros。英特尔解释了这两者在其未来节点开发中的应用前景。

嵌入式多互连桥(EMIB)相比传统的硅中介层具有几个相当明显的优势。在需要的地方嵌入一小块硅片而不是使用大面积的中介层具有明显的成本优势。第一代EMIB产品已经在包括该公司高端Stratix X FPGA和Kaby Lake G移动芯片在内的多个产品中使用了一段时间。截至去年初,英特尔已经出货了超过一百万件基于EMIB的产品。尽管这些是超高端产品,因而其出货量并不如他们希望的那样高以摊销技术成本,但这足以改进该技术,并开始在更多产品中使用。与EMIB类似,Foveros通过将两个芯片直接面对面堆叠,显著增加了焊点密度,但这也带来了更高的成本。

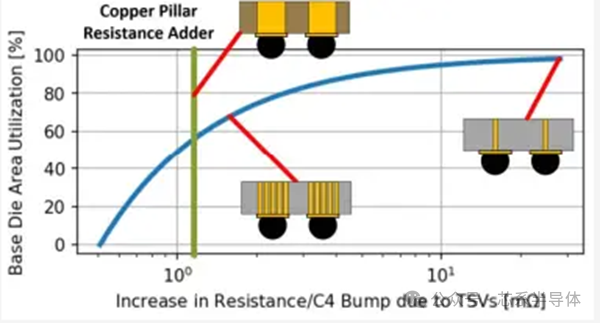

EMIB 和 Foveros 各有优劣,但它们都不完美。以Foveros 为例,它在顶层和底层芯片之间提供非常高的带宽。为了将电力传输到顶层芯片,需要通过底层芯片引入硅通孔(TSV)。TSV 会增加电阻,虽然可以通过增加更多的通孔来缓解,但这会占用额外的面积。此外,隔离区和固有拥塞问题会使情况更加恶化。根据英特尔的说法,保守估计芯片面积会增加约20%。在某些情况下,这个比例可能高达70%。然后是热管理问题。对于高性能应用,热量的散发是一个主要问题,因为顶层芯片阻碍了热量传递到散热器的路径,从而增加了热阻。传统的硅中介层可以通过将芯片分布在一大片硅片上来避免这个问题,从而实现更好的散热。同样,它也消除了逻辑芯片中使用 TSV 的需求,因此不会影响面积利用率。然而,较大的中介层会增加成本。此外,2.5D 解决方案失去了3D封装的优势。

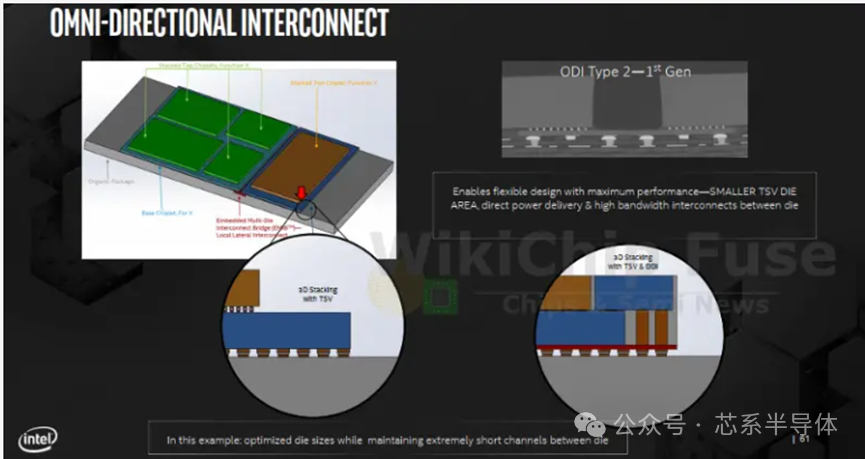

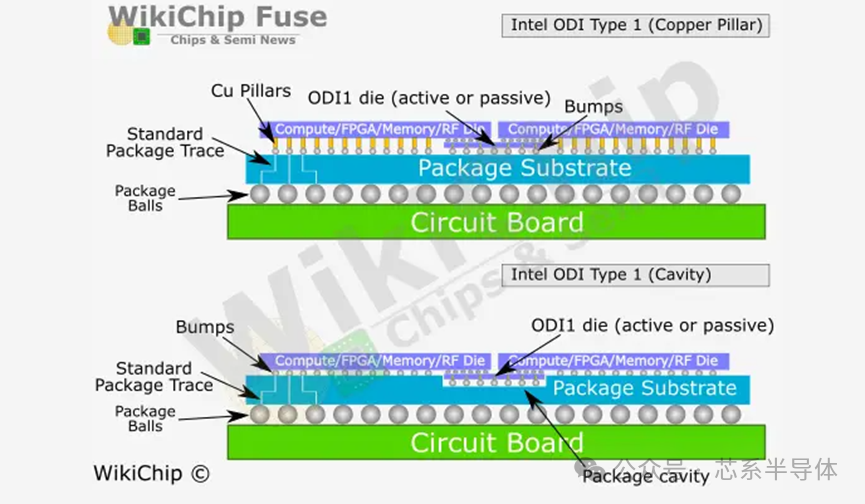

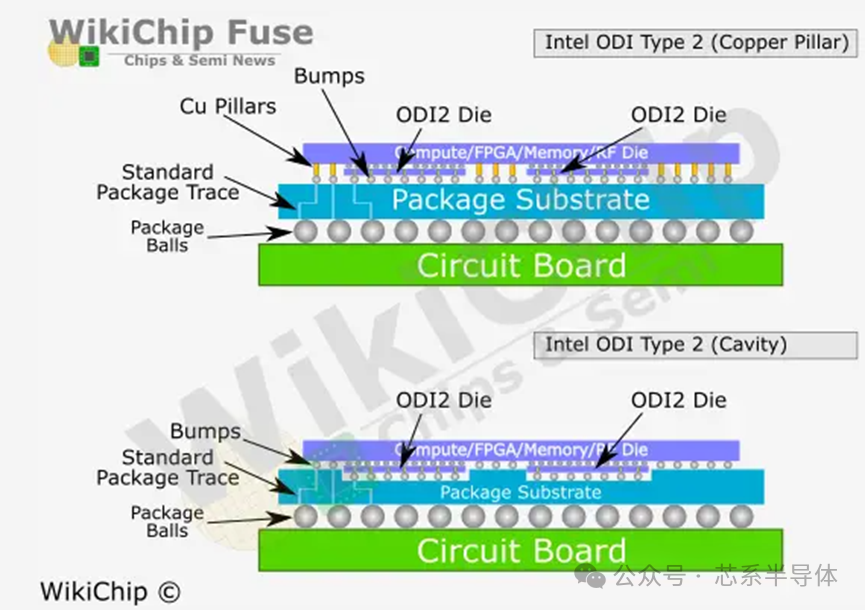

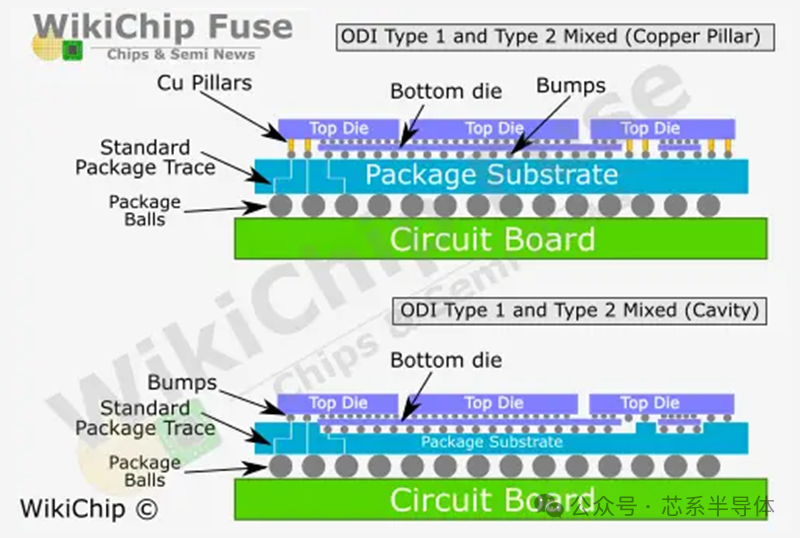

全向互连(ODI)是一新封装互连技术。ODI 通过多种3D封装流程,在功率传输和冷却能力方面相比于硅中介层等替代技术有显著提升,从而弥补了EMIB和Foveros之间的差距。ODI目前有四种变体。两种主要选项分别为“类型1”和“类型2”。每种类型都有两种风格——铜柱和空腔,所有四种变体可以根据需要组合在一起。同样,底部ODI芯片可以是有源芯片、无源芯片或两者的组合。

在ODI类型1中,底部芯片放置在两个顶层芯片的下方,或者放置在一个不能完全覆盖底部芯片的单个芯片下方。在ODI1中,底部芯片仅覆盖顶层芯片需要连接的部分,继承了Foveros类互连的优点,同时消除了TSV的缺点。ODI1可以是无源的,例如在芯片之间简单地进行路由,或者是有源的,例如在多个芯片之间主动路由数据或在多个芯片下方提供高度本地化的缓存。这种类型也可以用于单个芯片,例如在处理器与HBM或其他逻辑结合的情况下。

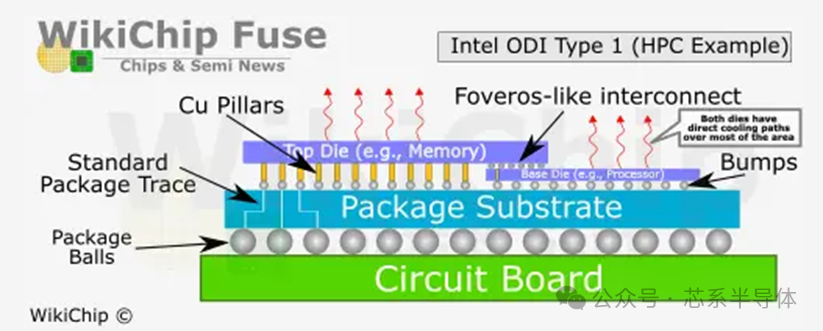

对于高性能应用而言,热量问题尤为重要,ODI1 提供了标准 2.5D 中介层所具备的额外优势,即直接访问冷却解决方案而无任何障碍。英特尔提供的一个示例是一个微处理器与堆叠内存的直接连接。ODI 避免了将两个芯片完全堆叠,从而使得两个芯片都可以直接接触冷却解决方案。同时,这个版本保留了类似 Foveros 的芯片间高带宽互连,消除了通过硅中介层的长通道的需求。

表面上看,1型版本可能与标准的EMIB非常相似,但实际上却有很大不同。在这一版本中,ODI芯片并未嵌入具有四周布线能力的硅中。相反,基础的ODI芯片是通过热压键合以受控高度放置在腔体内,然后使用热压键合(TCB)连接顶部芯片。通过独立控制底部芯片的高度,他们能够最大化C4工艺的效果。

在ODI类型2中,芯片完全位于顶层芯片下方。在这种情况下,底层芯片可以精确地定位在所需的位置,尽可能接近顶层芯片中所需逻辑的布线路径,就像使用底面电容(LSC)一样,以最大化它们的效率。ODI2可以用来增强顶层芯片的优势,比如增加额外的I/O功能或本地缓存。或者,它可以用来增加另一层主要功能,例如在处理器下方直接附加一个加速器。

混合搭配:ODI 的一个有趣特性是可以根据需要和实际情况自由混合搭配各种选项。例如,可以将基底做得更大,以包含多个顶部芯片,这种配置属于 Type 2 型配置,但边缘芯片可以采用 Type 1 型配置,使它们的电力通过铜柱进行传输。

英特尔推出了许多新的封装技术,涵盖了各种功能和能力。自首次披露EMIB以来,经过了数年的时间,Kaby Lake G等芯片才开始投产。然而,随着EMIB和Foveros技术的成熟,我们可能会看到新能力的进一步整合,超越ODI,并以更快速度进入生产阶段。

任何芯片间连接的一个问题就是连接本身。在目前提到的所有这些技术中,我们处理的是微凸点焊接连接——带有锡焊帽的小铜柱,这些铜柱被组合在一起并‘焊接’以创建连接。随着这些技术的不断发展,铜的生长和锡焊的沉积变得越来越困难,而且电子元件在不同金属间传输时也存在功率损耗的问题。Foveros Direct 通过直接铜对铜焊接解决了这个问题。

研究人员已经探索了若干年的直接硅对硅连接的概念,而不是依赖于柱和凸点的结合。如果一块硅片直接与另一块硅片对齐,那么几乎不需要额外的步骤来生长铜柱等。问题在于确保所有连接都能实现,确保上下两个芯片是如此平坦,以至于没有任何东西能阻碍连接。而且,这两块硅片必须融为一体,永久焊接在一起,无法分开。

Foveros Direct是一项技术,它帮助英特尔将芯片间连接的凸点间距缩小到10微米,相较于Foveros Omni密度提高了6倍。通过实现平坦的铜对铜连接,凸点密度得以增加,而全铜连接的使用意味着低阻连接,从而降低了功耗。英特尔表示,借助Direct,功能芯片的划分变得更加容易,功能模块可以根据需要拆分到多个层次上。

从技术上讲,Foveros Direct作为芯片间键合可以视为Foveros Omni的补充,后者将电源连接置于基底之外——两者可以独立使用。直接键合会使内部电源连接更容易,但可能仍会存在干扰问题,而Omni可以解决这一问题。需要注意的是,台积电也有类似的技术,称为Chip-on-Wafer(或Wafer-on-Wafer)。

-

测试芯片出炉 Altera/英特尔抢得14nm头筹2014-04-29 1716

-

#高通 #英特尔 #Elite 高通X Elite芯片或终结苹果、英特尔的芯片王朝深圳市浮思特科技有限公司 2023-10-27

-

英特尔转型移动领域难言乐观2012-11-07 3367

-

产业风暴,英特尔能否扳倒ARM?2016-09-26 4874

-

英特尔爱迪生闪存失败2018-11-02 5290

-

为什么选择加入英特尔?2019-07-25 5314

-

在移动领域,ARM在哪些方面领先英特尔2020-07-17 2991

-

英特尔重点发布oneAPI v1.0,异构编程器到底是什么2020-10-26 2113

-

英特尔封装技术路线2021-06-28 2828

-

英特尔开始加码封装领域2023-08-24 1005

-

英特尔先进封装全球布局 在马来西亚将有六座工厂2023-08-28 3640

-

2025年英特尔的先进芯片封装产能将扩大四倍2023-11-21 1604

-

英特尔携手日企加码先进封装技术2024-06-11 1021

-

详细解读英特尔的先进封装技术2025-01-03 2193

-

英特尔先进封装,新突破2025-06-04 1387

全部0条评论

快来发表一下你的评论吧 !