超结结构工艺实现方式

描述

以下文章来源于ICPMS冷知识 ,作者gz07apple

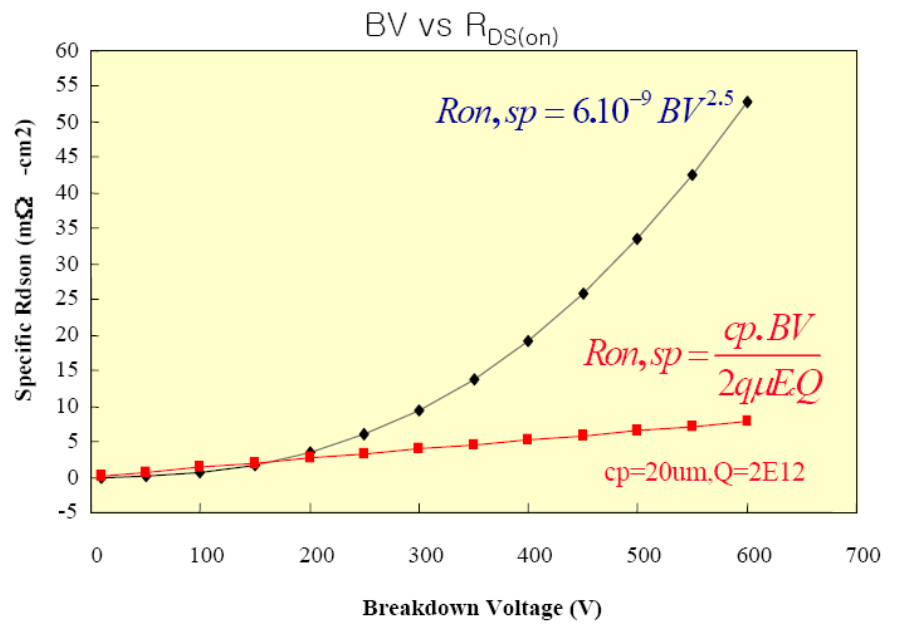

在过去的二十年,MOSFET主要用作开关器件,得到了长足的发展,由于它是多子器件,有相对较小的开关损耗,但其通态功耗较高,要降低通态功耗,导通电阻受击穿电压限制(导通电阻与击穿电压的2.5次方呈正比)无法再下降而存在一个极限,被称为“硅极限(Silicon Limit)”

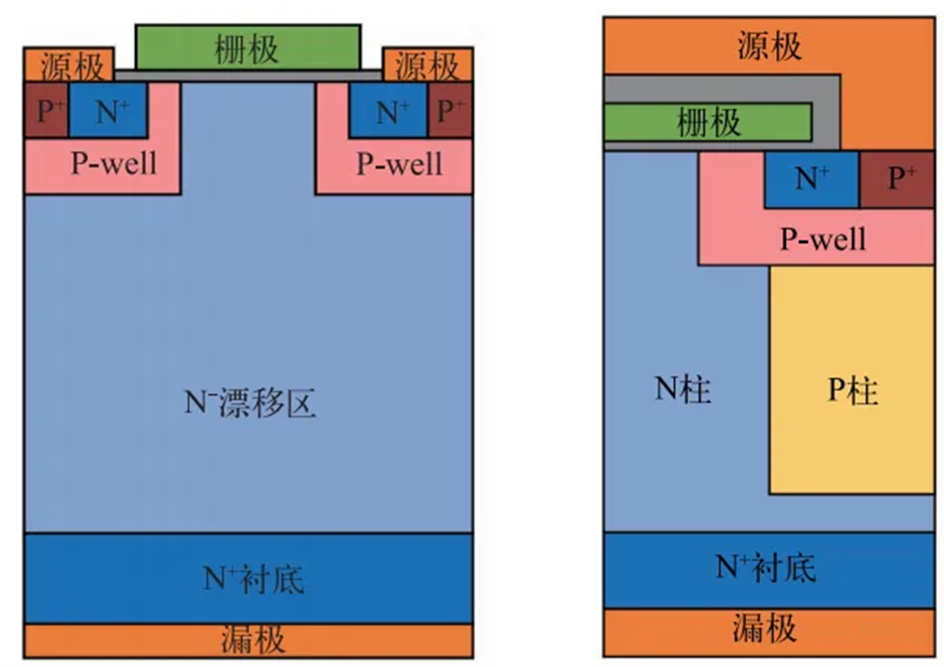

垂直双扩散金属氧化物半导体(VDMOS)是一种发展迅速、应用广泛的新型功率半导体器件。它在常规VDMOS基础上,引入超结(Superjunction)结构,使之既具有VDMOS输入阻抗高、开关速度快、工作频率高、电压控制、热稳定性好、驱动电路简单的特性,又克服了VDMOS的导通电阻随击穿电压急剧增大的缺点,提升了系统效率。目前超结VDMOS已广泛应用于电脑、手机、照明等消费电子领域、服务器电源、通讯电源等工业电子领域、以及充电桩、车载充电器等汽车电子领域。

在超结VDMOS中,耐压层由交替的高掺杂N柱和P柱构成(右侧图为超结),且N柱和P柱中的掺杂总量相等。在导通状态下,电流从源极经N柱流到漏极,P柱中不存在导电通道,而在阻断状态下,超结VDMOS的漂移区通过P柱的辅助耗尽作用在较低漏电压下就完全耗尽。

由于完全耗尽,P柱与N柱的等量异种电荷相互抵消而实现电荷平衡,电场在漂移区中近似于处处相等,因而击穿电压约等于临界电场与漂移区长度的乘积,这使得超结VDMOS的特征导通电阻与其击穿电压近似呈线性关系(1.32方甚至到1.03方),而不是传统器件的2.5方关系,进而可以减小导通电阻。

目前超结结构主要有两种工艺实现方式:多次外延工艺和深槽刻蚀加掺杂。

(一)多次外延工艺

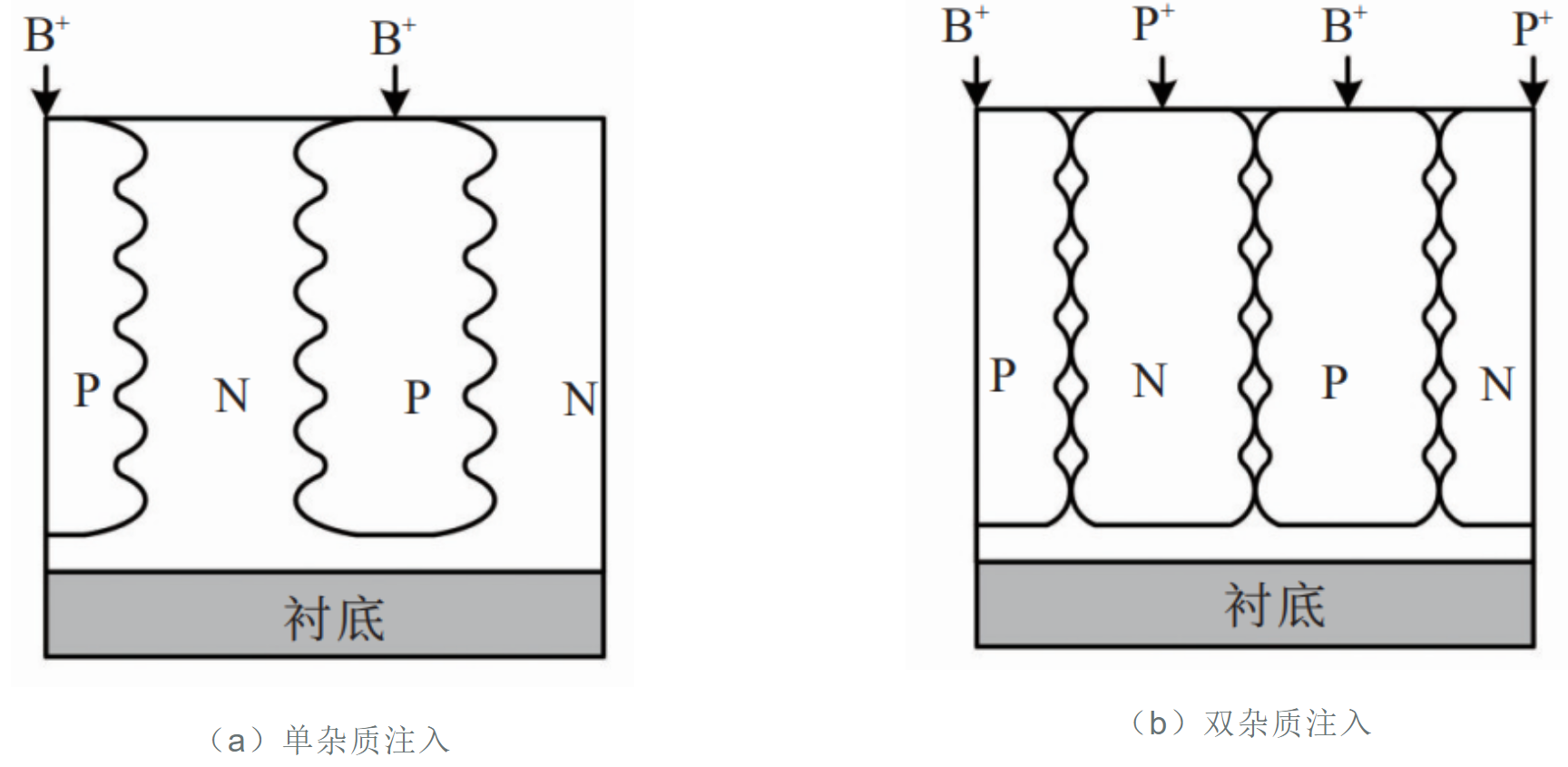

该工艺是在N型衬底上采用多次外延方式生长很厚的漂移区,每一次外延工艺均伴随一次P型离子注入,随后推结形成连续的P柱。制作一个约40μm深的P柱,一般需要进行5到6次外延生长和离子注入。

多次外延工艺

注意刚刚提到的方法是,通过多次外延一定浓度的N型区,然后仅仅采用单杂质(P型)注入补偿形成P柱。多次外延工艺实际上还有第二种方法(双杂质注入),是每次外延浓度较低,然后同时引入N和P型注入,分别形成超结的N柱和P柱,第二种工艺可以控制更好的均匀性,但工艺上需增加一次光刻与离子注入。

此类工艺的优点是形成超结耐压层的晶格质量较好,缺陷与界面态少。然而为形成较好超结形貌,每次外延层厚度相对固定且较薄,外延次数将随着器件耐压增大而增多,导致成本增加。

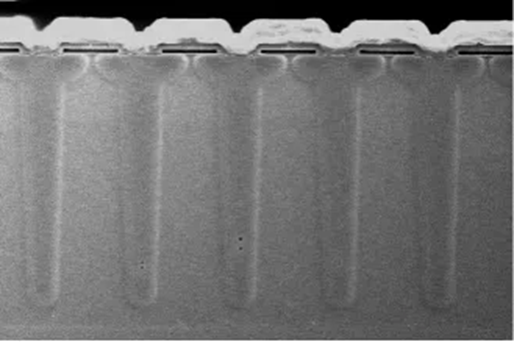

(二)深槽刻蚀加掺杂

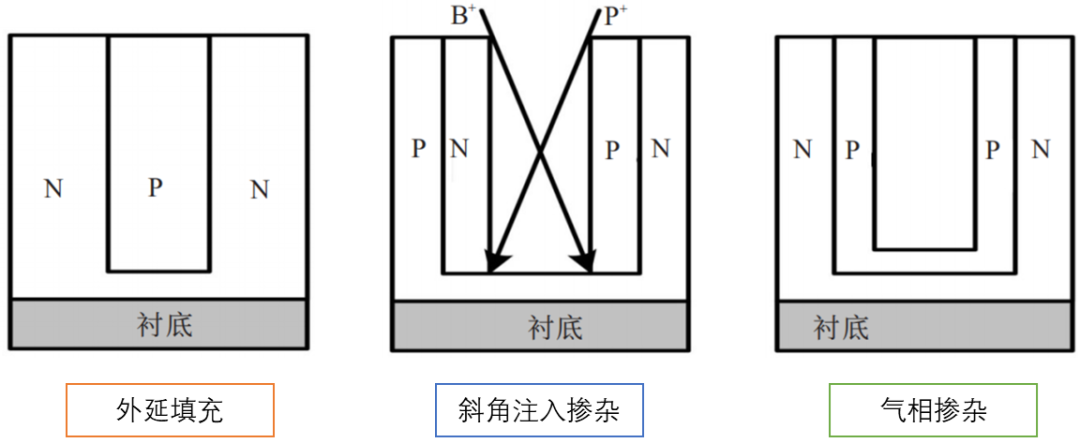

该工艺是在外延层上刻蚀出深沟槽,然后再对槽做内部掺杂。掺杂的方式通常分为三种:

第一种方式是外延填充。在槽内外延填充P型硅,然后采用化学机械抛光(CMP)实现平坦化;当然也可以先在槽壁上形成薄氧化层结构,再进行多晶硅填充形成P柱。

第二种方式是斜角注入掺杂。采用倾斜注入方式分别在槽壁上形成N柱和P柱,这样可以通过控制N和P型杂质的注入剂量来实现电荷平衡。

第三种方式是气相掺杂,通过对槽壁进行气相掺杂形成P柱。

深槽外延工艺

采用深槽刻蚀加外延填充工艺实现的超结耐压区,较多次外延工艺更易实现较小的深宽比,同时形成的超结区掺杂分布也较均匀,有利于降低导通电阻。

-

东芝推出采用超级结结构的600V N沟道功率MOSFET,助力提高电源效率2023-06-13 1430

-

研究生毕业继续送资料——超经典复旦大学微电子工艺教案2011-12-15 41499

-

多核DSP与超核DSP的基本结构讨论2019-06-26 1277

-

LTCC多层滤波器的工艺怎么实现?2021-04-12 1697

-

MCU总结结构和程序运行机制的相关资料分享2021-11-16 1356

-

OPPO RenoTP超窄边框点胶工艺揭秘2019-05-01 10899

-

东芝拓展650V超结结构N沟道功率MOSFET新品 景嘉微发布JH9202022-03-18 6128

-

FPGA的基本结构、数据存储及配置方式2022-11-29 5906

-

功率MOSFET基本结构:超结结构2023-11-04 7205

全部0条评论

快来发表一下你的评论吧 !