基于FPGA的JPEG-LS图像压缩器介绍

描述

在之前的推文里面也给大家介绍了JPEGLS算法的一些内容,可以点击下方链接查看JPEGLS算法简介

现在来看一下GitHub上面一个开源的JPEG LS算法的Verilog实现

开源地址:https://github.com/WangXuan95/FPGA-JPEG-LS-encoder

项目介绍

基于 FPGA 的流式的 JPEG-LS 图像压缩器,特点是:

纯 Verilog 设计,可在各种FPGA型号上部署

用于压缩 8bit 的灰度图像。

可选无损模式,即 NEAR=0 。

可选有损模式,NEAR=1~7 可调。

图像宽度取值范围为 [5,16384],高度取值范围为 [1,16384]。

极简流式输入输出。

使用方法

RTL 目录中的 jls_encoder.v 是用户可以调用的 JPEG-LS 压缩模块,它输入图像原始像素,输出 JPEG-LS 压缩流。

模块参数

jls_encoder 只有一个参数:决定了 NEAR 值,取值为 3'd0 时,工作在无损模式;取值为 3'd1~3'd7 时,工作在有损模式。

parameter [2:0] NEAR

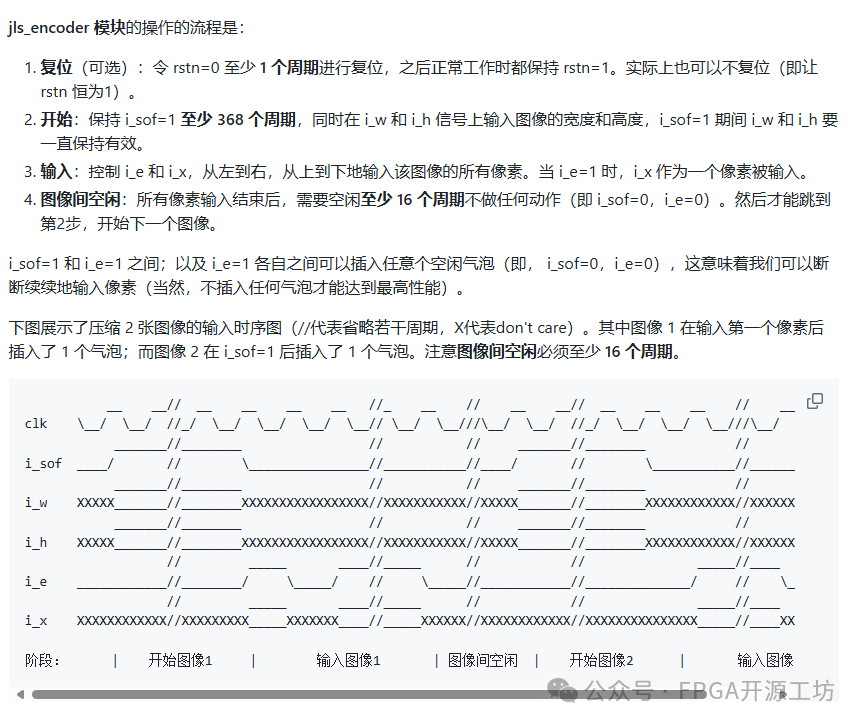

流程

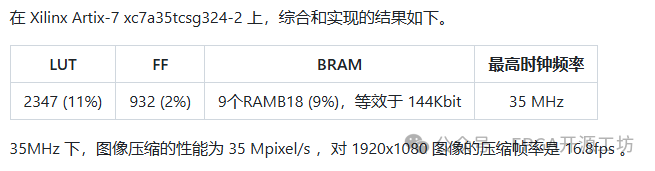

资源消耗

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

基于DSP的JPEG图像压缩设计2011-10-28 3583

-

基于JPEG标准的静态图像压缩算法研究2010-04-24 2040

-

压缩文件可以使用pdf压缩器吗2016-10-27 2614

-

如何使用pdf压缩器把文件进行压缩2016-11-02 2631

-

基于DSP的图像采集及JPEG-LS压缩系统2010-02-24 640

-

音频压缩器2009-09-08 2692

-

JPEG、MJPEG 图像压缩2010-01-07 3075

-

基于FPGA的静止图像压缩系统的研究2011-11-01 873

-

基于FPGA的JPEG实时图像编解码系统2016-08-29 725

-

DSP的图像采集及JPEG_LS压缩系统2017-10-19 1078

-

达芬奇技术的JPEG2000图像压缩系统设计2017-10-26 1176

-

图像压缩加密算法2018-01-19 1016

-

基于DSP的JPEG图像压缩的设计与实现2018-12-17 1056

-

JPEG 2000图像压缩的优势介绍2019-04-03 7256

-

如何使用FPGA实现机载图像无损和近无损压缩方案2021-02-03 1124

全部0条评论

快来发表一下你的评论吧 !